tft, tft array substrate, manufacturing method thereof, display panel, display device

An array substrate and substrate technology, which is applied to display panels and display devices, TFT, TFT array substrates and their manufacturing fields, can solve the problems of large parasitic capacitance, susceptibility to damage of semiconductor active layers, increased risk of discharge breakdown, and the like, Achieve the effect of reducing parasitic capacitance and avoiding the risk of discharge breakdown

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

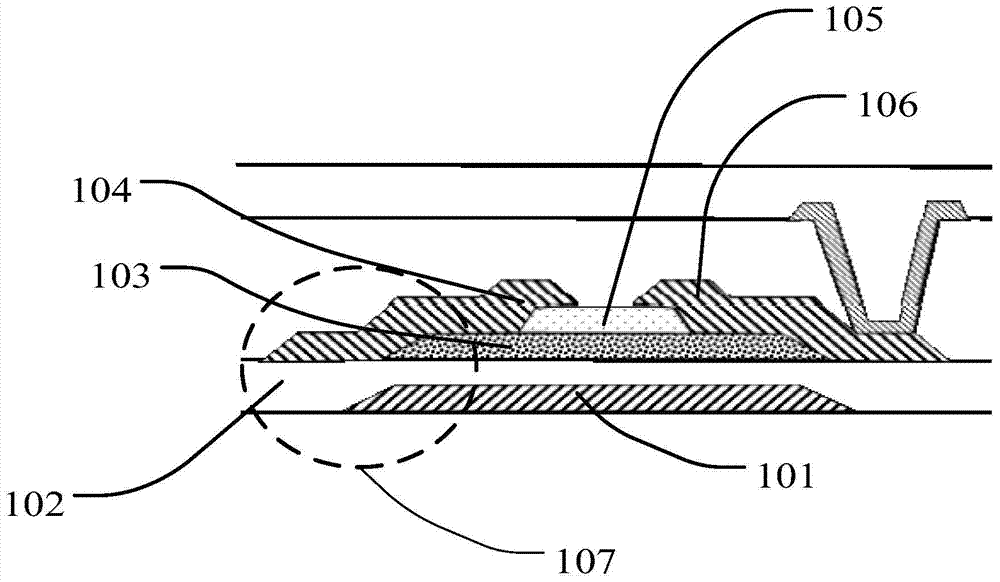

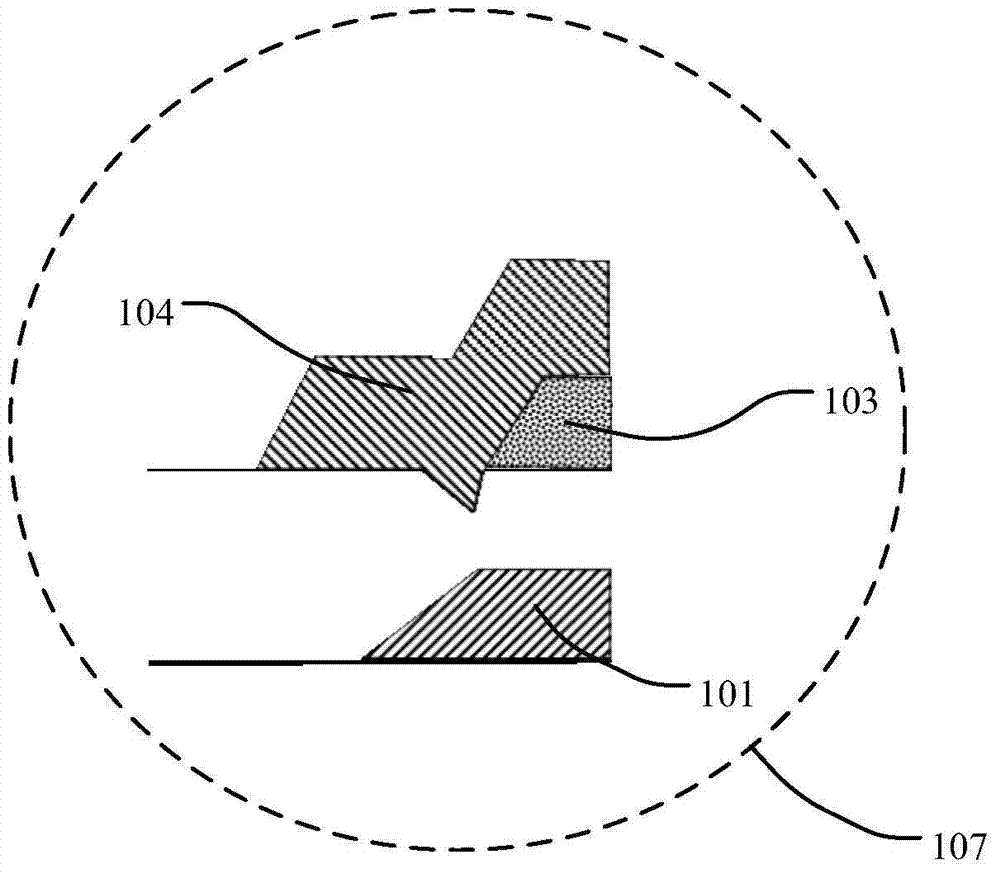

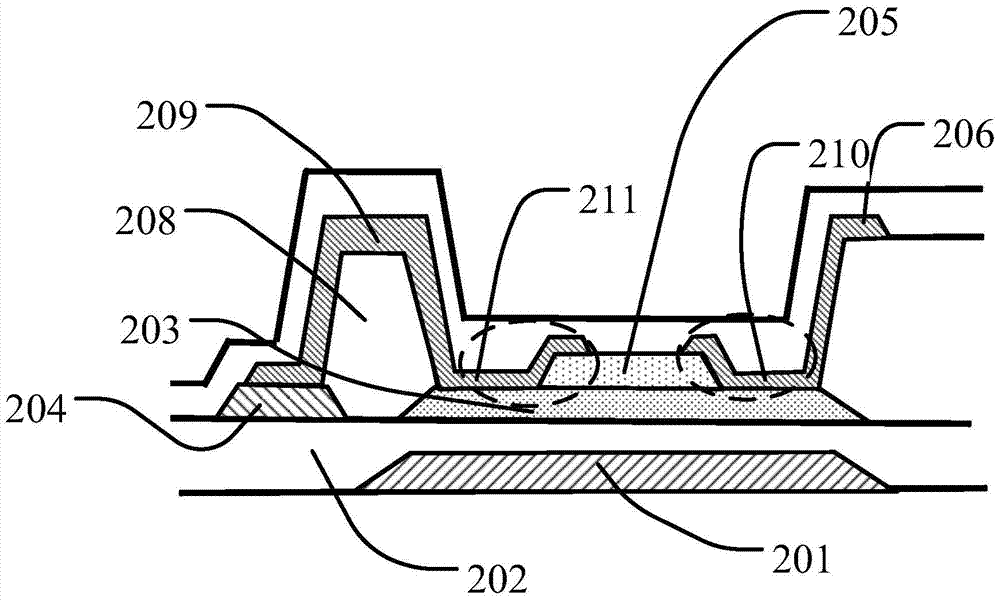

[0048] Please refer to image 3 , image 3 It is a schematic structural diagram of a thin film transistor array substrate provided in Embodiment 1 of the present invention. From image 3 It can be obtained that the thin film transistor array substrate provided in this embodiment includes: a substrate (not shown in the figure); a plurality of intersecting and insulated scanning lines (not shown in the figure) and a plurality of data lines arranged on the substrate line 204, and a plurality of pixel units defined by the scan line and the data line 204; a thin film transistor disposed in the pixel unit.

[0049] The thin film transistor comprises: a gate 201; a gate insulating layer 202 disposed on the gate 201; a mutually insulated semiconductor active layer 203 disposed on the gate insulating layer 202; disposed on the semiconductor The etch barrier layer 205 on the active layer 203; the source electrode 211 and the drain electrode 210 arranged on the semiconductor active la...

Embodiment 2

[0056] Please refer to Figure 4 to Figure 10 , Figure 4 to Figure 10 It is a schematic structural diagram of the array substrate during the manufacturing process provided by Embodiment 2 of the present invention. A method for manufacturing a thin film transistor array substrate provided in this embodiment includes: providing a substrate (not shown in the figure); forming a first metal layer on the substrate, patterning the metal layer, and forming a gate 201, such as Figure 4 As shown; a gate insulating layer 202 is formed on the gate 201; a semiconductor layer is formed on the gate insulating layer 202, and the semiconductor layer is patterned to form a semiconductor active layer 203, as Figure 5 As shown; a first insulating layer is formed on the semiconductor active layer 203, and the insulating layer is patterned to form an island-shaped etch stop layer 205, as Figure 6 As shown; a second metal layer is formed on the gate insulating layer 202, and the second metal ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More