Double-surface low-parasitic inductance GaN power integrated module

A low parasitic inductance, power integration technology, applied in the direction of circuits, electrical components, electric solid devices, etc., to achieve the effect of reducing area, avoiding oscillation and spikes, and reducing parasitic inductance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0020] The present invention will be further described below in conjunction with drawings and embodiments.

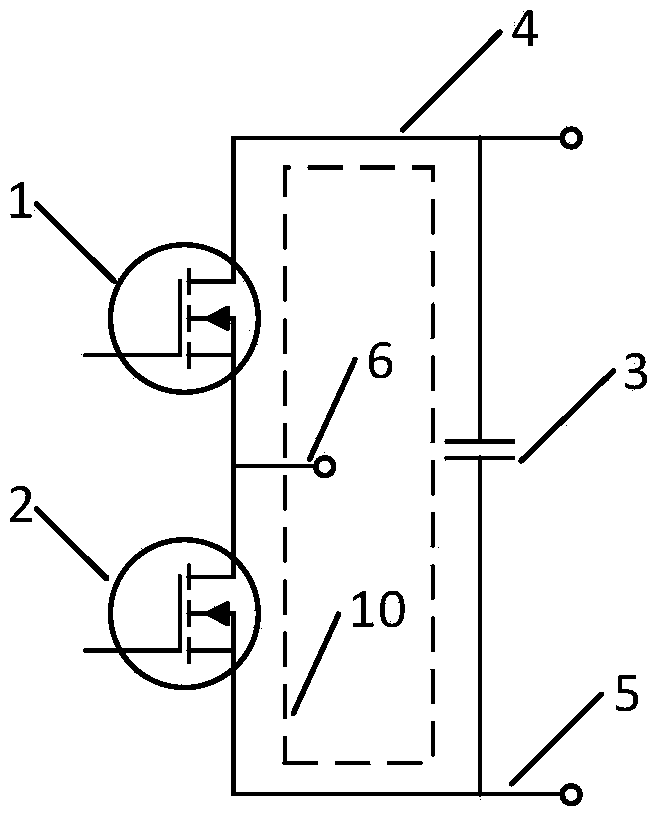

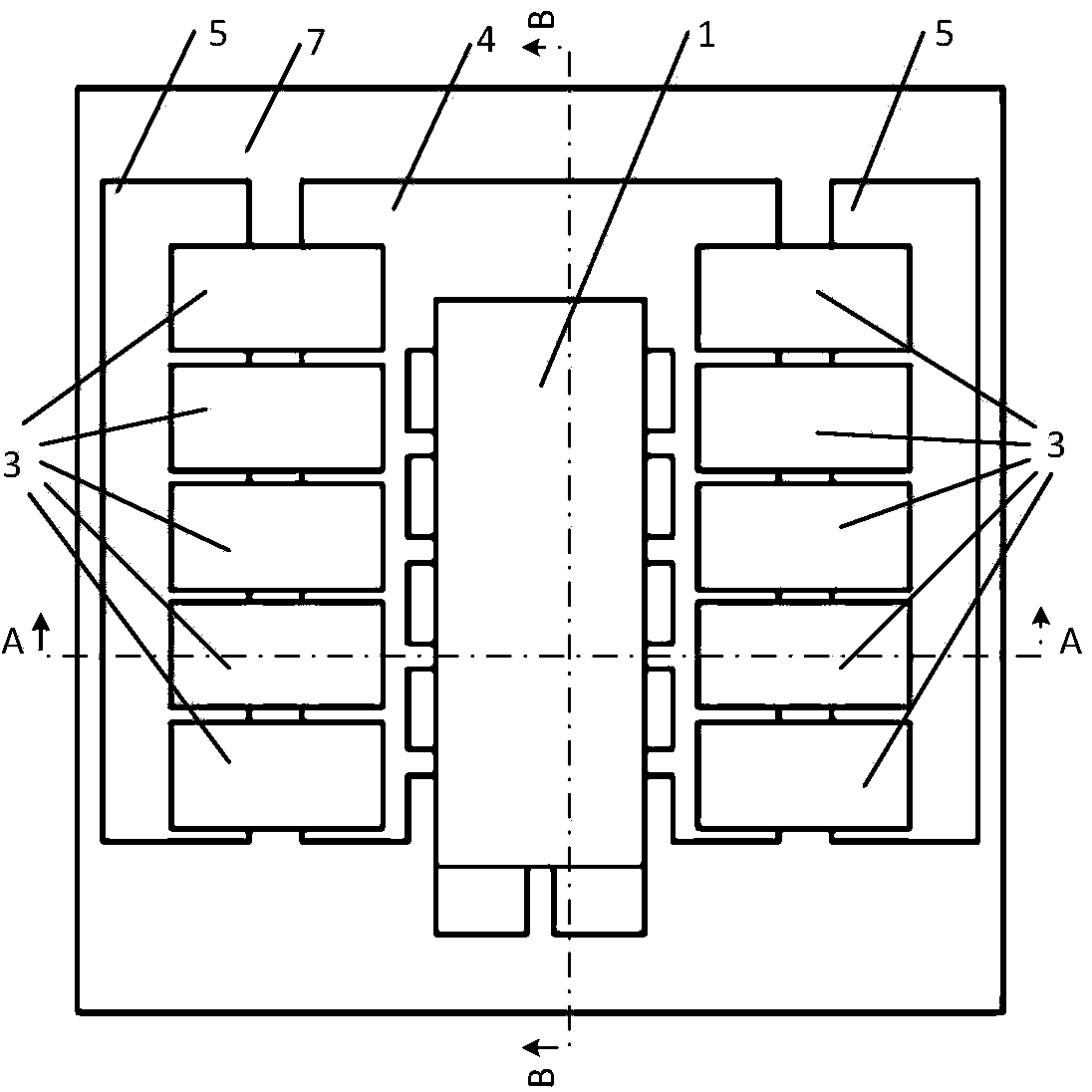

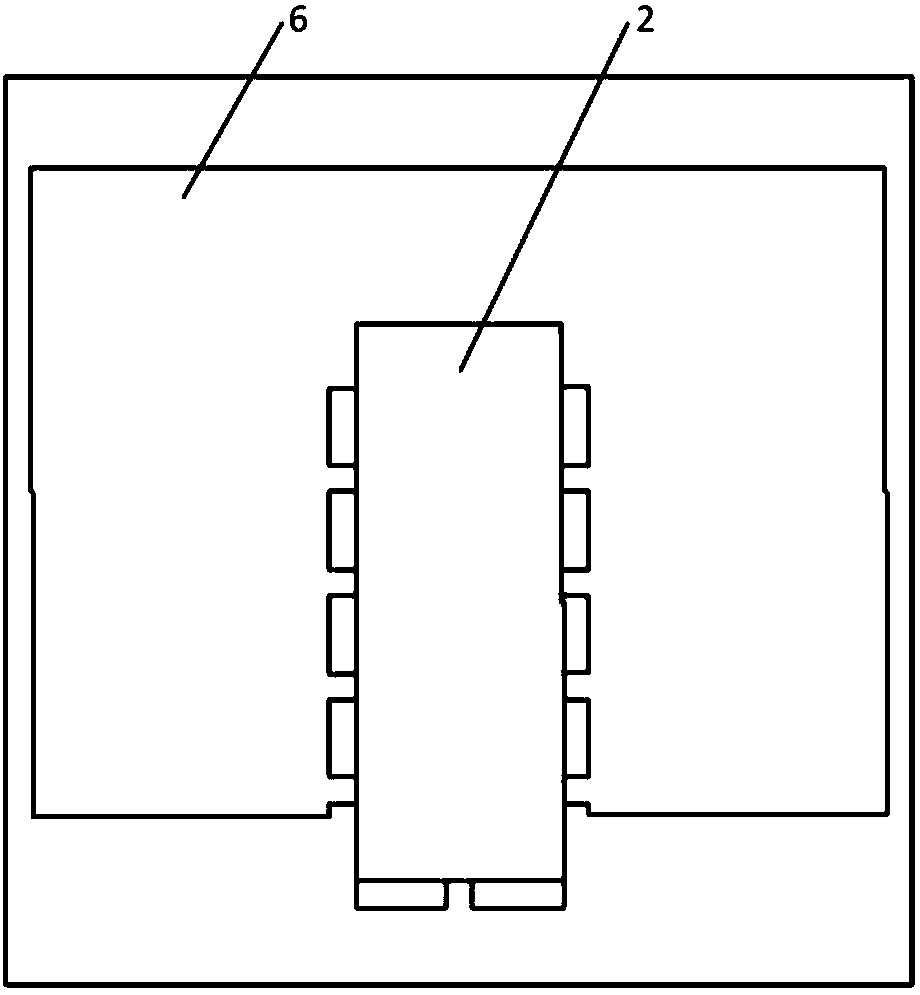

[0021] In the GaN power integrated module of the present invention, the upper bridge arm device 1, the lower bridge arm device 2 and the bus capacitor 3 are sequentially connected to form a high frequency power circuit 10, and the upper bridge arm device 1 and the lower bridge arm device 2 are respectively placed on the substrate 7 (The substrate is a PCB board or LTCC board), the source of the upper bridge arm device 1 and the drain of the lower bridge arm device 2 are placed facing each other, and are directly connected through via holes; the bus capacitor 3 is placed on the upper bridge arm One or both sides of the device 1; all the drains of the upper bridge arm device 1 are connected to one electrode of the bus capacitor 3 on the side close to the bus capacitor, and the other electrode of the bus capacitor 3 is connected to the middle conductive layer 12 through a v...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com