Signal transmission circuit suitable for DDR (Double Date Rate Synchronous Dynamic Random Access Memory)

A signal transmission and circuit technology, applied in the direction of logic circuit coupling/interface, logic circuit, logic circuit connection/interface arrangement using field effect transistors, etc., can solve problems such as signal instability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

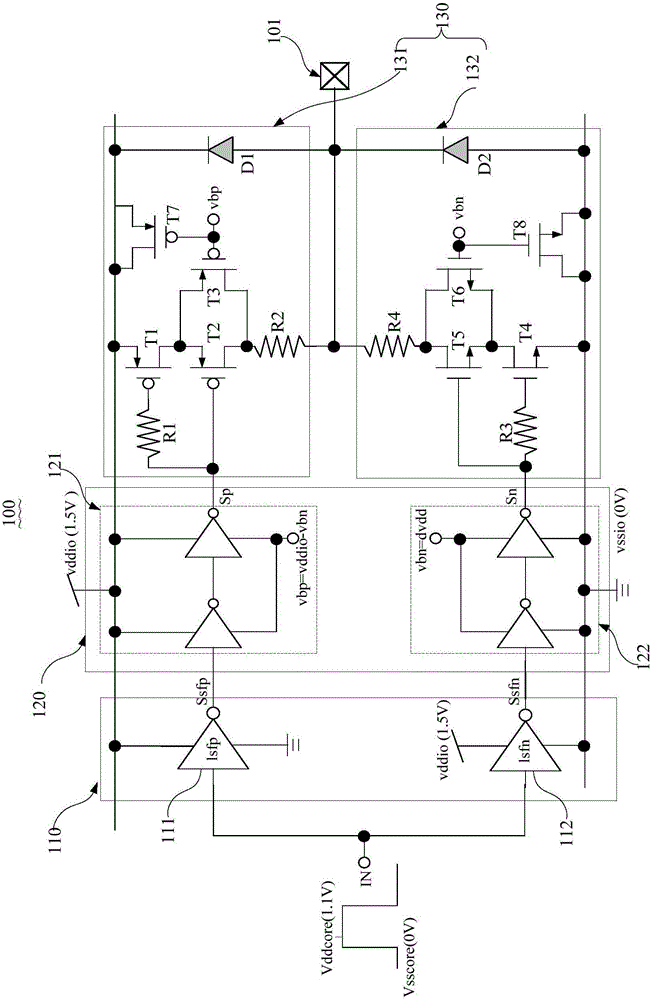

[0027] see image 3 , which is a schematic diagram of a signal transmission circuit suitable for DDR shown in an embodiment of the present invention. Here, DDR3 is taken as an example to introduce the present invention, and its operating voltage is 1.5V. Of course, the present invention is not limited thereto, and it can also be applied to other types of DDR, such as DDR3L with an operating voltage of 1.35V or an operating voltage of 1.35V. 1.2V DDR4.

[0028] Such as image 3 As shown, the signal transmission circuit 100 of the present invention is used to drive the connection pad 101 , which includes a level shift circuit 110 , a buffer circuit 120 and an output circuit 130 .

[0029] The level shifter circuit 110 includes an upper level shifter 111 and a lower level shifter 112, wherein the upper level shifter 111 and the lower level shifter 112 are respectively set at the operating voltage Vddio (1.5V) and ground voltage of DDR3 between Vssio(0V). And the upper level s...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More