AES encryption/decryption circuit based on data redundancy error detection mechanism

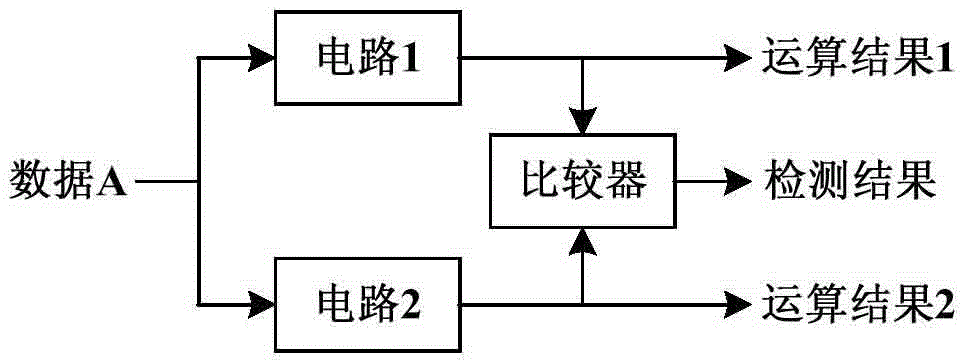

A data redundancy and data technology, applied in the direction of encryption device with shift register/memory, etc., can solve the problems of high data processing speed and large circuit area, so as to reduce circuit area, avoid wrong information transmission, and improve information efficiency. Effects of Sexuality and Reliability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0043] The present invention will be further described below with reference to the accompanying drawings and in conjunction with specific embodiments.

[0044] In the present invention, the round transformation operation that does not include column mixing (inverse column mixing) operation is called the last round of round transformation operation. The present invention also takes the key addition operation independent of the round transformation operation as a round of special round transformation operation. Since the reverse key addition operation is the same as the key addition operation, the present invention is collectively referred to as the key addition operation.

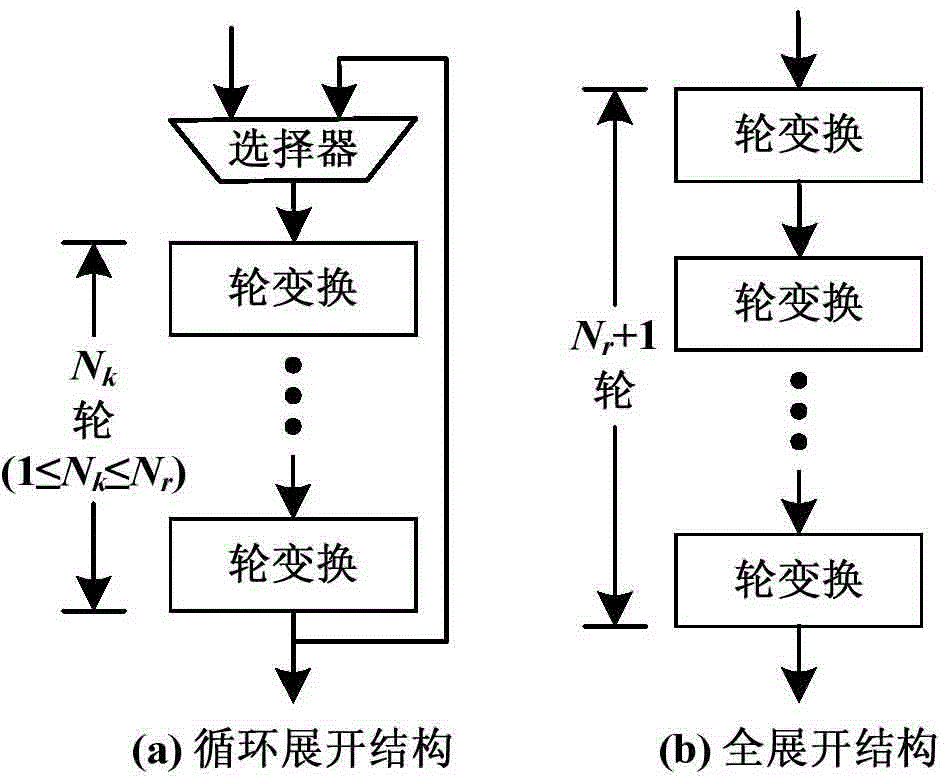

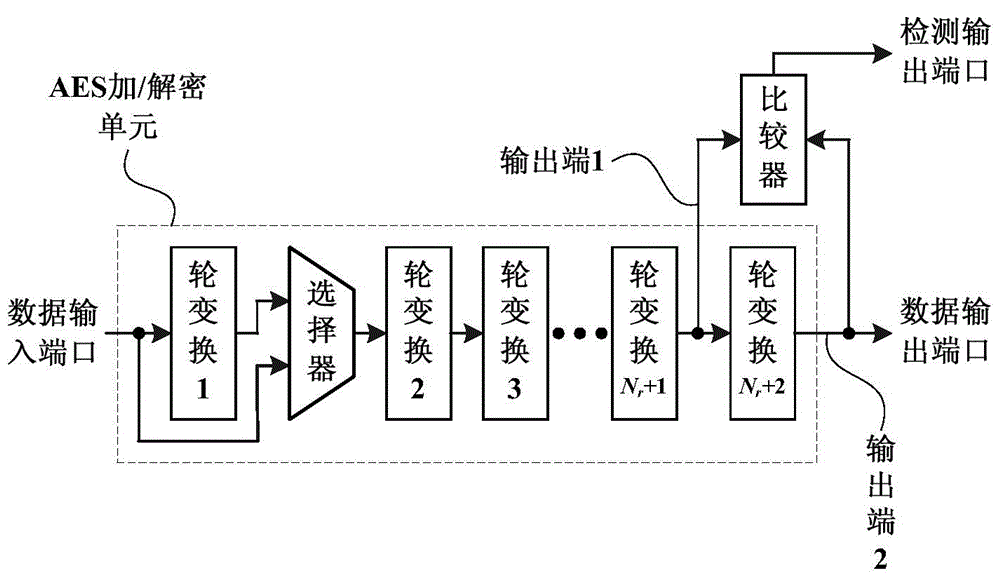

[0045] see image 3 , an implementation example of the present invention is that the AES encryption / decryption unit adopts a fully expanded structure to realize. like image 3 As shown, the circuit structure includes AES encryption / decryption unit and comparator, and the circuit also includes data input p...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More