Storage unit and storage array erasing method

A storage unit and storage array technology, applied in the field of memory, can solve problems such as low memory durability, and achieve the effects of increasing read current, increasing voltage difference, and improving durability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

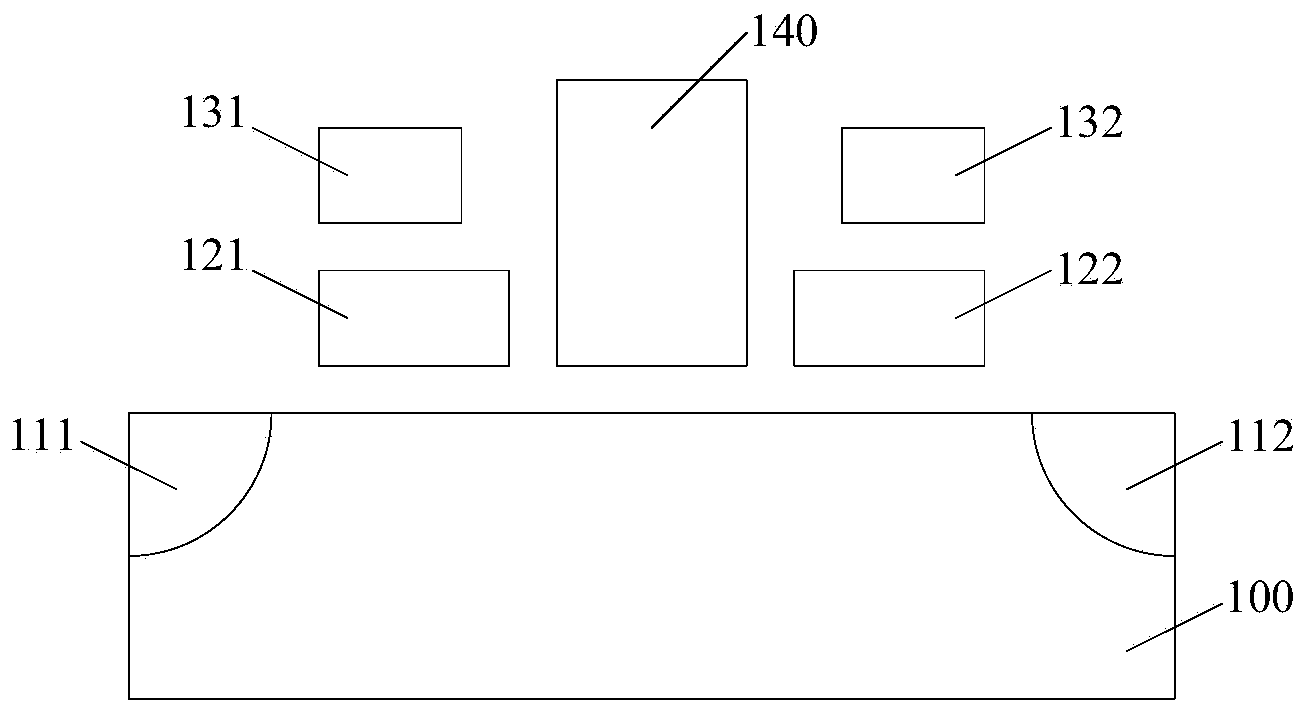

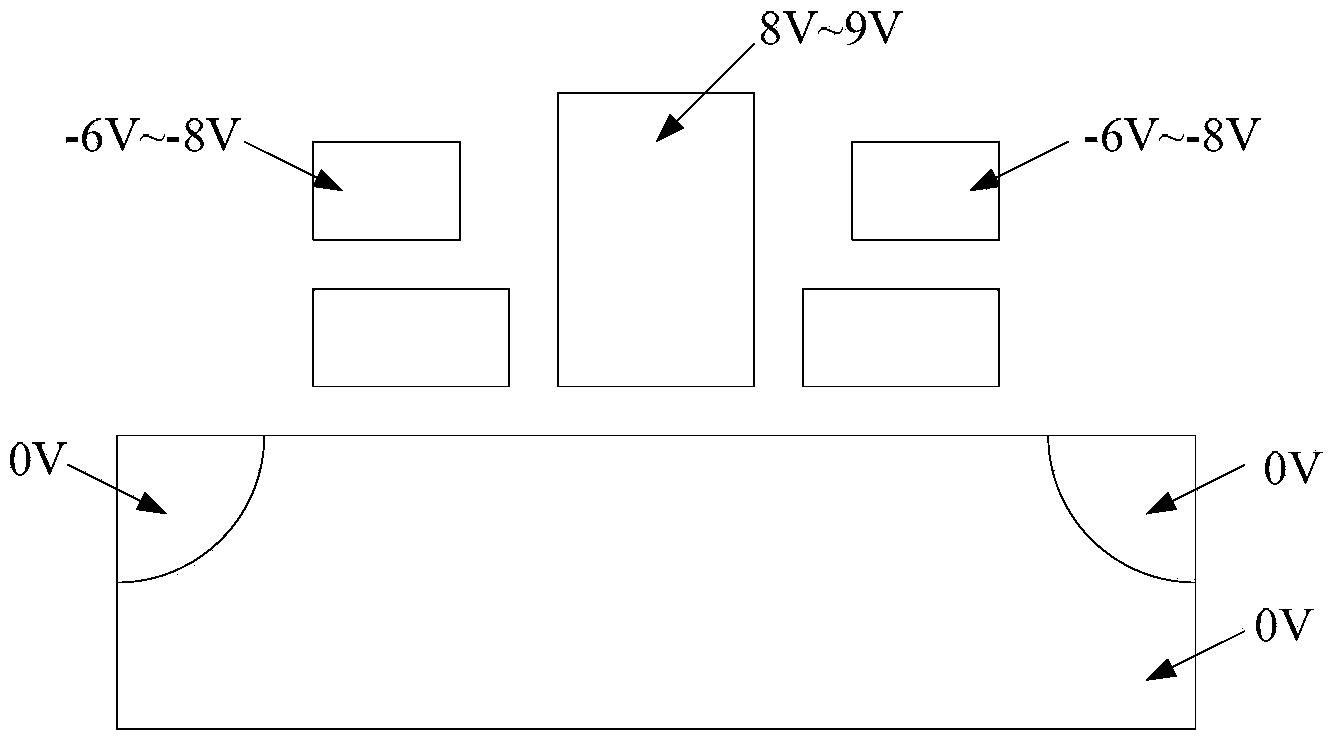

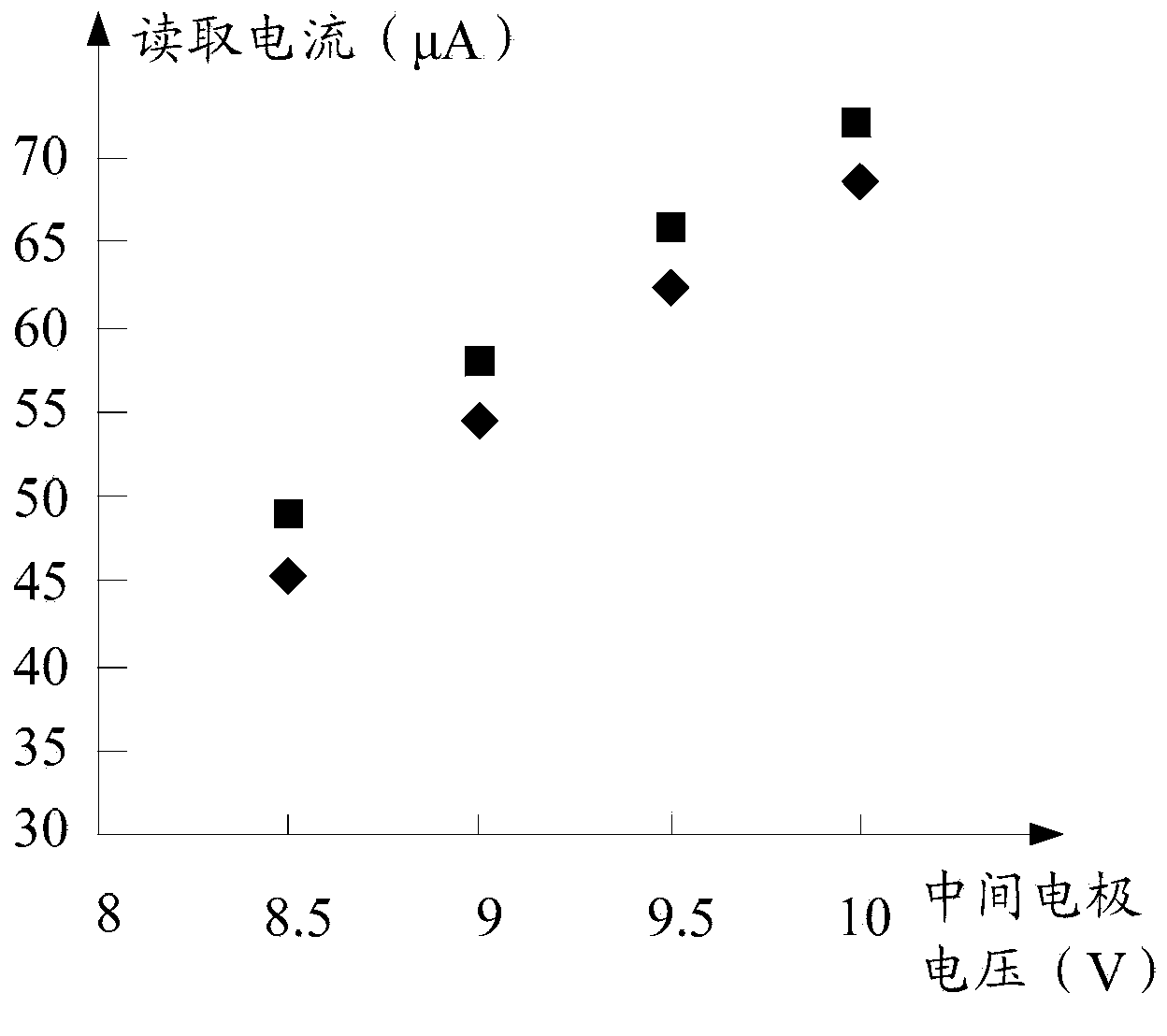

[0053] Endurance is an important index to measure the reliability of the memory, which means that the read current of the memory still meets the requirements after multiple erasing operations. for figure 1 For the shown memory cell, the magnitude of the read current after the erase operation is related to the applied erase voltage. for research figure 1 The specific relationship between the read current of the shown memory cell and the applied erasing voltage, the inventor adopts the erasing method of the prior art to figure 1 The memory cells shown were verified twice.

[0054] When verifying for the first time, multiple erasing operations are performed on the memory cell, and in each erasing operation, the voltage applied to the P-type well region 100 is the same, and the voltage applied to the drain 111 is the same, The voltage applied to the source 112 is the same, the voltage applied to the first control gate 131 is the same, the voltage applied to the second control g...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More