pmos transistor and its manufacturing method

A manufacturing method and transistor technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve the problems of slow carrier migration rate of PMOS transistors, reduce leakage current, increase migration rate, and avoid surface The effect of defects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

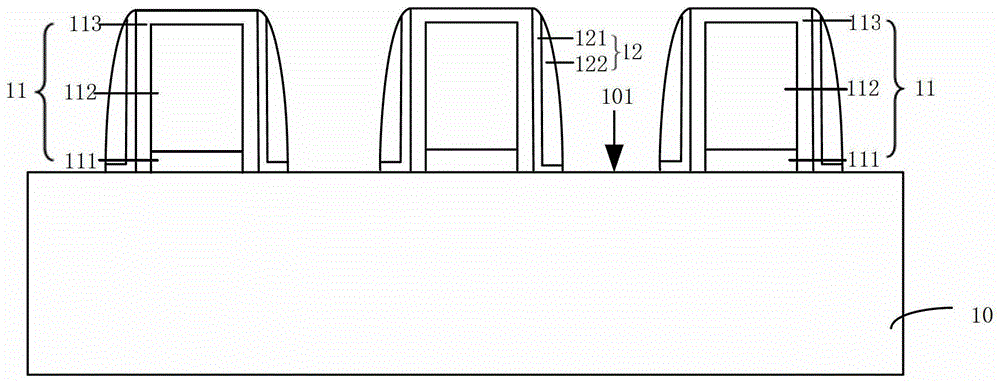

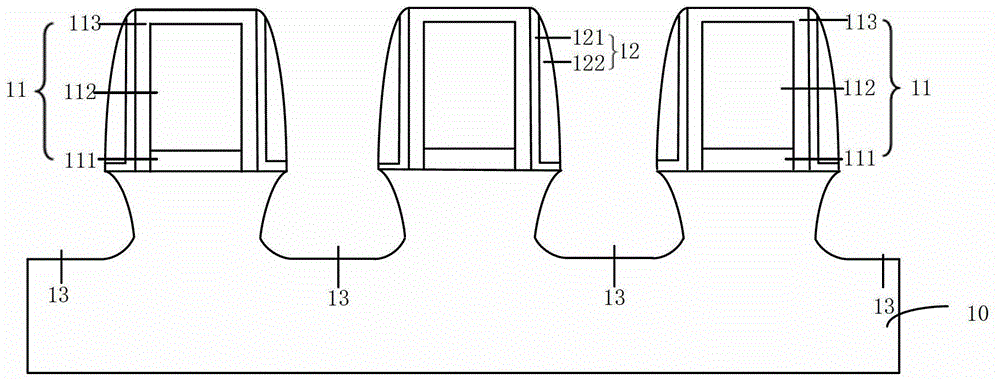

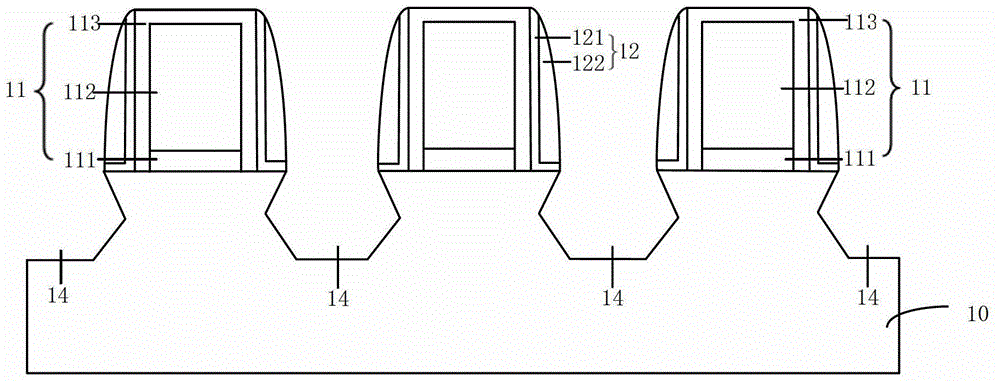

[0036] As mentioned above, in order to increase the compressive stress applied to the channel, when the present invention fills the sigma-shaped groove of the source / drain region with silicon-germanium material, the surface of the silicon-germanium material is higher than the surface of the silicon substrate to increase the silicon-germanium material. Filling amount of germanium material. In addition, in the semiconductor process, in addition to making PMOS transistors, other semiconductor devices, such as NMOS transistors, need to be formed in other areas of a wafer. Therefore, when performing ion implantation on the wafer to form the lightly doped region of the PMOS transistor, other The area needs to be covered with photoresist to protect it, and after the shallow junction is made, this photoresist residue needs to be removed. In order to prevent the above cleaning process from corroding the SiGe material, the present invention covers the side of the SiGe material with a pr...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More