Semiconductor integrated device

A technology for integrating devices and semiconductors, which is applied in semiconductor devices, electrical solid devices, electrical components, etc., and can solve problems such as damage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

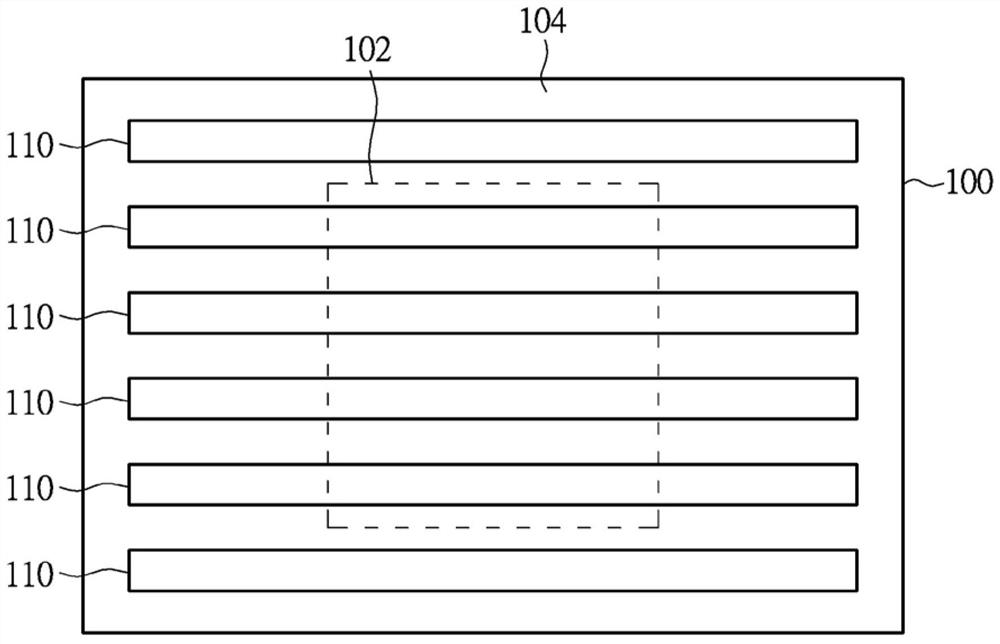

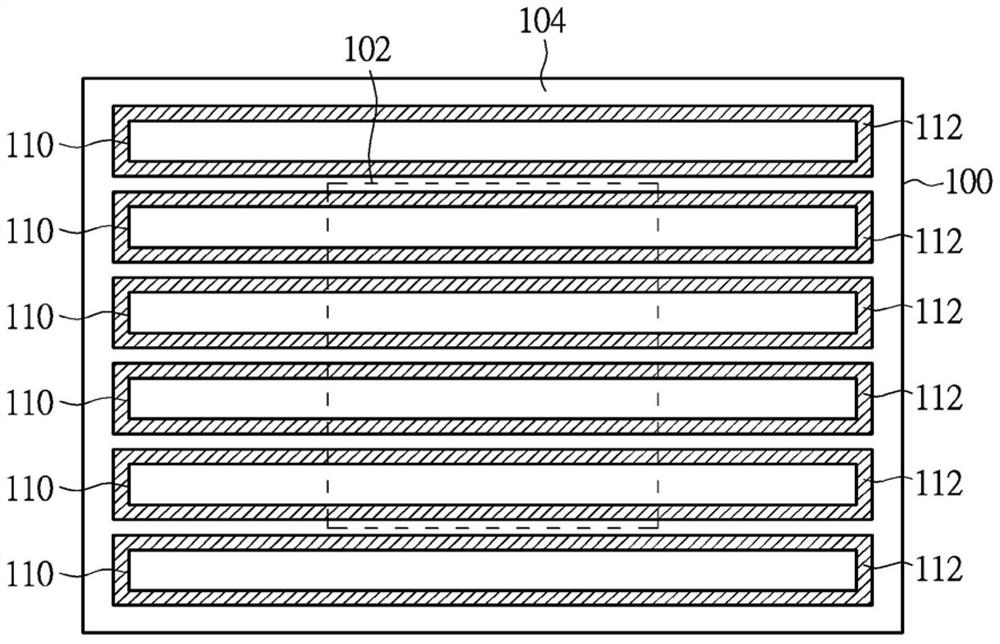

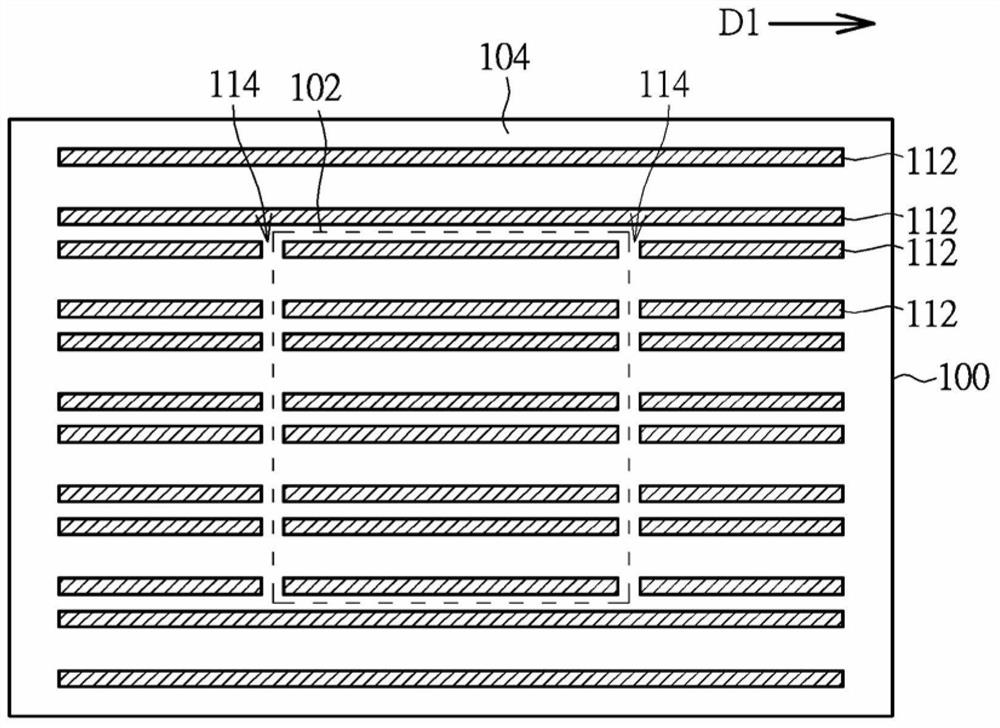

[0034] see Figure 1 to Figure 4 , Figure 1 to Figure 4 It is a schematic diagram of a first preferred embodiment of a semiconductor integrated device provided by the present invention. Such as figure 1 As shown, this preferred embodiment first provides a substrate 100, the substrate 100 may include a silicon-on-insulator (SOI) substrate, as known to those skilled in the art, the SOI substrate can be formed from bottom to top It sequentially includes a silicon substrate, a bottom oxide (BOX) layer, and a semiconductor layer formed on the bottom oxide layer, such as a silicon layer with a single crystal structure. In addition, the substrate provided in this preferred embodiment may include a bulk silicon substrate. An active area 102 and a peripheral area 104 surrounding the active area 102 are defined on the substrate 100 . Those skilled in the art should know that although the peripheral area 104 surrounds the active area 102 in this preferred embodiment, the relative rel...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More