Method for forming CMOS (Complementary Metal-Oxide-Semiconductor) transistor

A transistor and gas technology, applied in the field of formation of CMOS transistors, can solve the problems of complex process steps and poor performance of CMOS transistors, and achieve the effects of simple process, reduction of formation time, and reduction of adverse effects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0032] It can be seen from the background art that the performance of forming CMOS transistors in the prior art is poor and the process steps are complicated.

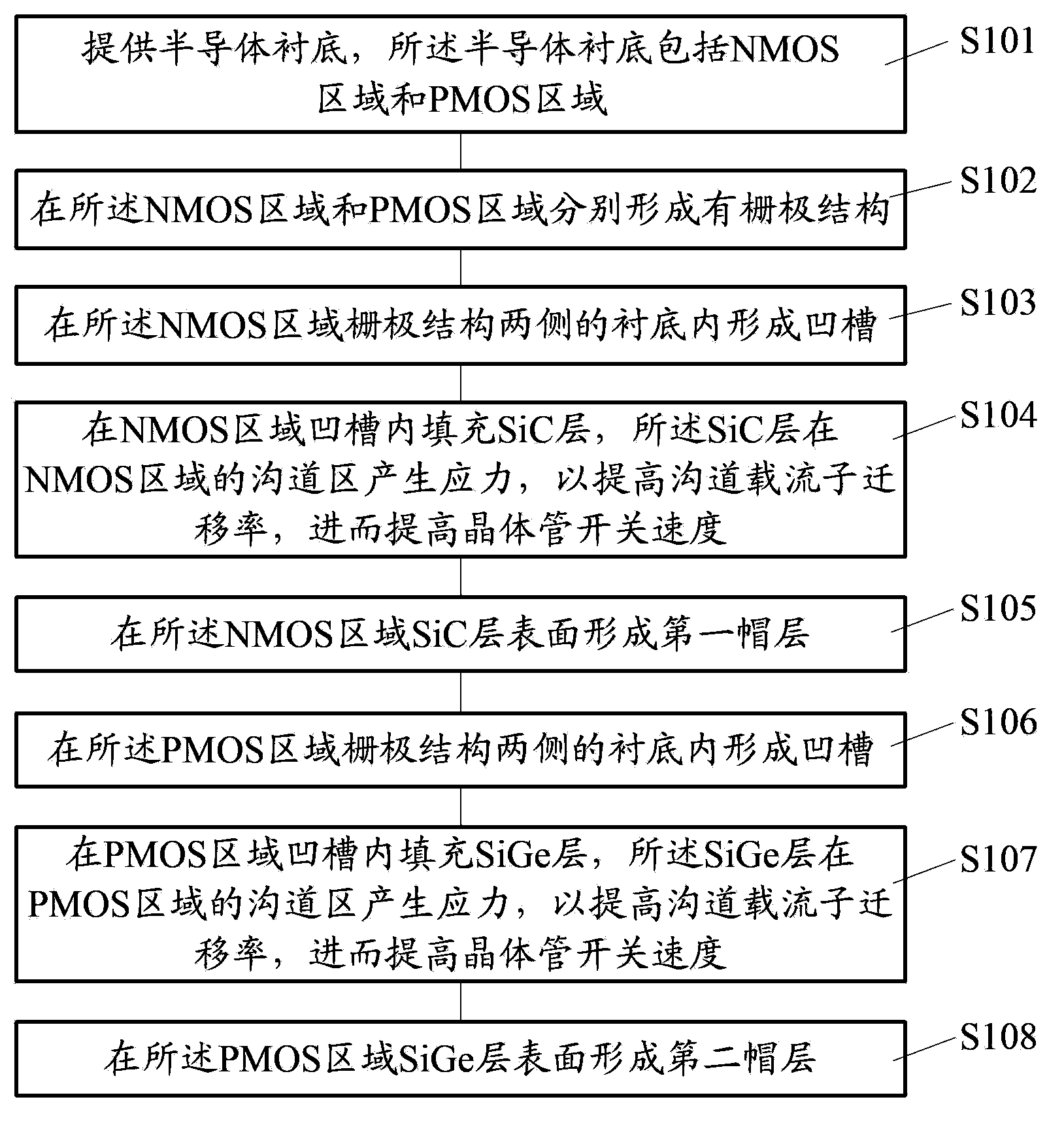

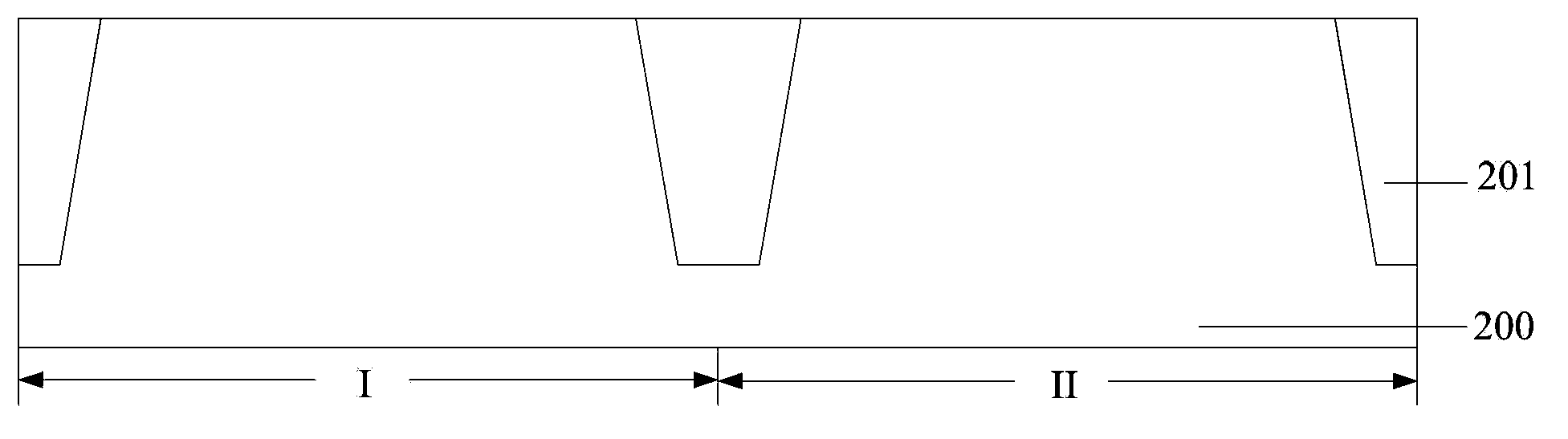

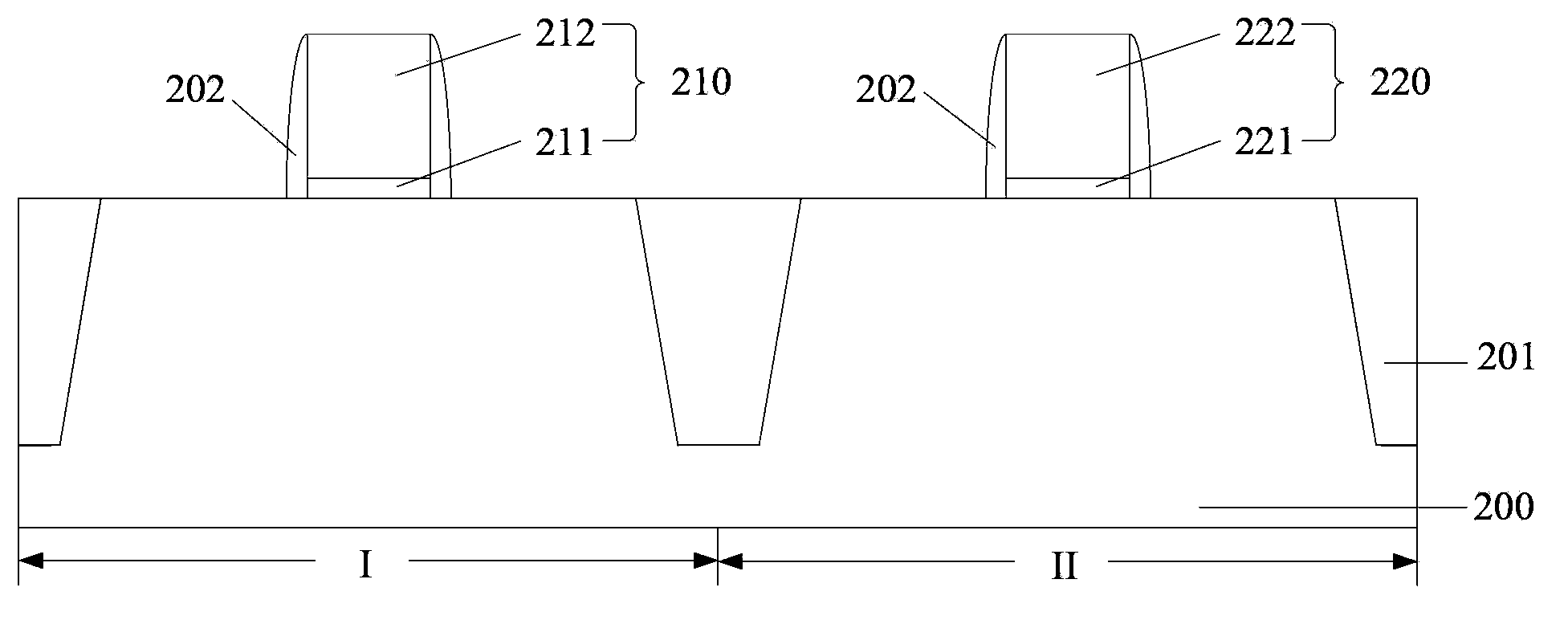

[0033] For this reason, the inventor studies the prior art CMOS transistor formation process, and finds that the CMOS transistor formation process includes the following steps, please refer to figure 1 Step S101, providing a semiconductor substrate, the semiconductor substrate includes an NMOS region and a PMOS region; Step S102, forming a gate structure in the NMOS region and the PMOS region respectively; Step S103, forming a gate structure in the NMOS region Grooves are formed in the substrates on both sides; step S104, filling the SiC layer in the groove of the NMOS region, and the SiC layer generates stress in the channel region of the NMOS region to increase the carrier mobility of the channel, thereby improving the transistor Switching speed; step S105, forming a first cap layer on the surface of the SiC layer in...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More