Rapid synchronous phasor correction method

A synchronized phasor and fast technology, which is applied in the direction of measuring devices, measuring electrical variables, and the phase angle between voltage and current, etc., can solve the problems of real-time measurement performance, phasor amplitude, angle accuracy reduction, and compensation failure. And other issues

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

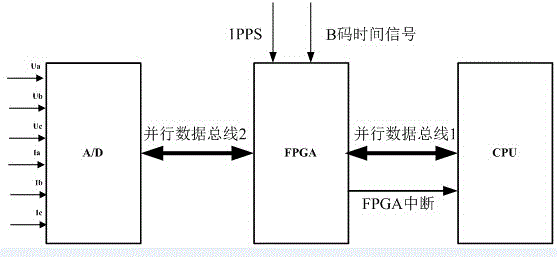

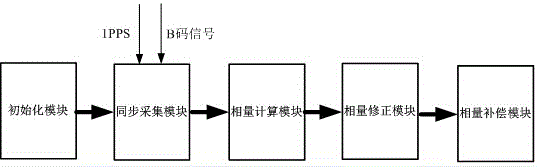

[0054] Attached below figure 1 And attached figure 2 , to further elaborate the technical content of the present invention. The following examples are only used to illustrate the technical solution of the present invention more clearly, but not to limit the protection scope of the present invention.

[0055] Such as figure 1 and figure 2, the present invention provides a kind of quick synchrophasor correction method, and this method comprises the following steps:

[0056] (1) FPGA and CPU are connected by 32-bit or 64-bit parallel bus 1 in hardware, FPGA has an interrupt signal connected to the external interrupt pin of CPU, FPGA is connected to 1PPS signal of standard clock and B code time signal, FPGA passes Parallel bus 2 controls the AD chip;

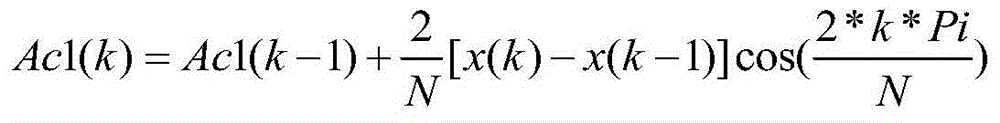

[0057] (2) Define the sampling configuration register (CONFIG_REG), sampling buffer register (DATA_REG), DFT coefficient original register (DFT_COEF), filter coefficient register (FIR_COEF), and DFT result buffer register (DF...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com