EtherCAT dual-network data reading and writing system and method thereof

A technology of data reading and writing and data, which is applied in the field of EtherCAT dual-network data reading and writing system, which can solve the problems of long-term occupation of the bus of the main control chip, the decline of real-time performance of the control system, and the impact on the real-time performance of the control system, so as to shorten the waiting time , reduce overhead, and run faster

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0049] The specific implementation manners of the present invention will be further described in detail below in conjunction with the accompanying drawings.

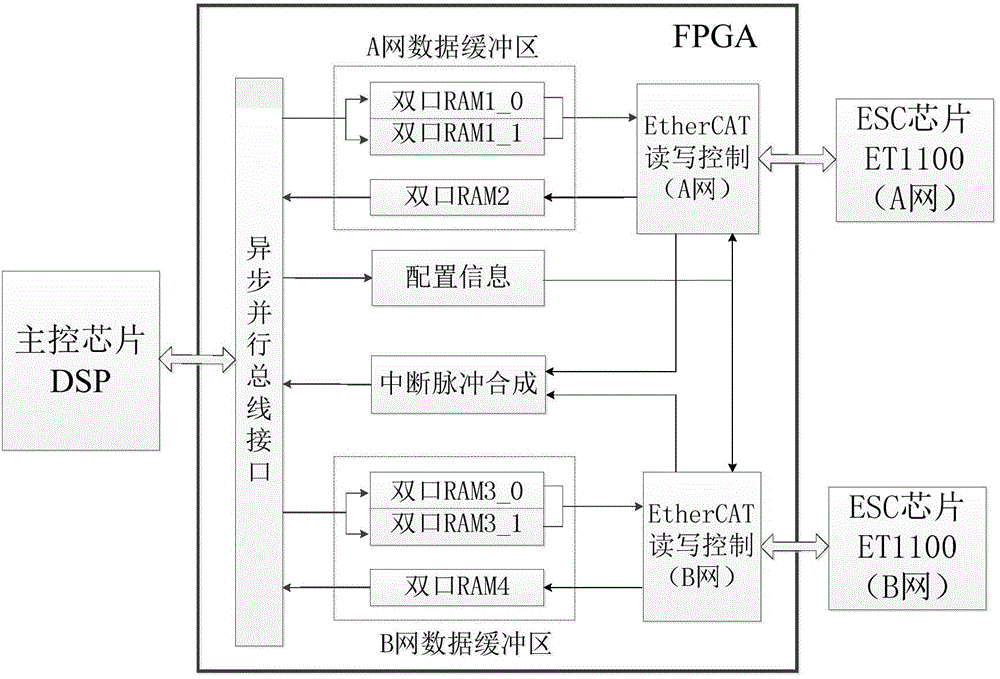

[0050] Such as figure 1 As shown, the present invention provides a FPGA-based EtherCAT dual-network data reading and writing system, and the FPGA selects the Spartan series of Xilinx Company, with a programmable Block RAM inside. The main control chip is TI's C2000 series DSP, which supports 16-bit data bus; the ESC chip is Beckhoff's ET1100 chip. Connect the FPGA to the bus interface of the main control chip, ESC chip ET1100 (A network) and ESC chip ET1100 (B network). The address bus and data bus are both 16 bits.

[0051] FPGA internal function module of the present invention is specifically as follows:

[0052] Asynchronous parallel bus interface module; dual-port RAM1 module with ping-pong control; dual-port RAM2 module; EtherCAT read and write control (A network) module; configuration information module; dual-por...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More