A single-event flip-resistant static random memory unit

A static random storage, anti-single particle technology, applied in static memory, information storage, digital memory information, etc., can solve the problems of writing time and area cost, power consumption and area, and writing delay, etc., to achieve enhanced Anti-single particle ability, small footprint, and the effect of increasing speed

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0021] The present invention will be described in further detail below in conjunction with the accompanying drawings:

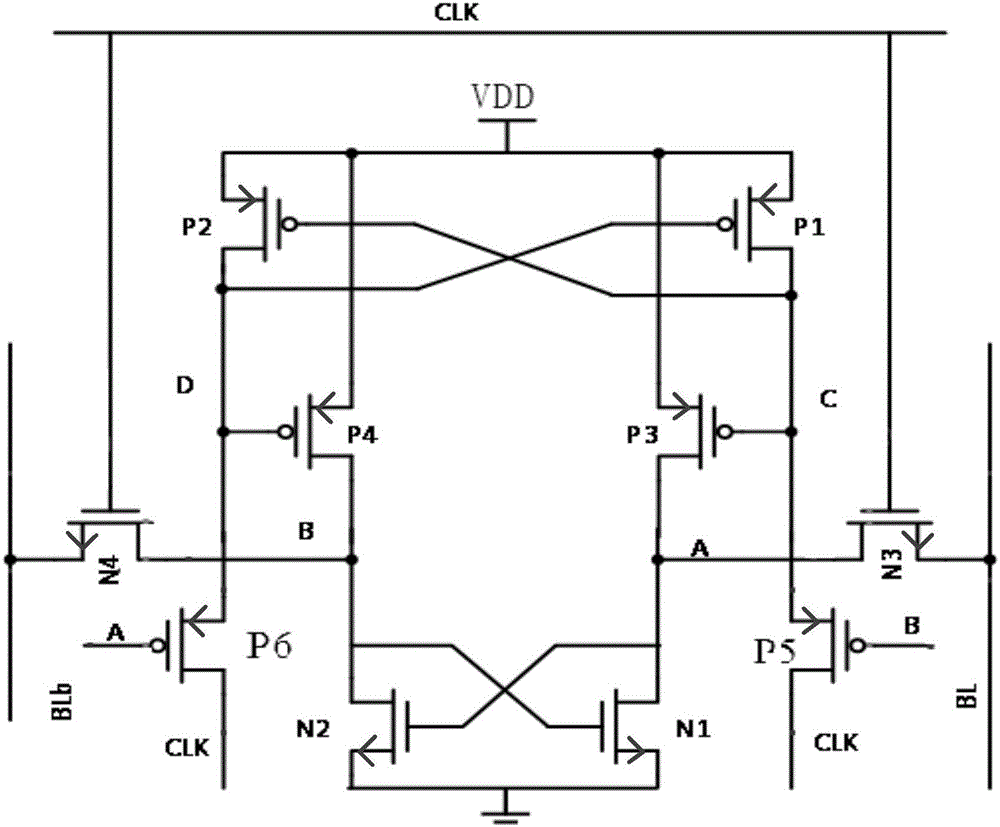

[0022] reference figure 1 The static random storage unit against single event upset of the present invention includes a signal input terminal BL, a signal output terminal BLb, a clock port CLK, a first control node C, a second control node D, a first storage node A, and a second Storage node B, first PMOS tube P1, second PMOS tube P2, third PMOS tube P3, fourth PMOS tube P4, fifth PMOS tube P5, sixth PMOS tube P6, first NMOS tube N1, and second NMOS tube N2, the third NMOS transistor N3, and the fourth NMOS transistor N4; the gate and drain of the first PMOS transistor P1 are connected to the second control node D and the first control node C, respectively, the source of the first PMOS transistor P1 and The substrate is connected to the power supply VDD; the gate and drain of the second PMOS transistor P2 are respectively connected to the first control node C an...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More