PMOS (p-channel metal oxide semiconductor) device and manufacturing method thereof

A manufacturing method and device technology, which is applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve the problems of PMOS performance improvement obstacles, achieve size reduction, improve performance, and increase the saturation current.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

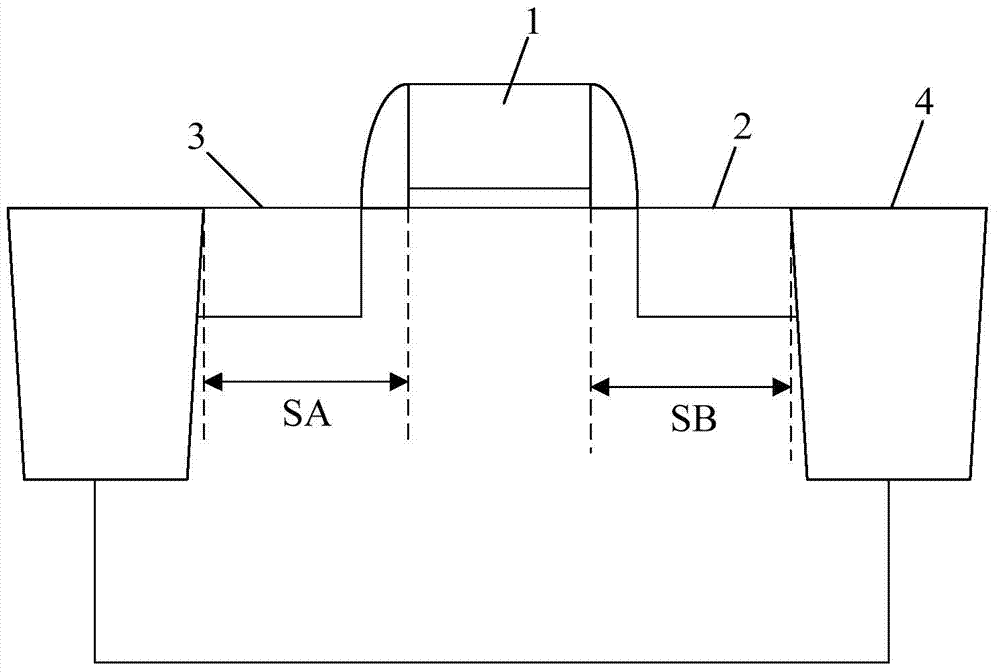

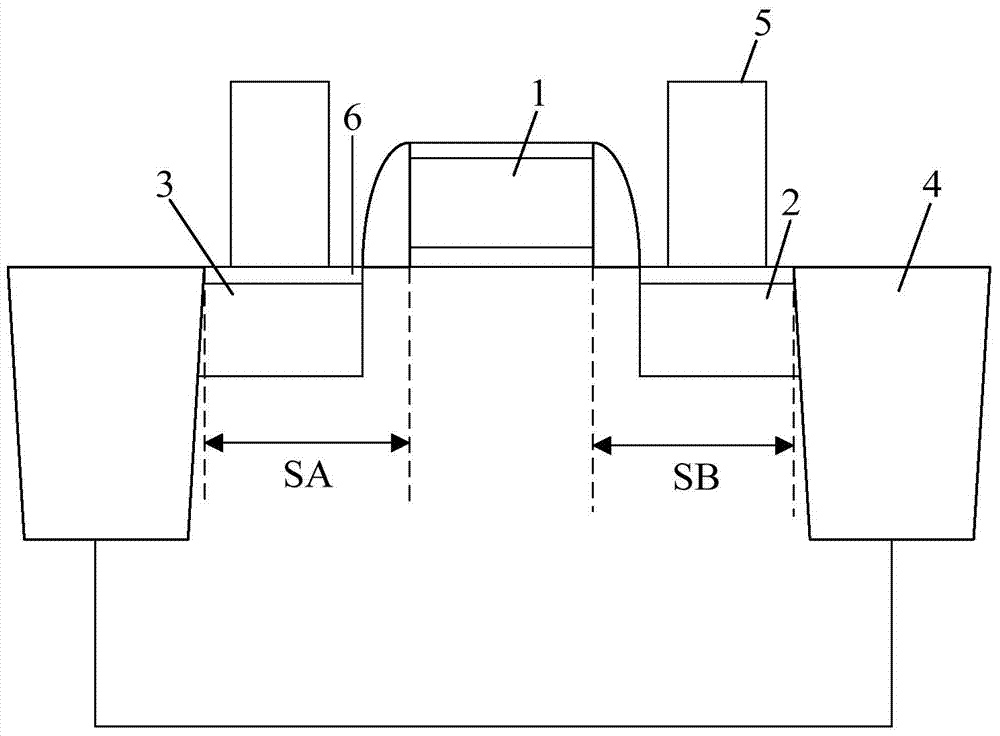

[0044] refer to figure 1 with figure 2 As shown, in the existing PMOS device, a conductive plug 5 is formed on the source region 3 and the drain region 2, and a contact layer 6 is also formed between the source region 3, the drain region 2 and the conductive plug 5 for Reduce contact resistance.

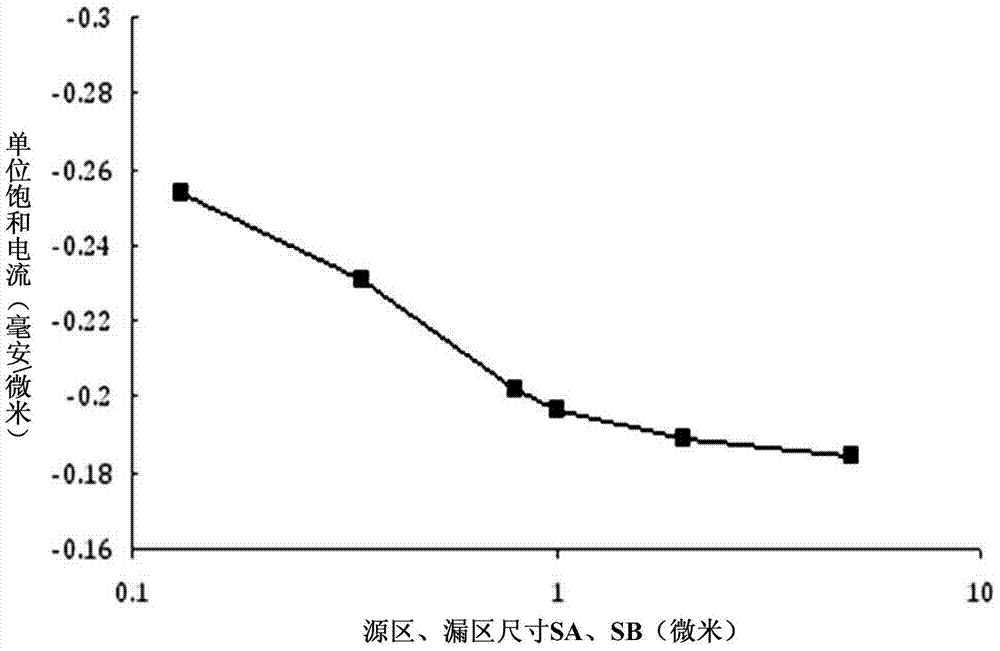

[0045] In order to prevent the deviation of the formation position of the conductive plug 5 , the conductive plug 5 is formed on the gate 1 (including the sidewall of the gate 1 ) or the isolation region 4 , thereby resulting in failure of the conductive plug 5 . The size of the existing source region 3 and drain region 2 is usually relatively large in the horizontal direction (such as figure 1 with figure 2 As shown, SA and SB represent the size of the source region 3 and the drain region 2 respectively, and SA and SB are usually 0.3 to 0.35 microns), so that even if there is a certain deviation in the position of the conductive plug 5 formed in the subsequent steps, the still...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More