Method for Integrating Power Devices and Control Devices

A technology for controlling devices and integrating power, which is applied in semiconductor/solid-state device manufacturing, electric solid-state devices, semiconductor devices, etc. It can solve the problem of poor compatibility between power devices and control devices, affecting device performance optimization, and occupying a large area and other issues to achieve the effect of reducing aspect ratio, reducing difficulty and improving performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0060] The present invention will be further described below in conjunction with the accompanying drawings and specific embodiments, but not as a limitation of the present invention.

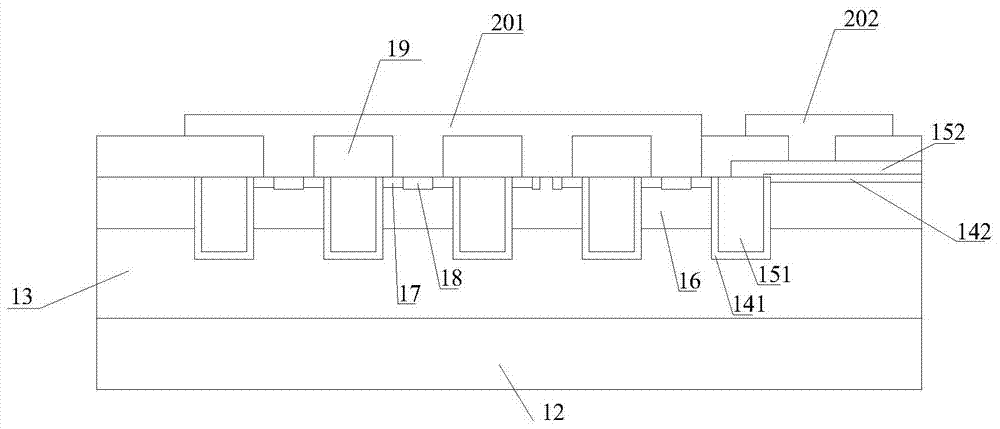

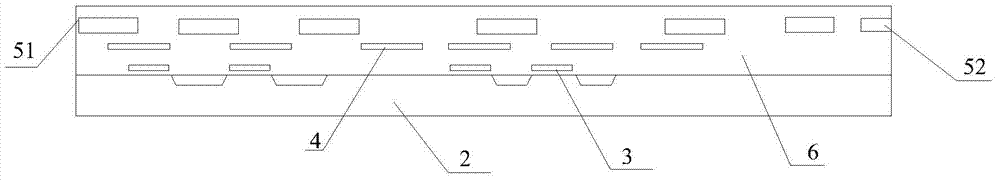

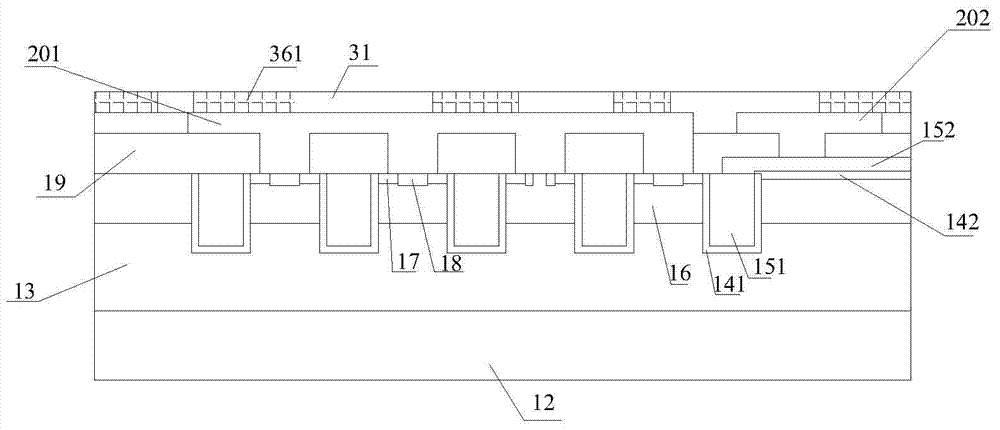

[0061] like Figure 14 As shown, the present invention provides a method for integrating power devices and control devices, comprising the following steps:

[0062] Provide a power chip prepared with a power device and a control chip prepared with a control device, and the power chip is provided with a drain region; the power device has a source electrode and a gate electrode, and the control device has a first control electrode and a second control electrode. electrode;

[0063] A first dielectric layer is deposited on the front of the power chip and the front of the control device, and part of the first dielectric layer is respectively etched to form a plurality of first openings, a plurality of second openings, a plurality of first openings and the plurality of first openings. The above-men...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More