Method for etching surface insulation layer of PAD at bottom of TSV hole of CIS product

A technology for insulating layers and products, applied in electrical components, semiconductor/solid-state device manufacturing, circuits, etc., can solve problems such as difficulty in exposure and development, inconsistent thickness of photoresist, and difficulty in detecting the complete development of the bottom, so as to save yellow light process , The effect of saving process cost

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0031] The present invention will be described in detail below in conjunction with specific embodiments shown in the accompanying drawings. However, these embodiments do not limit the present invention, and any structural, method, or functional changes made by those skilled in the art according to these embodiments are included in the protection scope of the present invention.

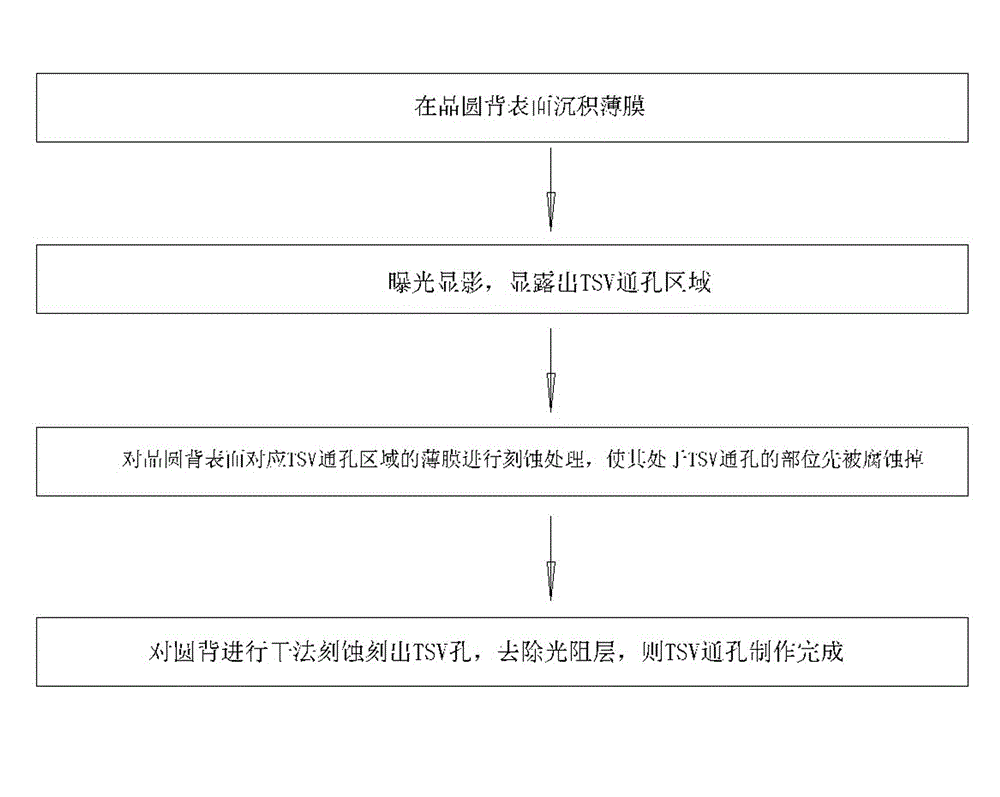

[0032] figure 1 Shown is the flow chart of the etching method of the PAD surface insulating layer at the bottom of the TSV hole of the CIS product involved in the present invention.

[0033] A kind of etching method of PAD surface insulation layer at bottom of CIS product TSV hole of the present invention, it comprises following specific steps:

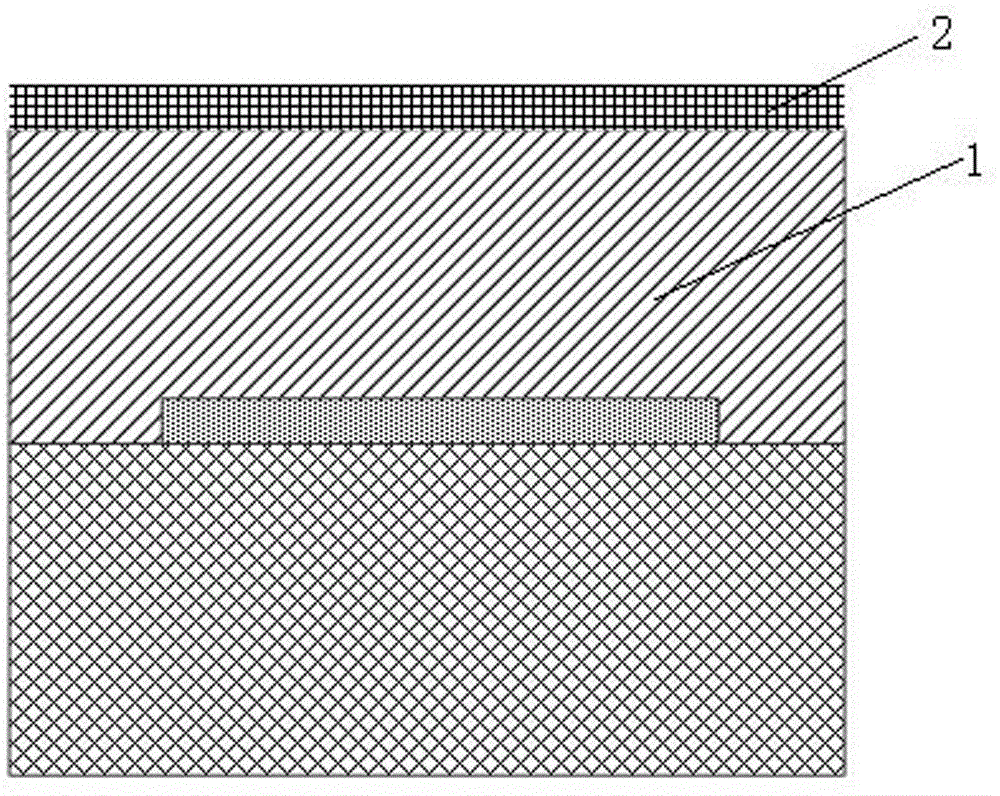

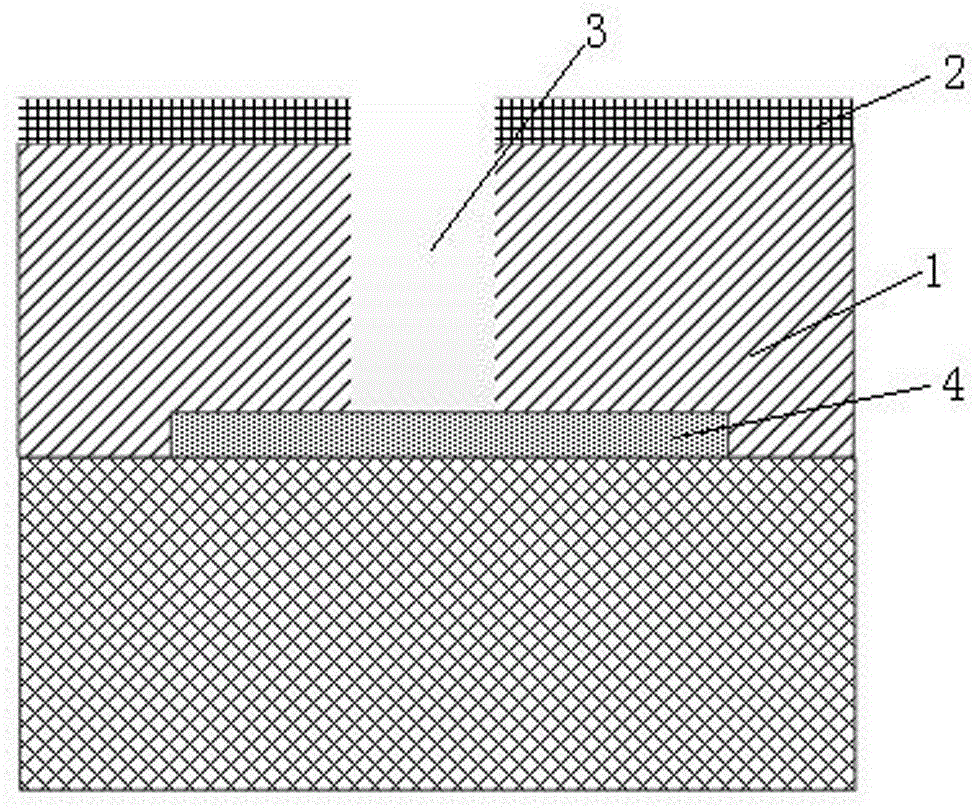

[0034] (1), see figure 2 , first deposit a layer of first insulating layer 2 on the wafer 1 surface where the TSV holes are to be etched;

[0035] Deposit a layer of first insulating layer on the surface of the TSV wafer to be opened. The insulating layer ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com