Storage unit of static random access memory based on dice structure

A static random access memory cell technology, applied in the fields of static random access memory, integrated circuit design and manufacturing, can solve the problems of excessive area and large number of transistors, and achieve the effect of small area overhead and reduced number

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

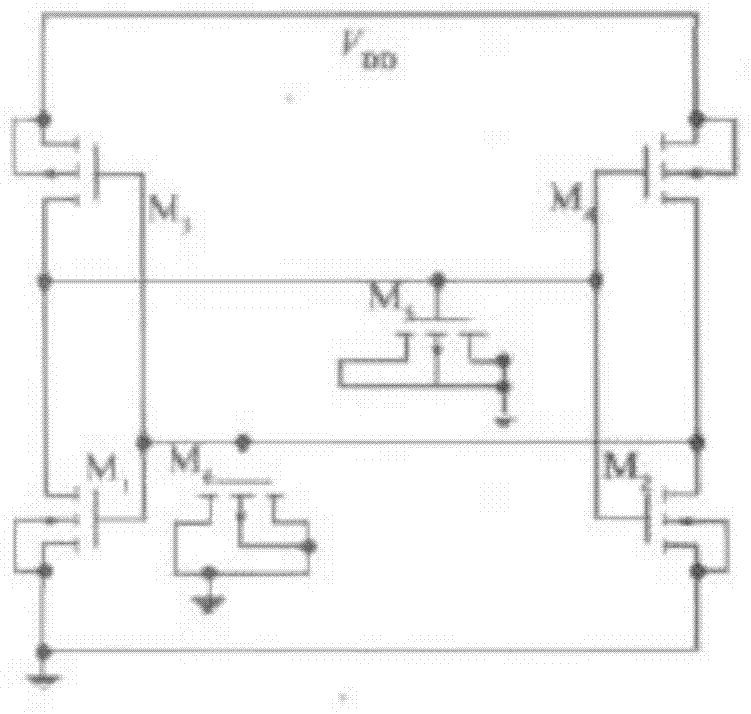

[0020] like Figure 7 As shown, this embodiment includes a redundant information latch circuit and a redundant bit selection circuit. The redundant information latch circuit is composed of NMOS transistors N0, N1, N2, and N3 connected end to end; the gate of N0 is connected to the drain of N1 and connected to the storage point X1; the gate of N1 is connected to the drain of N2 and connected to to the storage point X2; the gate of N2 is connected to the drain of N3 and connected to the storage point X3; the gate of N3 is connected to the drain of N0 and connected to the storage point X0; the sources of N0, N1, N2 and N3 are all grounded. The redundant bit selection circuit is composed of PMOS transistors P0, P1, P2, and P3; the drain of P0 is connected to X0, the drain of P1 is connected to X1, the drain of P2 is connected to X2, and the drain of P3 is connected to X3; the source of P0 and P2 The poles are connected together to the bit line BL; the sources of P1 and P3 are co...

Embodiment 2

[0027] like Figure 8 As shown, it also includes a redundant information latch circuit and a redundant bit selection circuit. The redundant information latch circuit is composed of PMOS transistors P0, P1, P2, and P3 connected end to end; the gate of P0 is connected to the drain of P3 and connected to the storage point X3; the gate of P1 is connected to the drain of P0 and connected to To storage point X0; the gate of P2 is connected to the drain of P1 and connected to storage point X1; the gate of P3 is connected to the drain of P2 and connected to storage point X2; the sources of P0, P1, P2, and P3 are connected Together, connect to the power supply. The redundant bit selection circuit is composed of NMOS transistors N0, N1, N2, and N3. The drain of N0 is connected to X0, the drain of N1 is connected to X1, the drain of N2 is connected to X2, and the drain of N3 is connected to X3; the sources of N0 and N2 are connected together and connected to the bit line BL; the source...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More