Method for forming finned field effect transistor

A fin-type field effect and transistor technology, applied in semiconductor devices, semiconductor/solid-state device manufacturing, electrical components, etc., can solve the problems of uneven surface of the isolation layer and damaged fin contours, and achieve good surface flatness and flatness Excellent performance and improved performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

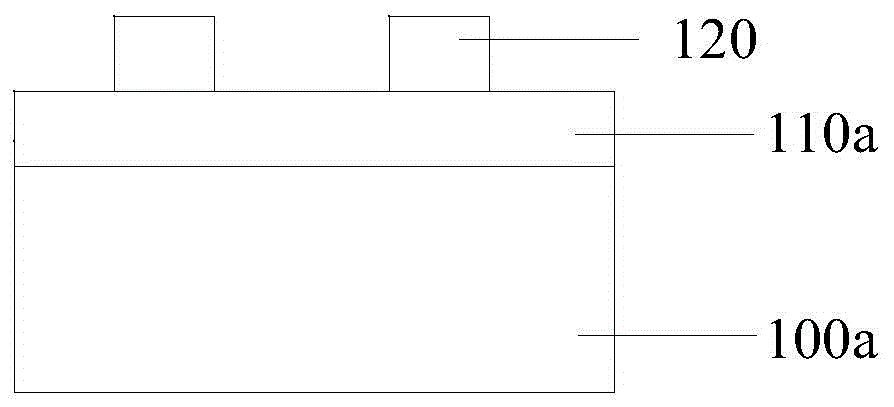

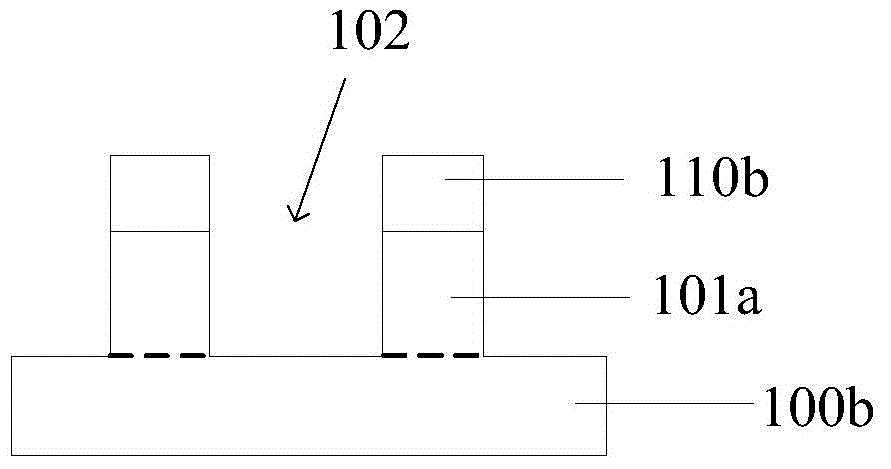

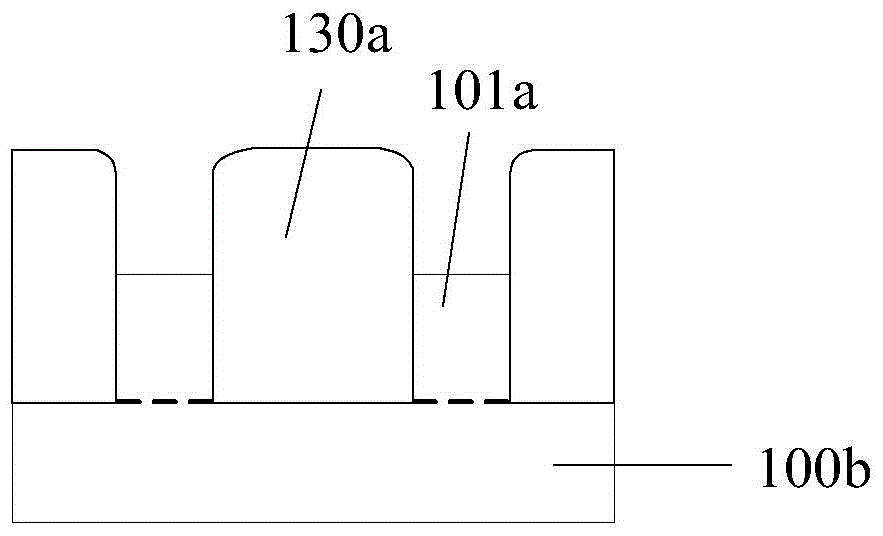

[0042] In the existing methods for forming fin field effect transistors, in the planarization process, the cap layer is usually removed first. At this time, if wet etching is used to etch the isolation material layer, the wet etching will also affect the fin portion. Etching, therefore, leads to poorer fin profile finally formed, and the poorer fin profile will affect the subsequently formed channel, ultimately affecting the performance of the transistor. If the isolation material layer is directly etched to form the isolation layer by using the SiConi etching method, since the isolation material layer has a part higher than the fin after the cap layer is removed (please refer to image 3 ), the SiConi etching method will simultaneously etch the upper surface and the exposed side of the isolation material layer (that is, the top corner of the isolation material layer is etched at 270 degrees), until the upper surface of the isolation material layer is lower than the fin. After...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com