A design method for converting pci bus to isa and apb bus

A technology of PCI bus and APB bus, which is applied in the field of bus interface conversion, can solve the problem that processors cannot access at the same time, achieve optimal design, good adaptability, and improve the effect of integration

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

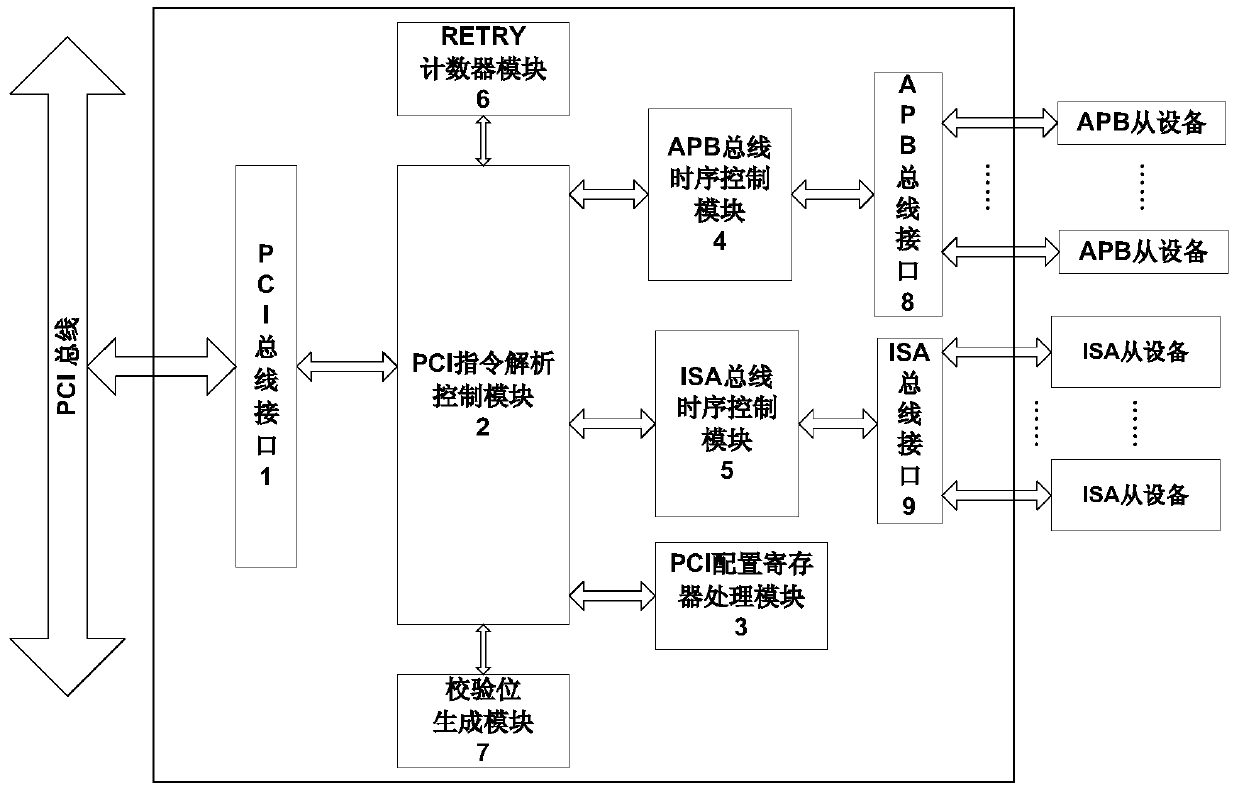

[0034] The IP core design method for converting PCI bus protocol to ISA and APB bus protocol is as follows: figure 1 As shown, the specific operation steps are as follows:

[0035] 1. PCI bus interface 1: realize the connection of PCI bus interface signals, see the specific signals figure 2 , and transmit the signal to the PCI instruction analysis control module 2 .

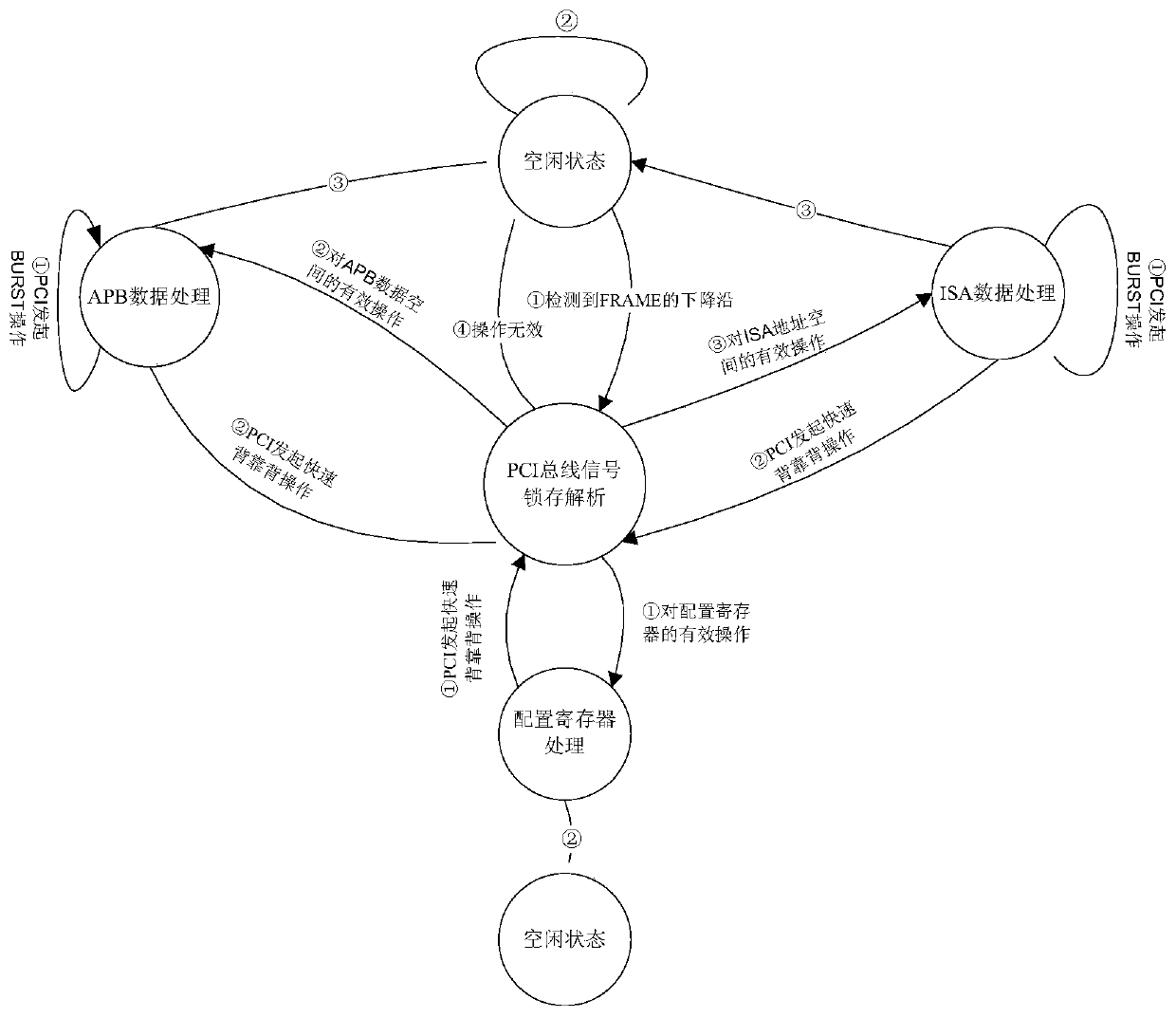

[0036] 2. PCI instruction analysis control module 2: see the state machine for its working process image 3 , first in the idle state, receive the PCI bus interface signals from PCI bus interface 1, and analyze these signals, when the falling edge of the FRAME signal is judged, enter the PCI bus signal latch analysis state, otherwise return to the idle state, and continue to wait . In the PCI bus signal latch analysis state, by analyzing the PCI bus command, determine which module is to be accessed in the following three modules. The three modules include: PCI configuration register processing module 3, APB b...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More