Inter-chip high-speed interconnection link layer design method and system

A design method and link layer technology, applied in transmission systems, electrical components, etc., can solve problems such as slow interaction speed, poor performance, and low efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0048]In order to explain in detail the technical content, structural features, achieved goals and effects of the technical solution, the following will be described in detail in conjunction with specific embodiments and accompanying drawings.

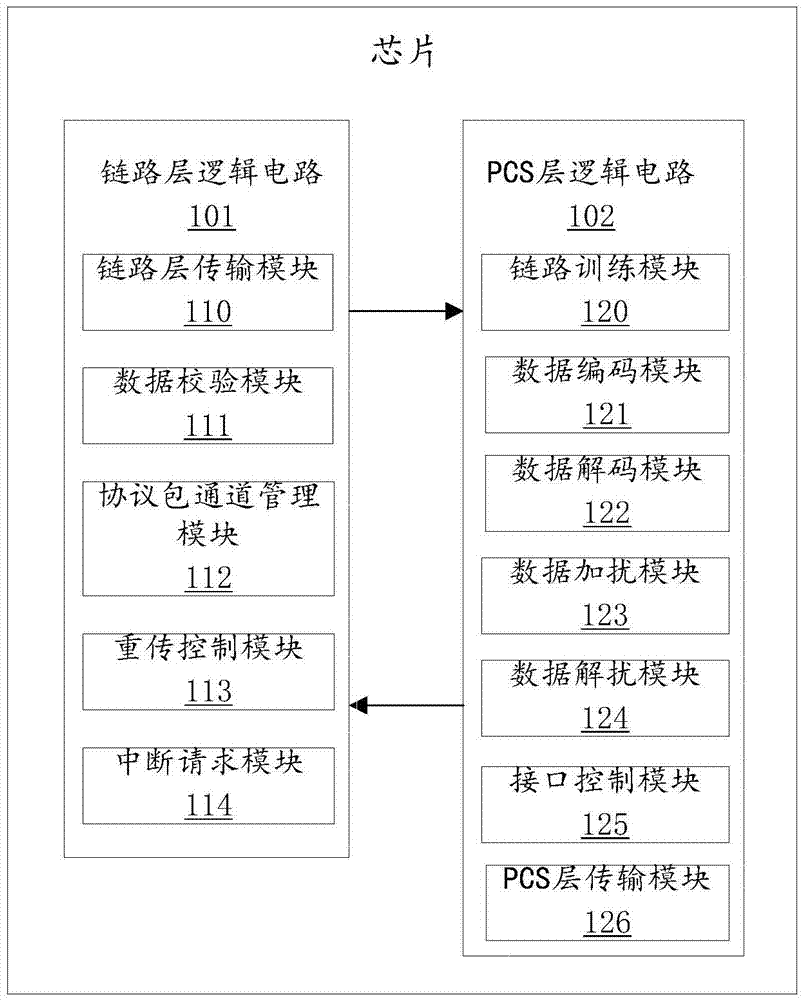

[0049] see figure 1 , is a schematic diagram of a chip of a link layer system implementing high-speed inter-chip interconnection according to an embodiment of the present invention. The chip includes a link layer logic circuit 101 and a PCS layer logic circuit 102; the link layer logic circuit 101 includes a data verification module 111, a protocol packet channel management module 112, and a link layer transmission module 110; the PCS layer The logic circuit 102 includes a link training module 120, a PCS layer transmission module 126, an interface control module 125, a data encoding module 121, a data decoding module 122, a data scrambling module 123 and a data descrambling module 124; the link layer logic circuit 101 is connected wit...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More