A Realization Method of Space Vector Modulation Based on Combination of Digital and Analog

A technology of space vector modulation and implementation method, which is applied in the field of power electronics and electric transmission, and can solve problems such as longer upgrade cycle, higher cost, and inability to directly apply research results.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

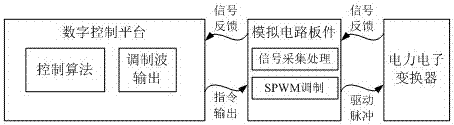

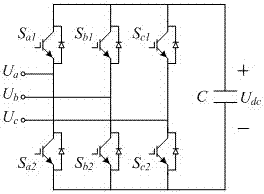

[0072] A digital-analog combined space vector modulation implementation method uses an ordinary digital controller to complete the sector judgment, vector action time calculation and switch time calculation in the SVPWM algorithm, and completes the output setting according to the carrier characteristics of the subsequent hardware circuit. Level analog circuit realizes the generation of PWM pulse.

[0073] The specific steps are:

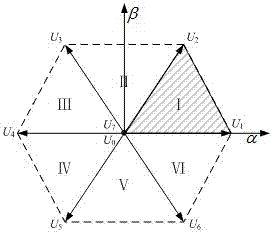

[0074] The first step is to judge the instruction space vector U OUT Sector N;

[0075] The second step is to calculate the conventional vector action time t X , t Y and zero vector action time t 0 ;

[0076] t 0 is not a regular vector, but a zero vector.

[0077] The third step is to calculate the switching point or switching time waveform t of each phase pulse cm1 , t cm2 , t cm3 ;

[0078] The fourth step is to combine the switching time waveform obtained in the third step with the carrier characteristics of the subsequent hardware cir...

Embodiment 2

[0081] A digital-analog combined space vector modulation implementation method, using a conventional controller to complete the sector judgment, vector action time calculation and switch time calculation in the SVPWM algorithm, and complete the output setting according to the carrier characteristics of the subsequent hardware circuit, and finally pass the Level hardware circuit realizes the generation of PWM pulse.

[0082] The specific steps are:

[0083] 1) Judging the command voltage space vector U OUT The sector number N.

[0084] The command voltage space vector U OUT In response to load disturbances and command changes, the power electronic converter is the command control quantity obtained by closed-loop adjustment according to the real-time parameters of the system.

[0085] The sector number N refers to the position area of any voltage space vector on the space plane. According to the angle θ between the voltage space vector and the α axis of the stationary coord...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More