Eight-tube SRAM bit cell circuit working at low voltage suitably and array of eight-tube SRAM bit cell circuit

A bit cell, low-voltage technology, applied in the field of 8-tube SRAM bit cell circuit and its array, can solve the problems of SRAM data competition, non-selected cell data interference, etc., and achieve the effect of eliminating competition and interference

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

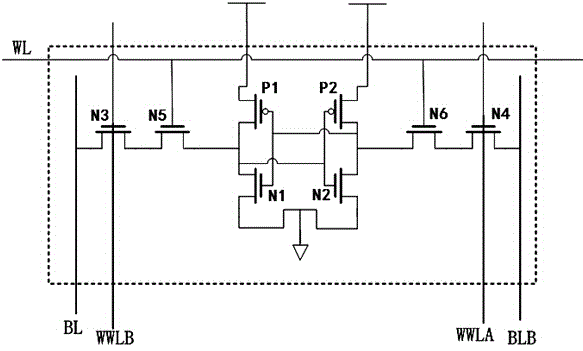

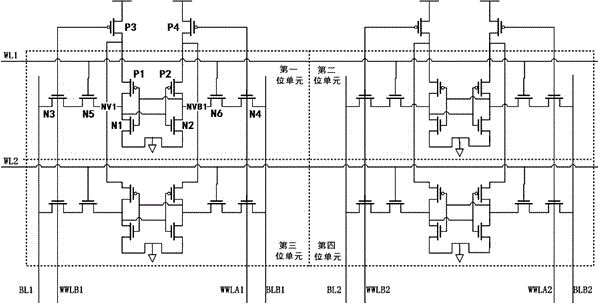

[0030] The present invention will be described in detail below with reference to the accompanying drawings and in combination with embodiments.

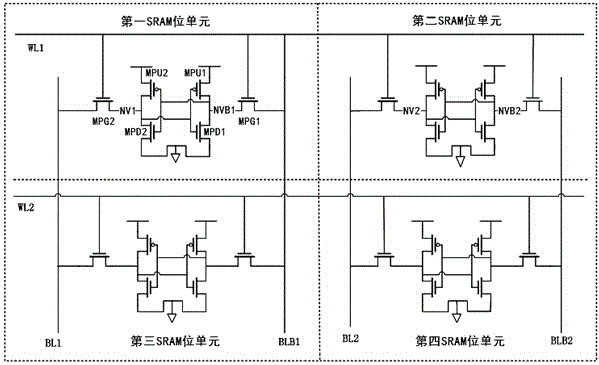

[0031] see figure 2 As shown, an 8-tube SRAM bit cell circuit suitable for low-voltage operation includes a first PMOS transistor P1, a second PMOS transistor P2, a first NMOS transistor N1, a second NMOS transistor N2, a third NMOS transistor N3, and a fourth NMOS transistor. NMOS transistor N4, fifth NMOS transistor N5 and sixth NMOS transistor N6;

[0032] Wherein, the first PMOS transistor P1 and the first NMOS transistor N1 form a first inverter, and the second PMOS transistor P2 and the second NMOS transistor N2 form a second inverter; the first The output terminal of the inverter is directly connected to the input terminal of the second inverter, and the output terminal of the second inverter is directly connected to the input terminal of the first inverter;

[0033] The sources of the first PMOS transistor P1 and the s...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More