Semiconductor device having vertical mosfet with superstructure structure and manufacturing method thereof

A manufacturing method and semiconductor technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, semiconductor/solid-state device components, etc., can solve problems such as film thickness grinding stop, PN column depth deviation, abnormal growth of type layer J6, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 approach

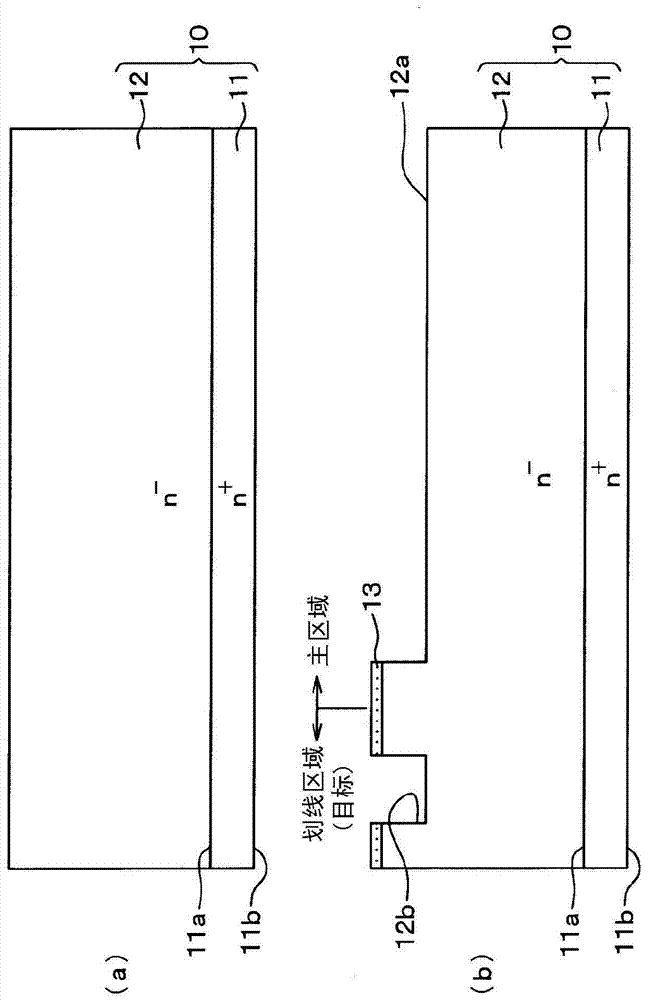

[0043] refer to figure 1 (a) to figure 2 (b) The method of manufacturing the semiconductor device according to the first embodiment of the present invention will be described. In addition, here, a semiconductor device including a trench gate type vertical MOSFET as an SJ structure vertical MOSFET will be described as an example.

[0044] 〔 figure 1 Process shown in (a)]

[0045] The following semiconductor substrate 10 is prepared: n + On the surface 11a of the type silicon substrate 11, the n corresponding to the first semiconductor layer - Type layer 12 is grown epitaxially. no + Type silicon substrate 11 is the part that functions as the drain region, and n - The n-type layer 12 has a higher concentration of impurities than the n-type. no - Type layer 12 functions as a drift layer and constitutes an n-type column among PN columns.

[0046] 〔 figure 1 Process shown in (b)]

[0047] On the surface side of the semiconductor substrate 10, at n -The oxide film 1...

no. 2 approach

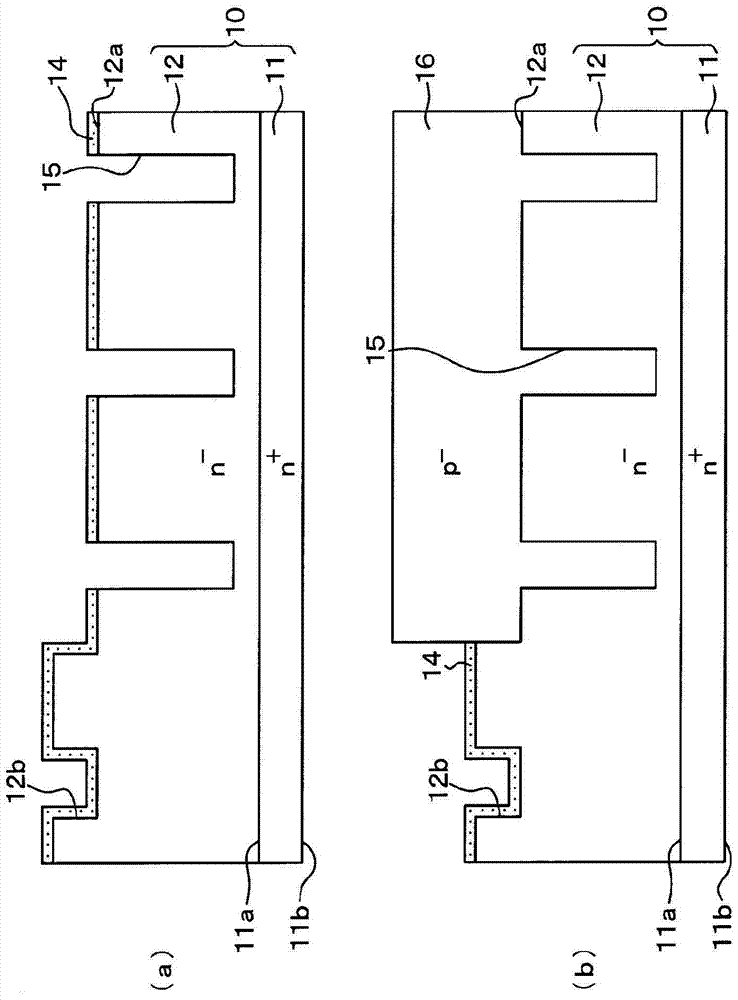

[0067] A second embodiment of the present invention will be described. In the present embodiment, the vertical MOSFET formed in the semiconductor device is changed to a planar type compared to the first embodiment, and the rest is the same as the first embodiment, so only the parts different from the first embodiment will be described.

[0068] refer to Figure 4 (a) and Figure 4 (b) A method of manufacturing the vertical MOSFET of the present embodiment will be described.

[0069] First, after performing the description in the first embodiment figure 1 (a), figure 1 (b), figure 2 (a), figure 2 After the process of (b), as Figure 4 The process of (a) is carried out as described in the first embodiment. image 3 (a) The same process. Thus, a structure is formed in which, on the surface side of the semiconductor substrate 10 , including the concave portion 12 a and the groove 15 , the n- type layer 12 on the surface so that p - Type layer 16 epitaxial growth, and ...

no. 3 approach

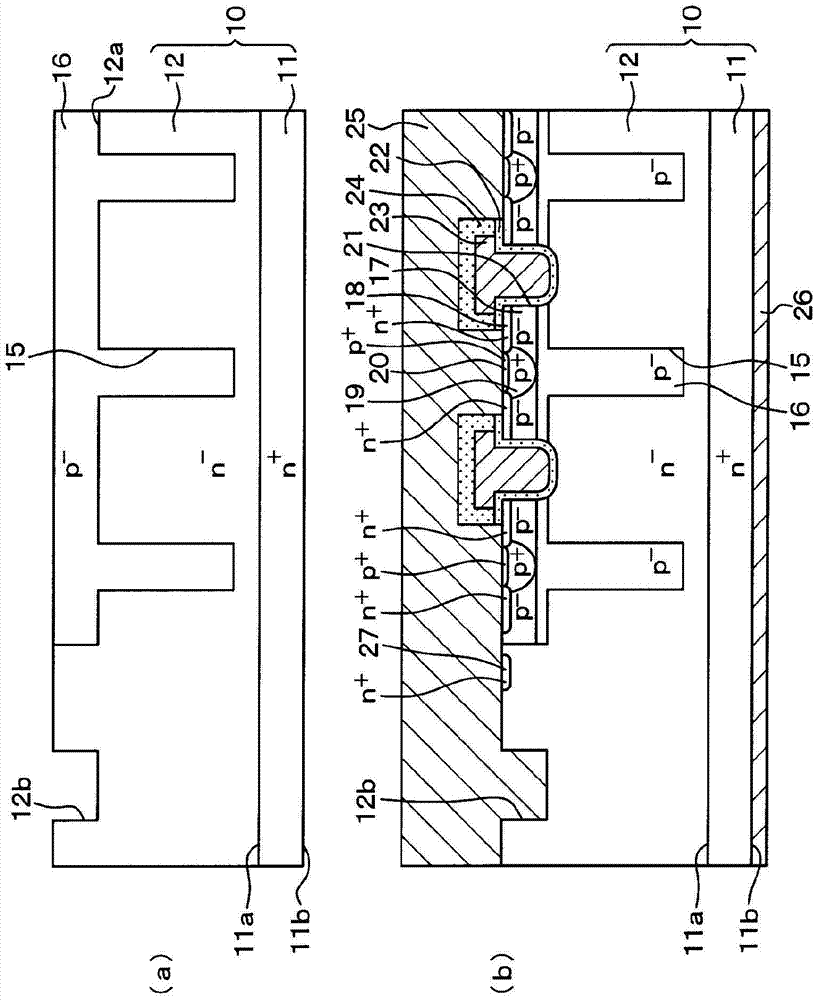

[0075] A third embodiment of the present invention will be described. The present embodiment is a manufacturing method in consideration of the peripheral withstand voltage structure of the semiconductor device compared to the second embodiment, and the rest is the same as the second embodiment, so only the differences from the second embodiment will be described.

[0076] refer to Figure 5 (a)~ Figure 7 (b) The vertical MOSFET manufacturing method of this embodiment, that is, the manufacturing method that further includes a step of forming a peripheral voltage-resistant structure in a semiconductor device including a planar vertical MOSFET having an SJ structure will be described.

[0077] First, in Figure 5 In the process shown in (a), prepare the n substrate as a substrate made of semiconductor material having a surface 11a and a back surface 11b. + On the surface 11a of the type silicon substrate 11, the n corresponding to the first semiconductor layer - The substrat...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More