Array substrate and restoration method, test method and manufacture method thereof, and display apparatus

An array substrate and substrate technology, applied in static indicators, semiconductor/solid-state device manufacturing, organic semiconductor devices, etc., can solve problems such as black lines on the display screen, complex production processes, and the inability to quickly and easily repair data line breaks, etc., to achieve The repair process is simple and easy to achieve

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

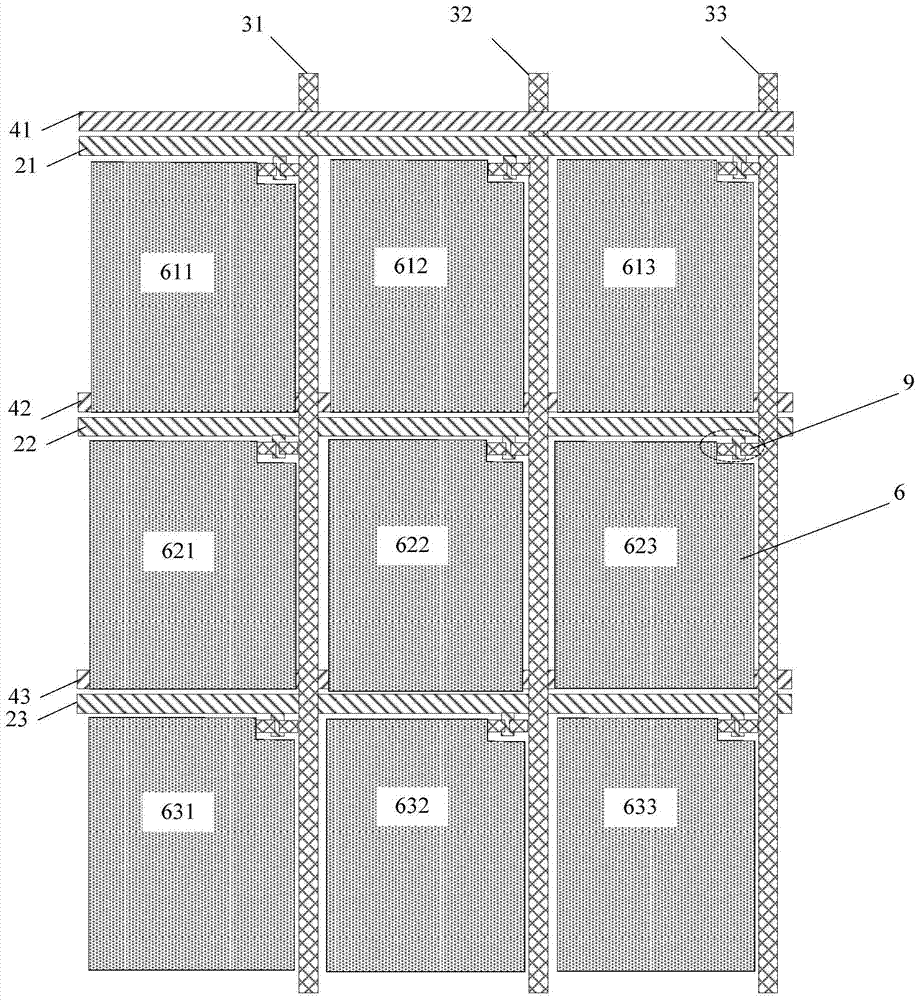

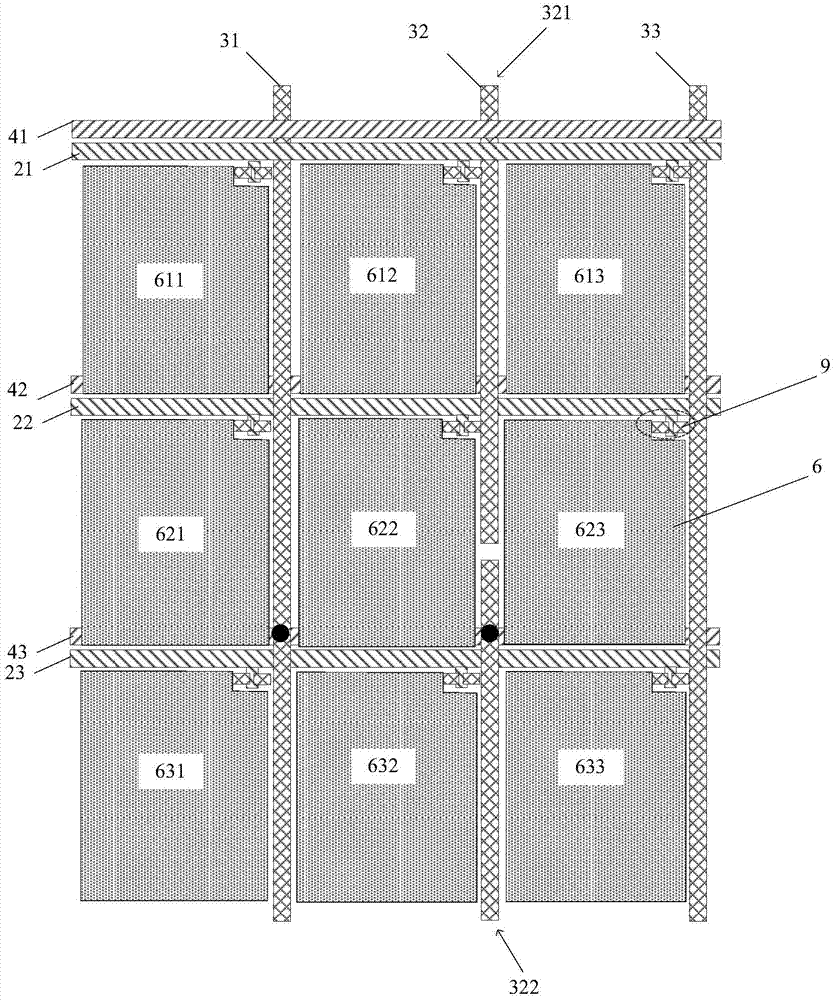

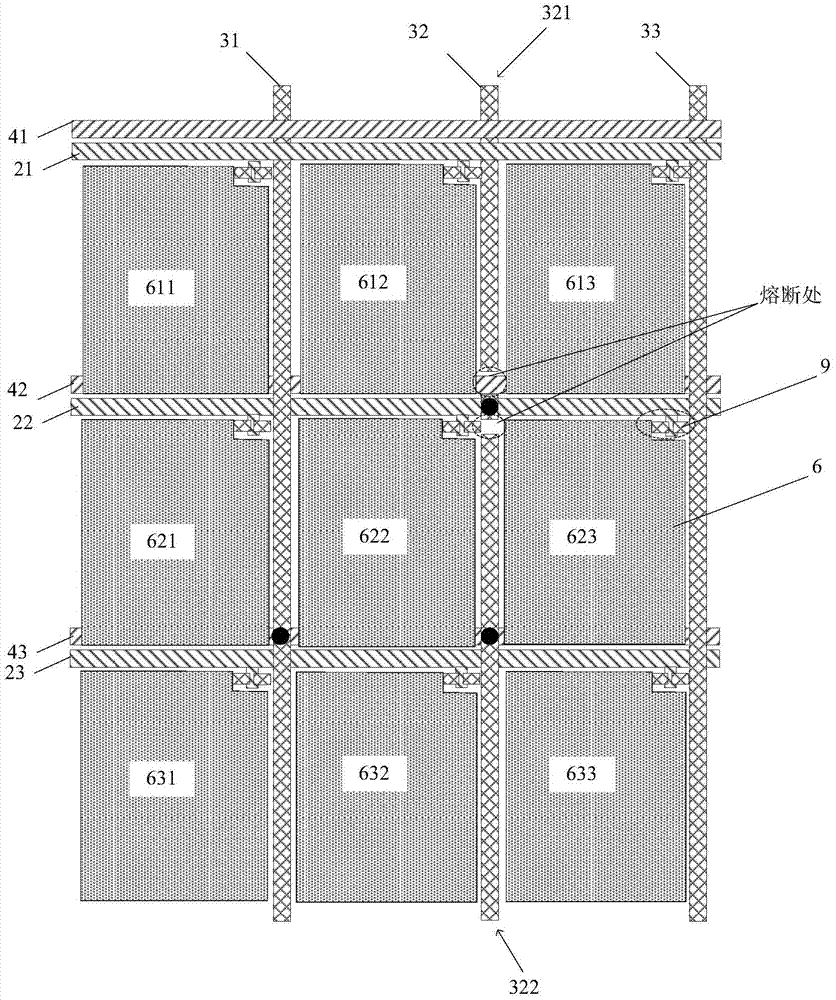

[0033] Embodiment 1 of the present invention provides the structure of the array substrate, which can be referred to figure 1 and 4 , including: base1( figure 1 Not shown in ), the gate line pattern and data line pattern formed on the substrate 1, each row of gate lines 21, 22, 23 in the gate line pattern and each column of data lines 31, 32, 33 in the data line pattern perpendicularly intersect , dividing the array substrate into a plurality of pixels, and further including a spare line pattern formed on the same layer as the gate line pattern, the spare line pattern including a plurality of spare lines 41, 42, 43 parallel to the gate lines in the gate line pattern, A spare line is formed at the position of each row of pixels, and there is a vertical overlapping area between the spare line and the data line connected to each pixel in the row. In addition, a gate insulating layer 5 for isolating the gate line pattern, the spare line pattern and the data line pattern is also ...

Embodiment 2

[0044] In the H-ADS array substrate in the prior art, since the pixel electrodes are fabricated under the common electrode layer, the test terminals cannot be connected to the pixel electrodes, and corresponding electrical performance tests cannot be realized. In order to overcome such problems, Embodiment 2 of the present invention provides a new type of H-ADS array substrate.

[0045] refer to Figure 5 and 6 As shown, the array substrate provided in Embodiment 2 is an H-ADS (High Aperture Ratio Edge Field Switching) substrate. Compared with the array substrate provided in Embodiment 1, it also includes: a passivation layer formed on the pixel electrode pattern Pattern 7 and the common electrode pattern 8 formed on the passivation layer pattern 7; each spare line pattern has a vertical overlapping area with the pixel electrode block above it, and the passivation layer pattern 7 is formed at a position corresponding to the vertical overlapping area There is a positioning ho...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More