Double-DA synchronous sampling device

A technology of synchronous sampling and sampling unit, applied in the field of communication, can solve the problems of reduced reliability, inconsistency, and voltage signals are easily interfered by external noise, and achieves improved debugging and usability, strong portability, and increased reliability. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

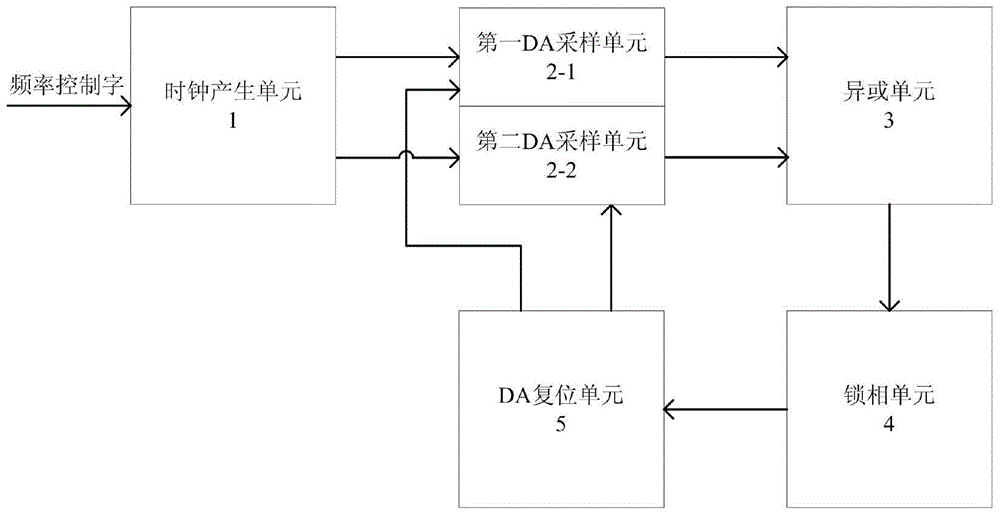

[0019] refer to Figure 1 to Figure 5 , the present invention includes a clock generation unit 1 , a first DA sampling unit 2 - 1 , a second DA sampling unit 2 - 2 , an exclusive OR unit 3 , a phase locking unit 4 and a DA reset unit 5 . figure 1 It is a principle block diagram of the present invention, and the examples are according to figure 1 Connect the lines. The clock generation unit 1 generates a clock signal according to the frequency control word input from the outside, and divides the clock signal into two channels and sends them to the first DA sampling unit 2-1 and the second DA sampling unit 2-2 in one-to-one correspondence; the first DA sampling unit 2-1 The sampling unit 2-1 and the second DA sampling unit 2-2 each generate a 4-way frequency-divided clock signal, and send them to the exclusive OR unit 3; After the XOR signal is processed, an XOR signal is generated and sent to the phase-locking unit 4; the phase-locking unit 4 phase-locks the XOR signal and se...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More