Self-aligned double patterning method and fin field effect transistor manufacturing method

A double patterning and fin field effect technology, which is applied in the production of fin field effect transistors and the field of self-alignment double patterning, can solve the problem of shape asymmetry, damage the electrical performance of semiconductor devices, and affect the pattern to be etched 21 Shape and other problems, to achieve the effect of improving electrical performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

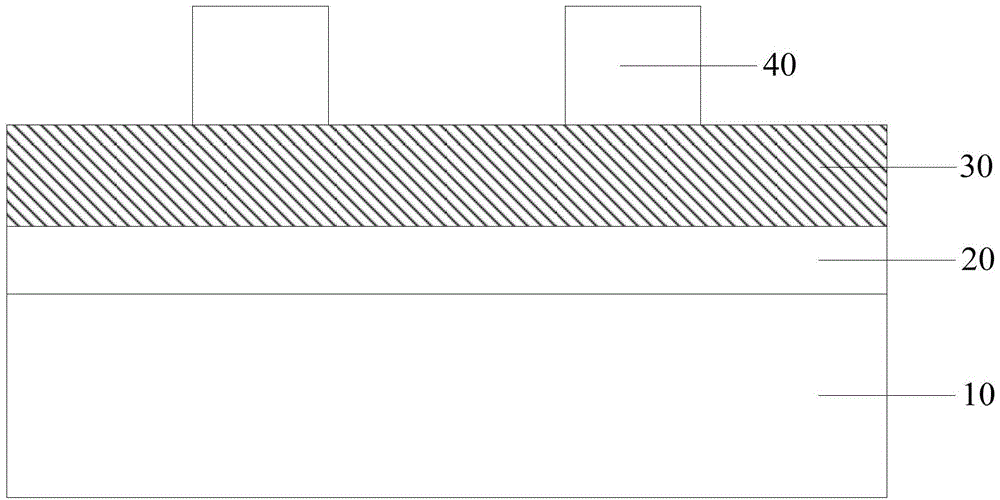

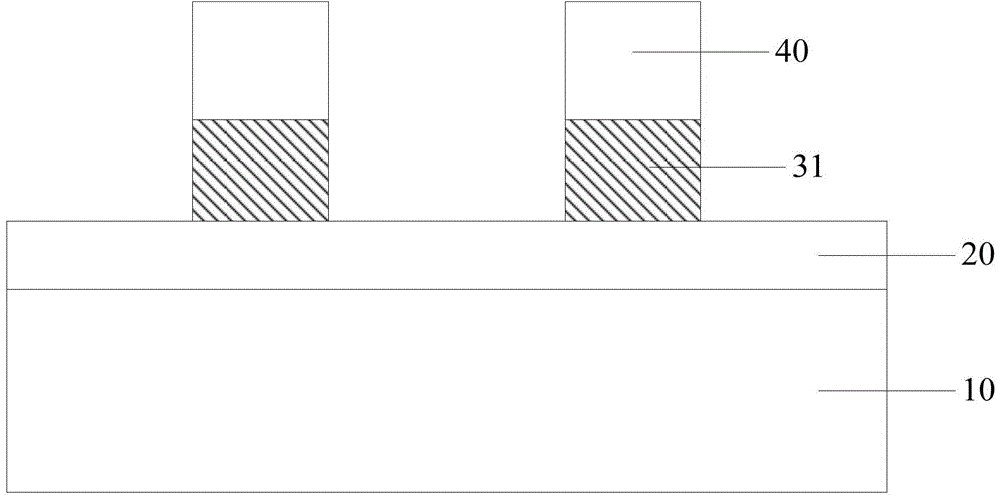

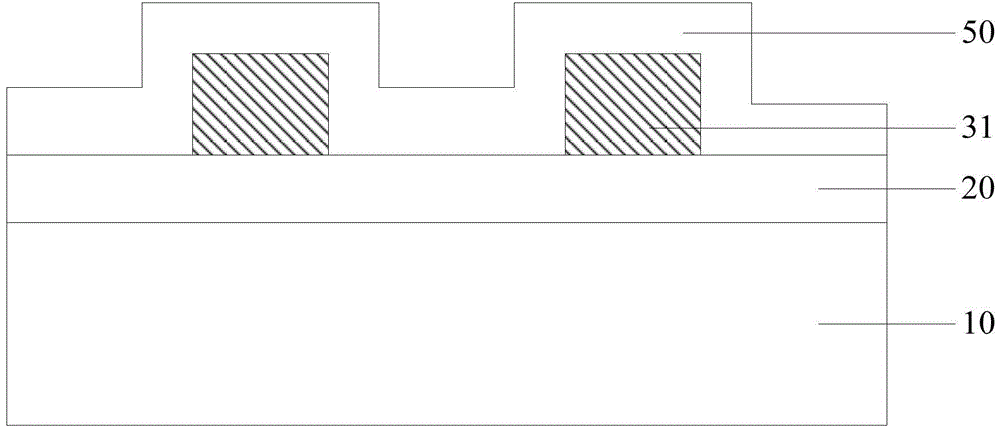

[0029] As described in the background art section, after the prior art SADP technology is used to etch the material layer to be etched, the etching mask obtained by the sidewall process (ie, sidewall) has a pyramidal and asymmetrical appearance. Specifically, the sidewall of the sidewall on the side close to the sacrificial layer pattern is perpendicular to the surface of the semiconductor substrate, and the shape of the sidewall on the side far from the sacrificial layer pattern is arc, so that the sidewalls on both sides of the sidewall The profile shape is different. Therefore, when the material layer to be etched is etched using such sidewall spacers as a mask, the topography of the sidewalls of the material layer to be etched corresponding to both sides of the sidewall spacers are different, which will affect the electrical performance of the semiconductor device to be subsequently formed.

[0030] In view of the above-mentioned problems, the present invention provides a sel...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com