Fin field effect transistor and method of forming the same

A fin-type field effect and transistor technology, which is applied in the direction of transistors, semiconductor devices, electric solid-state devices, etc., can solve the problems of increasing the difficulty of the gate structure, and achieve the effect of reducing the difficulty of the process and reducing the process steps

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

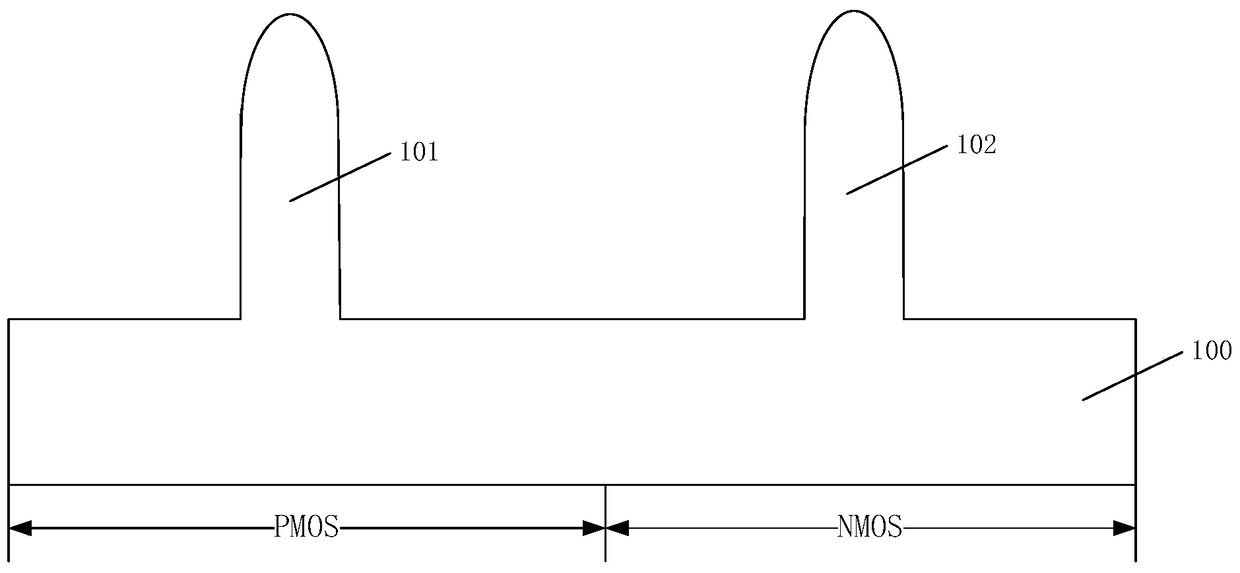

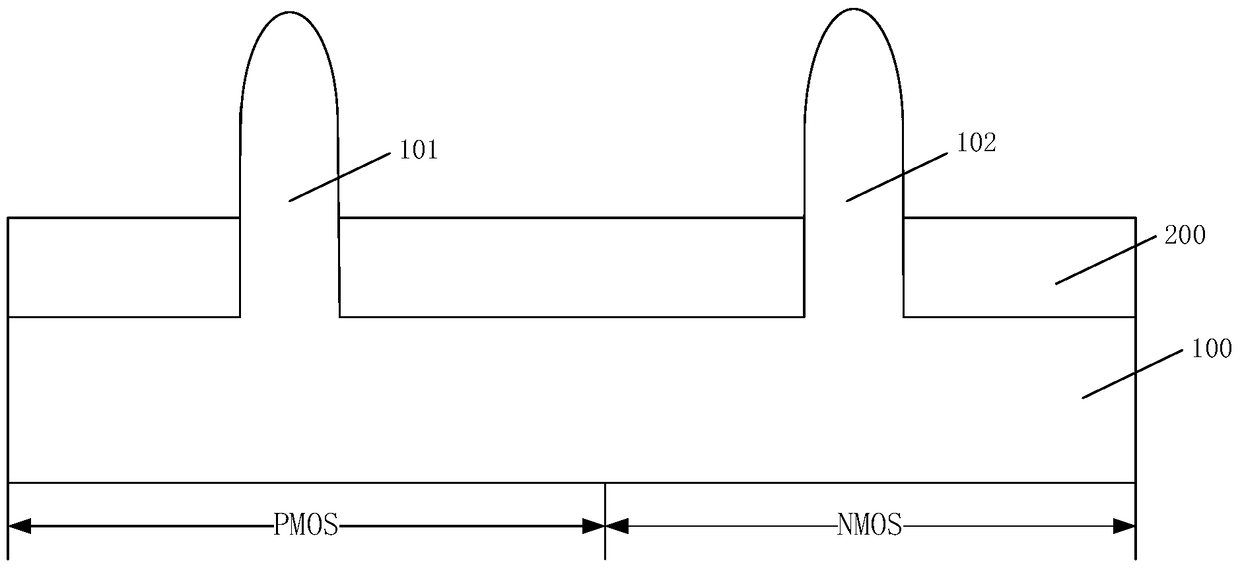

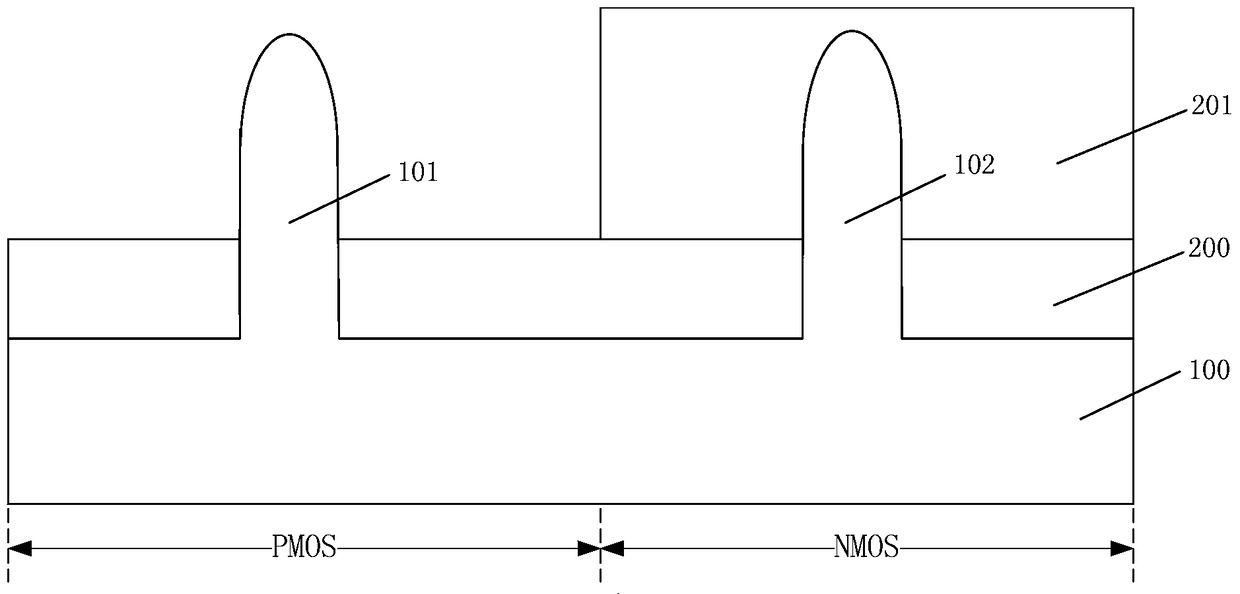

[0031] As mentioned in the background technology, the steps of forming fin field effect transistors in the prior art are relatively complicated. Since the gate work function required by the P-type fin field effect transistor and the N-type fin field effect transistor is different, the P-type fin field effect transistor The fin field effect transistor and the n type fin field effect transistor often need to use work function layers formed of different materials, so that the gate structures of the p type fin field effect transistor and the n type fin field effect transistor need to be formed respectively, which requires more Complicated process steps, and because the fin field effect transistor has a three-dimensional structure, the increase in process steps further increases the difficulty of forming the fin field effect transistor.

[0032] In the embodiment of the present invention, a work function adjustment layer is formed on the first fin of the PMOS region, and the work fu...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More