Capacitance compensation circuit and analog-digital converter for NMOS input transistor of operational amplifier

An operational amplifier, capacitance compensation technology, applied in the direction of analog-to-digital converters, etc., can solve problems such as errors

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

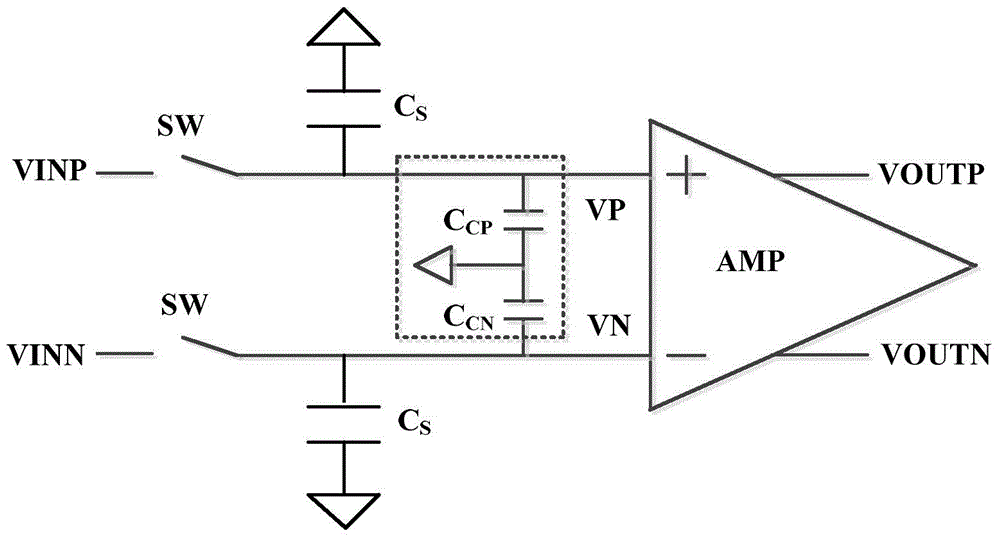

[0023] In order to make the technical means, creative features, goals and effects achieved by the present invention easy to understand, the present invention will be further described below in conjunction with specific illustrations.

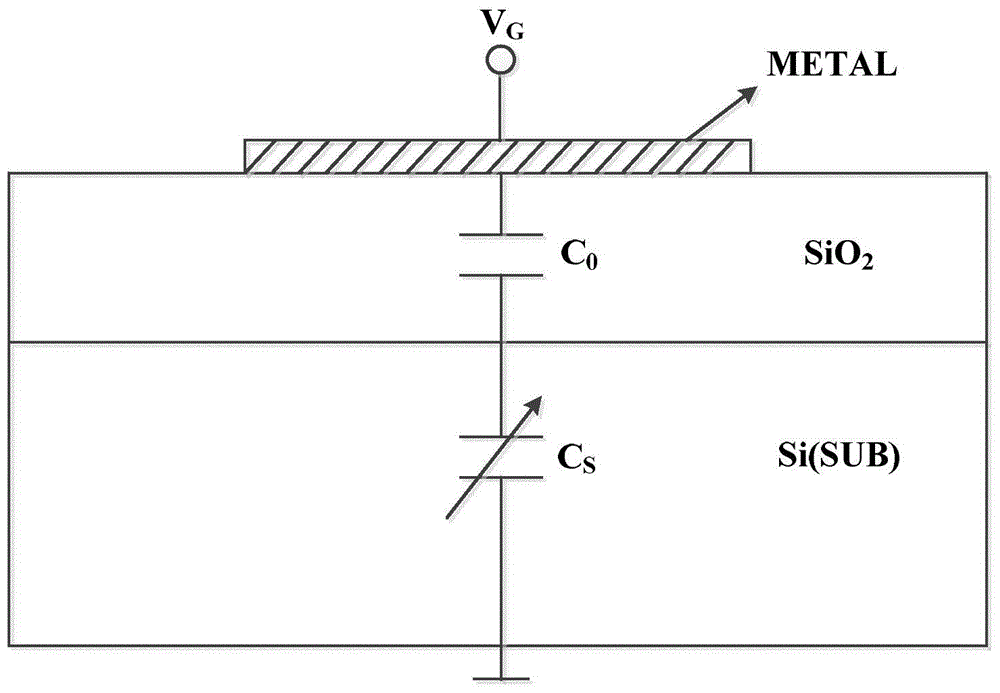

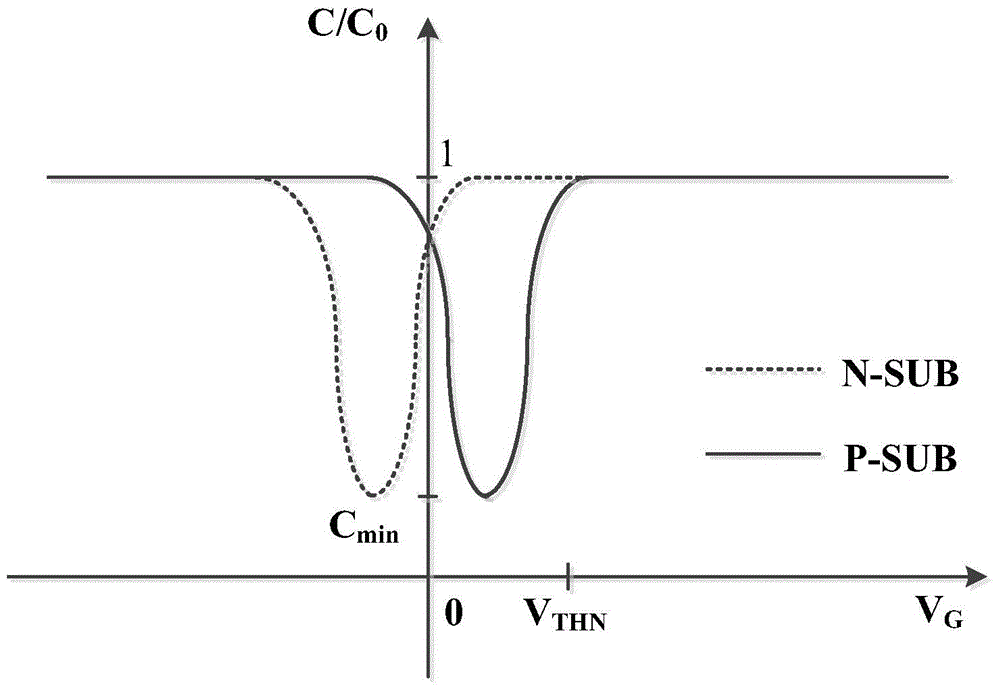

[0024] Please refer to Figure 6 and Figure 7 As shown, the present invention provides a capacitance compensation circuit for an operational amplifier NMOS input transistor, the capacitance compensation circuit is a deep N-well NMOS transistor NM1, and the deep N-well NMOS transistor NM1 includes a deep N-well DNW, which is the same as the deep N-well NMOS transistor NM1. The first N well NW1 and the second N well NW2 connected by the N well DNW, the first N well NW1 and the second N well NW2 are provided with an N+ implantation region to lead out the N well potential, the deep N well, the second N well NW2 A P well P-WELL is surrounded by an N well and a second N well, and the P well P-WELL is used as the substrate of the deep N well NMOS tra...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More