Field programmable gate array (FPGA) based high-speed analog-digital converter (ADC) synchronous acquisition system

A synchronous acquisition and high-speed technology, applied in the direction of physical parameter compensation/prevention, analog-to-digital converter, etc., can solve the problems that the sampling rate of the signal acquisition board is not high enough, the synchronization index cannot meet the requirements of broadband signal acquisition and processing, and achieve wide applicability Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0026] The present invention will be further described below in conjunction with the accompanying drawings.

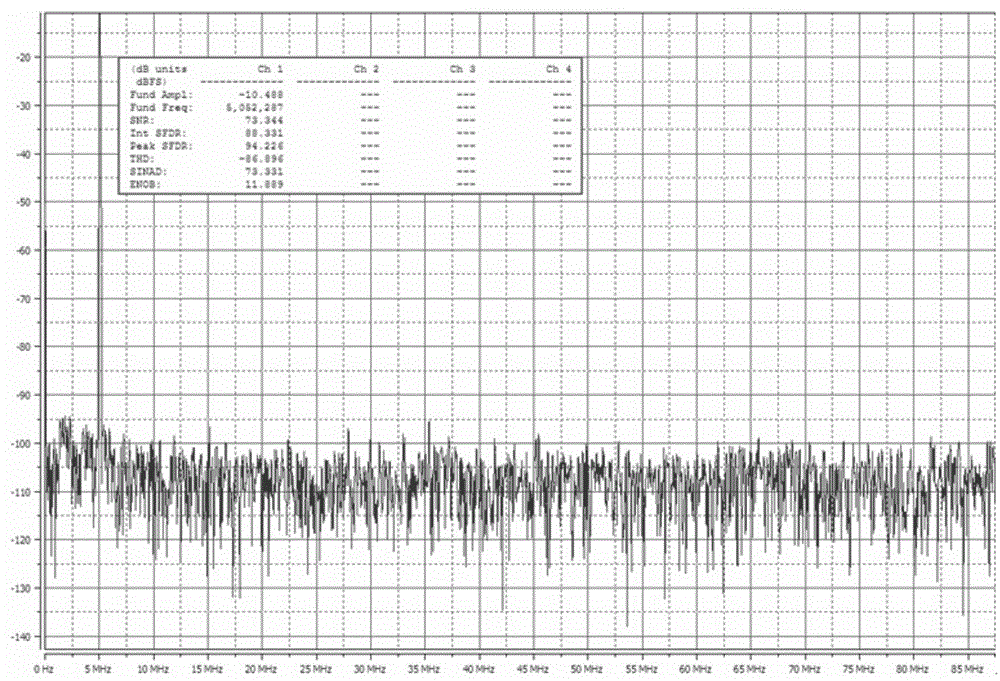

[0027] This patent implements a high-speed synchronous acquisition system with a 2-way sampling rate of 500MHz and a quantization bit width of 14bit through an FPGA-based high-speed acquisition circuit design. It achieves high synchronization, SNR and SFDR performance, and the board is designed based on FMC structure, which has wide applicability.

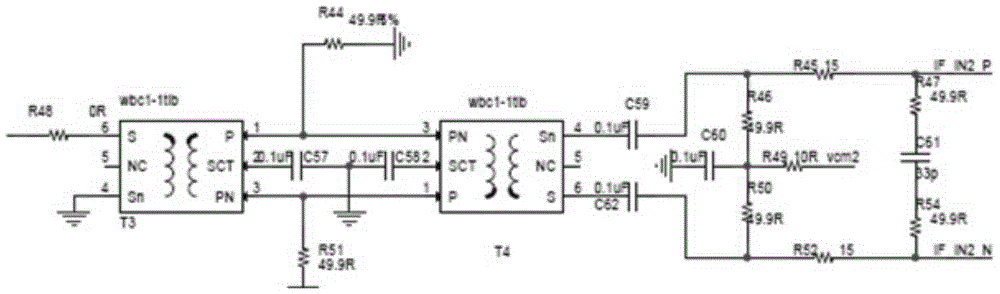

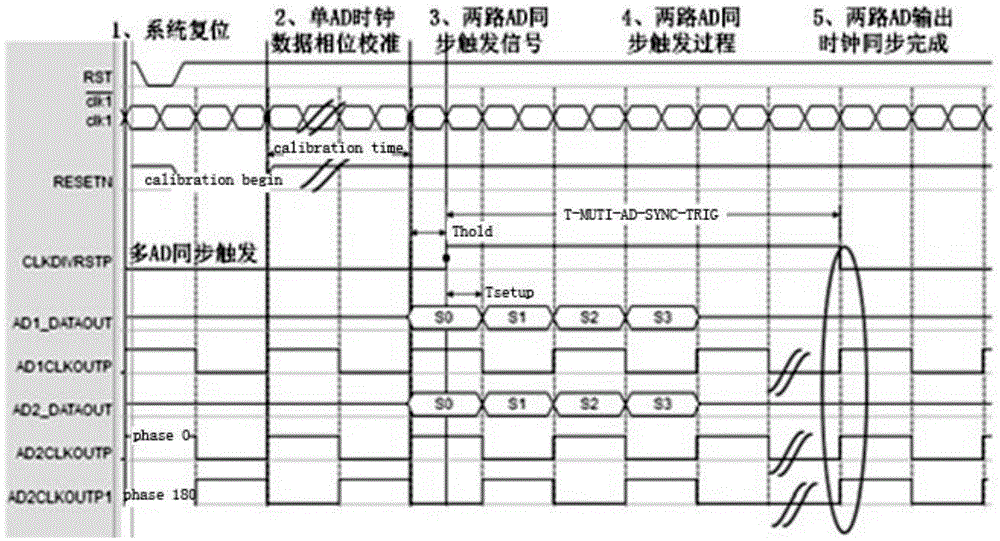

[0028] Such as figure 1 As shown, the design is based on multi-channel ultra-low jitter high-speed clock generation circuit, high-speed ADC front-end signal conditioning circuit, multi-channel ADC synchronization technology, high-speed ADC low-noise power supply design technology and layout technology, FPGA-based signal processing platform design technology, etc. , to complete the high-speed synchronous data acquisition of 2 broadband signals. The multi-channel high-speed synchronous clock circuit generates multiple low-j...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More