Architecture Design Method of Heterogeneous Multi-core SoC

An architecture, heterogeneous multi-core technology, applied in the field of computer applications, can solve problems such as lack of theoretical methods

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0008] The architecture design method of the heterogeneous multi-core SoC provided by the embodiment of the present invention will be described in detail below with reference to the accompanying drawings.

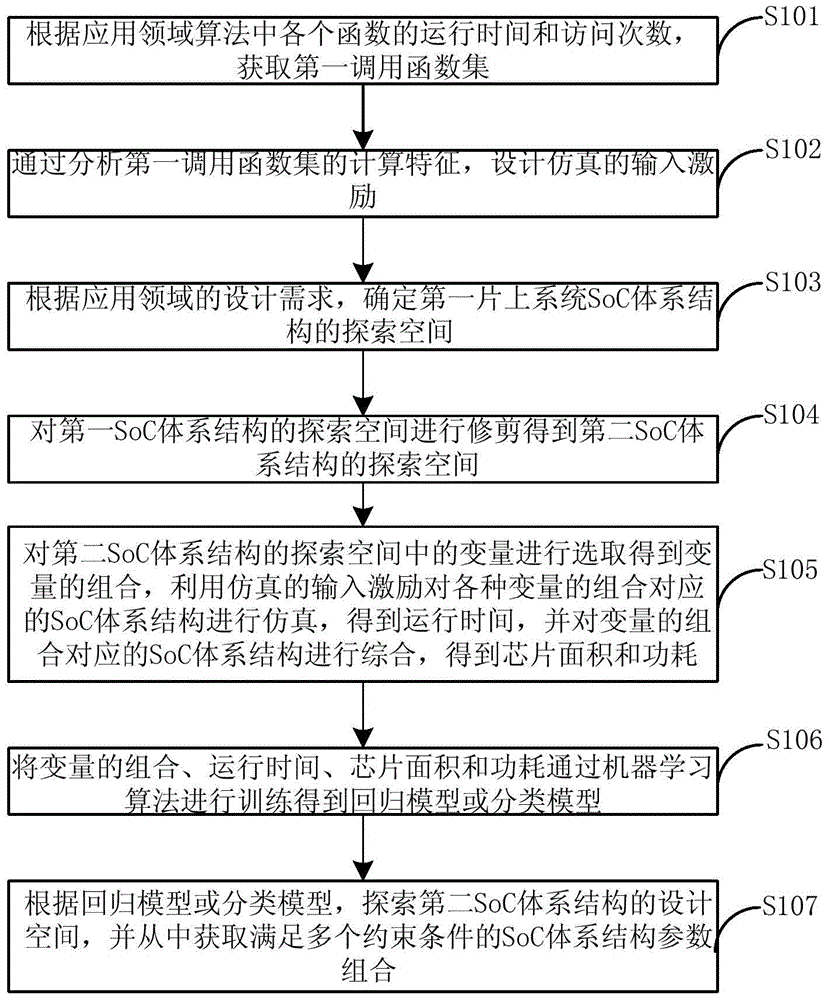

[0009] figure 1 It is a flowchart of a heterogeneous multi-core SoC architecture design method provided by an embodiment of the present invention.

[0010] refer to figure 1 , in step S101, according to the running time of the function and the number of visits to obtain the first set of calling functions.

[0011] Here, the first call function set is a function with a large amount of computation, a long computation time, or a large number of calls.

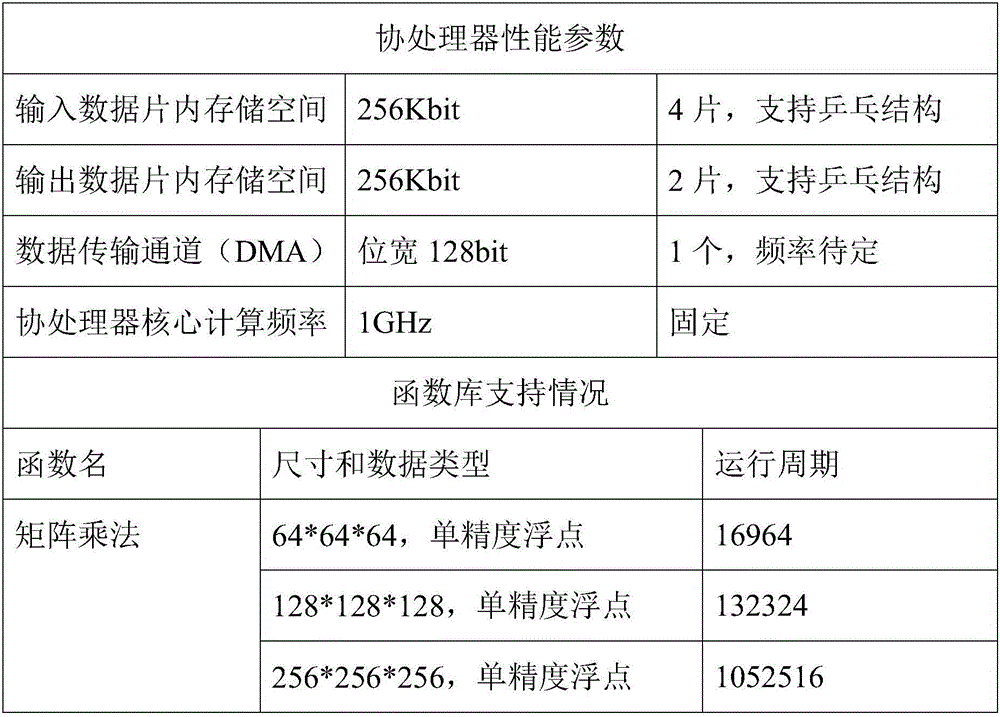

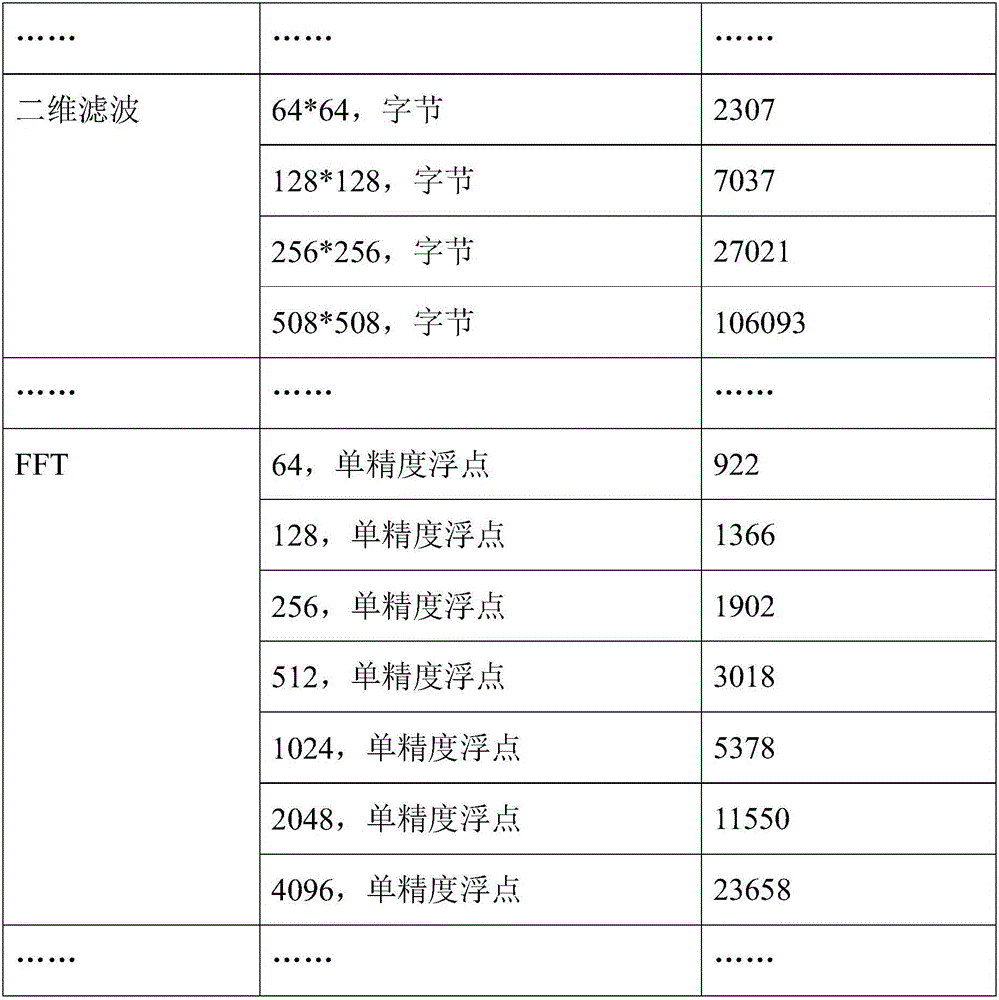

[0012] Specifically, use the gprof software of Linux to dynamically analyze the call situation of each function, and determine the function with a large amount of calculation in the program. Referring to the consumption time table of each function shown in Table 1, select the 15 functions that consume the most time among the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More