A High-Level Synthetic Scheduling Method Based on Linear Delay Model

A high-level synthesis and scheduling method technology, applied in the field of hardware circuit structure design, can solve the problems of inability to meet the development needs of integrated circuit design, high algorithm time complexity, poor overall scheduling effect, etc., to reduce the algorithm time complexity, meet the Development requirements, effects of reduced accuracy

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

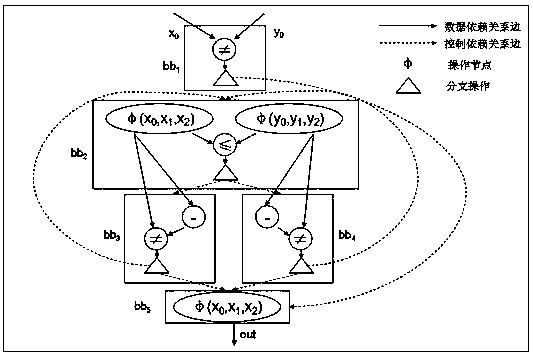

[0047] First, the control data flow diagram is described, figure 1 It is a schematic diagram of the control data flow graph. The control data flow graph is the execution operation object of the scheduling algorithm. It is a directed graph that includes data operations, data dependencies, control jumps and other related information input into the circuit description of the system. The control data flow graph can be divided into two parts: nodes and edges, where nodes include operation nodes and basic blocks. An operation node refers to a set of operation operations appearing in the input circuit description, and according to different control relationships, one or more sets of operation nodes can constitute a basic block. In the figure, the solid line represents the data dependency edge, the dotted line represents the control dependency edge, each ellipse represents an operation node, and each box represents a basic block. Every circuit description can be represented by such a...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More