Chip packaging structure with package and realization process

A technology of chip packaging structure and packaging structure, which is applied in the direction of electrical components, electric solid devices, circuits, etc., can solve problems such as delamination damage, moisture absorption, etc., and achieve the effect of improving protection level, product yield rate, and reliability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

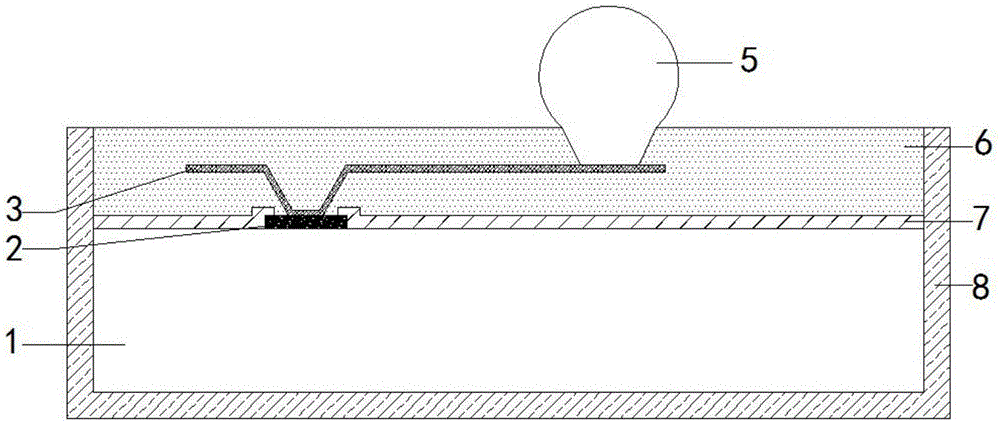

[0031] The present invention proposes a chip packaging structure with encapsulation and its realization process, such as figure 1 As shown, the packaging structure includes a chip unit (9) and a first insulating layer (6) and a second insulating layer (8) covering the chip unit, and the bottom and both sides of the chip unit (9) are covered by the second insulating layer (8). ) package, the top of the chip unit (9) is wrapped by the first insulating layer (6); the chip unit (9) includes a silicon chip (1) and an oxide layer (7) containing an integrated circuit function layer, and contains an integrated circuit function The silicon wafer (1) of the first layer is located below the chip unit (9); the oxide layer (7) is placed above the silicon wafer (1) containing the integrated circuit function layer; there are several PINs in the oxide layer (7) Pin (2), the PIN pin (2) is a metal pin.

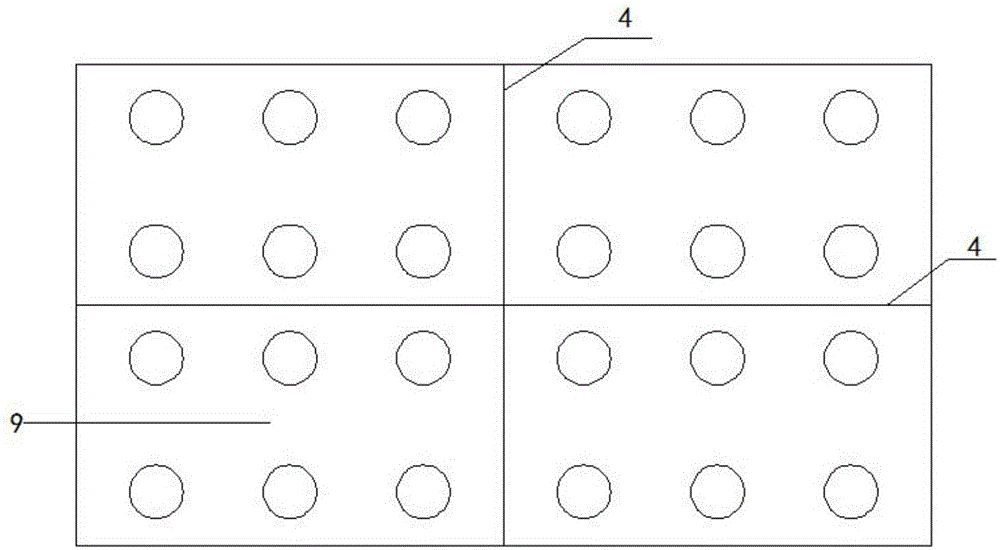

[0032] Such as Figure 1~2 As shown, the process flow for forming a six-sided covering s...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com