High-speed parallel processing architecture for data center

A parallel processing, high-speed serial interface technology, applied in the field of data processing, can solve the problems of loss of important information and discontinuity of vibration data collection, and achieve the effect of improving processing capacity and reducing system scheduling delay.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0014] In order to make the above objects, features and advantages of the present invention more comprehensible, the present invention will be further described in detail below in conjunction with the accompanying drawings and specific embodiments.

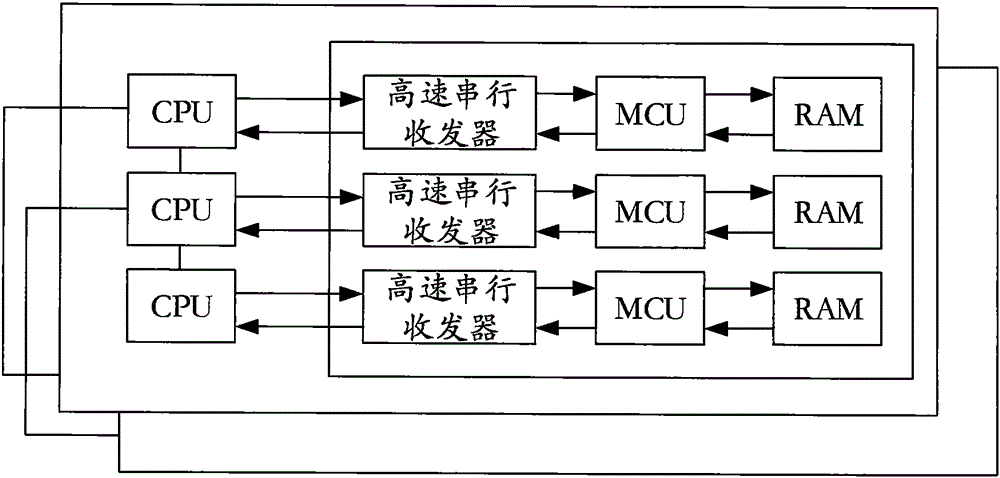

[0015] Such as figure 1 As shown, it is a schematic structural diagram of a high-speed parallel processing architecture of a data center provided by an embodiment of the present invention, including multiple processing single boards, and one processing single board includes: at least two transceivers, at least one FPGA programmable logic chip and At least two processor CPUs, the CPUs are connected with the FPGA chip through the CPU high-speed serial interface, and the FPGA chip is internally provided with a plurality of high-speed serial transceiver cores and corresponding coprocessor MCUs; A plurality of embedded memories corresponding to each coprocessor MCU are embedded; the embedded memories are configured in a dual-port mode ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More