A design method of asynchronous sequential circuit based on ams

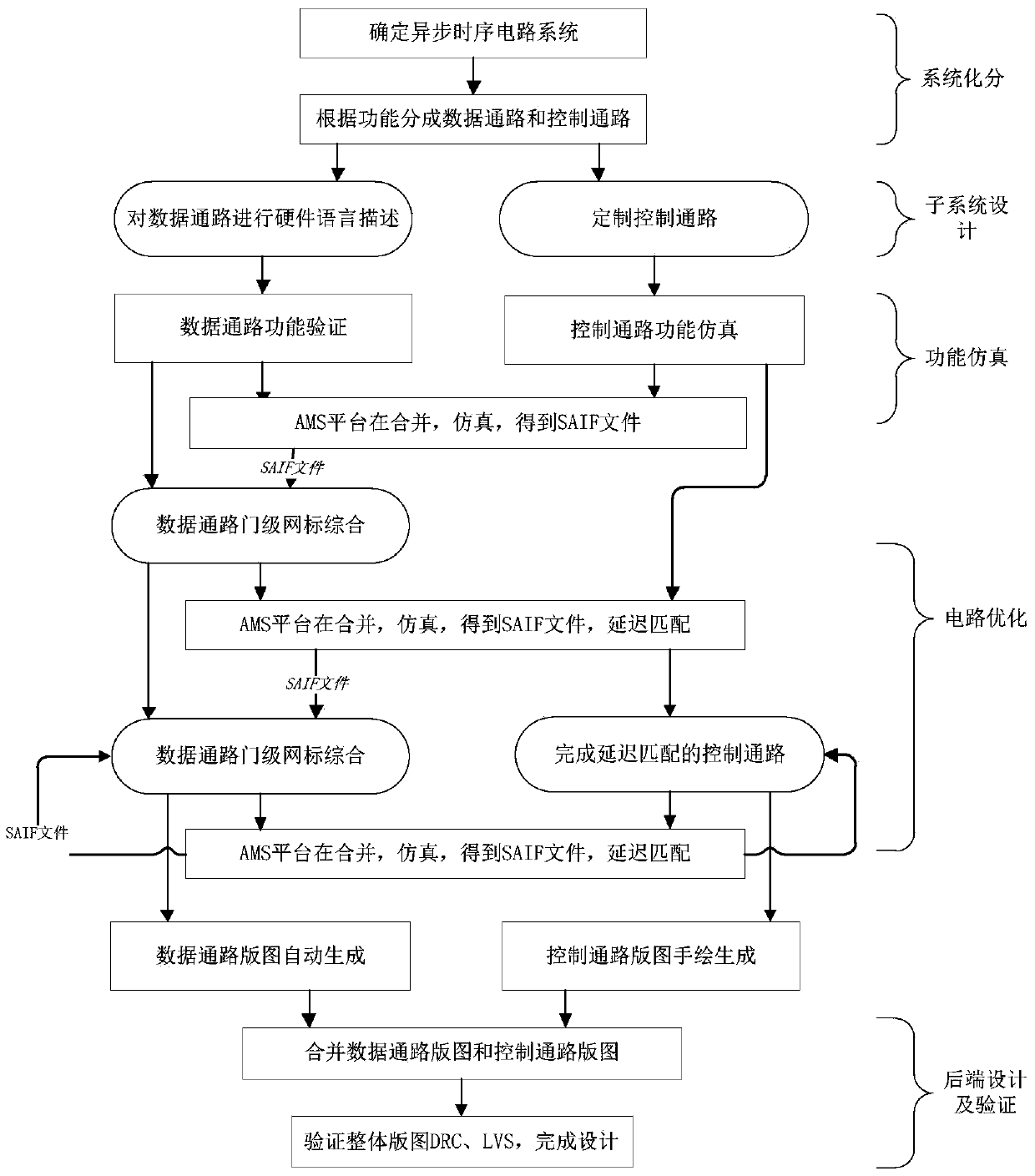

A technology of asynchronous sequential circuit and design method, which is applied in computing, electrical digital data processing, special data processing applications, etc., can solve the problems of interface circuit design difficulties and inability to optimize the circuit as a whole, so as to facilitate design optimization, reduce simulation time and Difficulty, the effect of solving compatibility problems

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

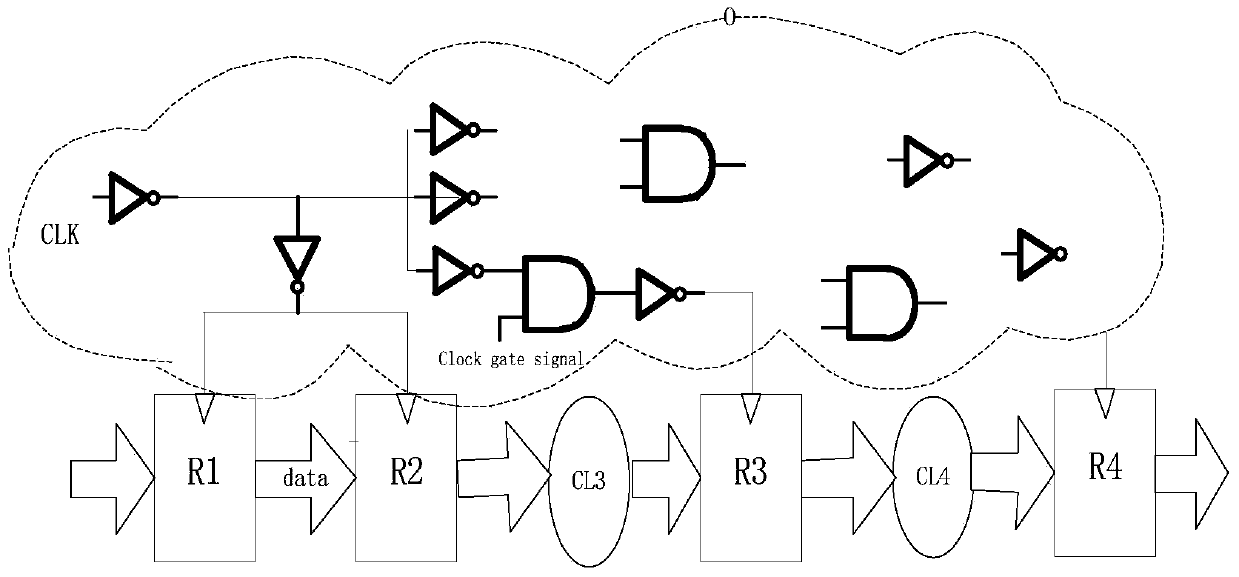

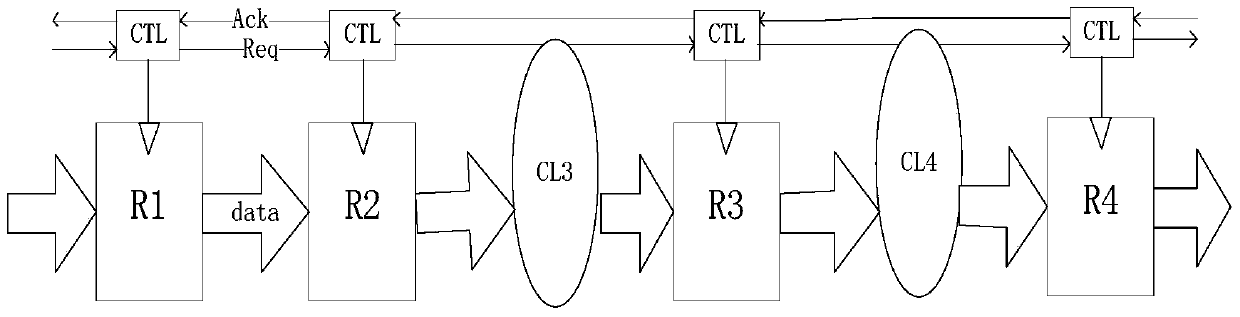

[0020] Taking the 32-bit asynchronous multiplier as an example, this design method is introduced in detail. It should be pointed out that the simulation tools called by the AMS simulation platform built by this method are: the transistor-level circuit simulation tool Nano Sim and the behavior-level and gate-level circuit simulation tool VCS. The simulation platform can simulate transistor-level circuits and behaviors and gate-level circuits at the same time, and generate analog waveforms and digital waveform files, as well as overall power consumption files.

[0021] The multiplier used in this example adopts Booth coding, completes the addition of partial products through the Wallace tree, and finally obtains the operation result. The multiplication structure can make good use of pipeline control data flow. At the same time, the asynchronous communication protocol selected in this example is a four-phase monorail bundled data protocol, and its design process is as follows ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More