TMR-based implementation and fault injection simulation platform and simulation method

A technology of fault injection and simulation methods, applied in special data processing applications, instruments, electrical digital data processing, etc., can solve problems such as increasing the difficulty of fault-tolerant system design

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

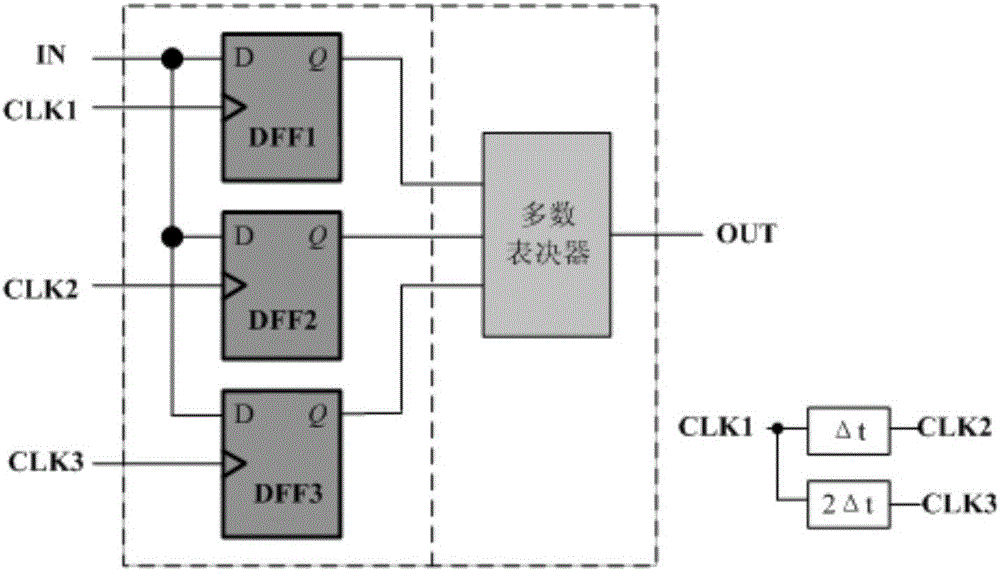

Method used

Image

Examples

Embodiment Construction

[0044] The present invention will be further described in detail below in conjunction with specific embodiments, which are explanations of the present invention rather than limitations.

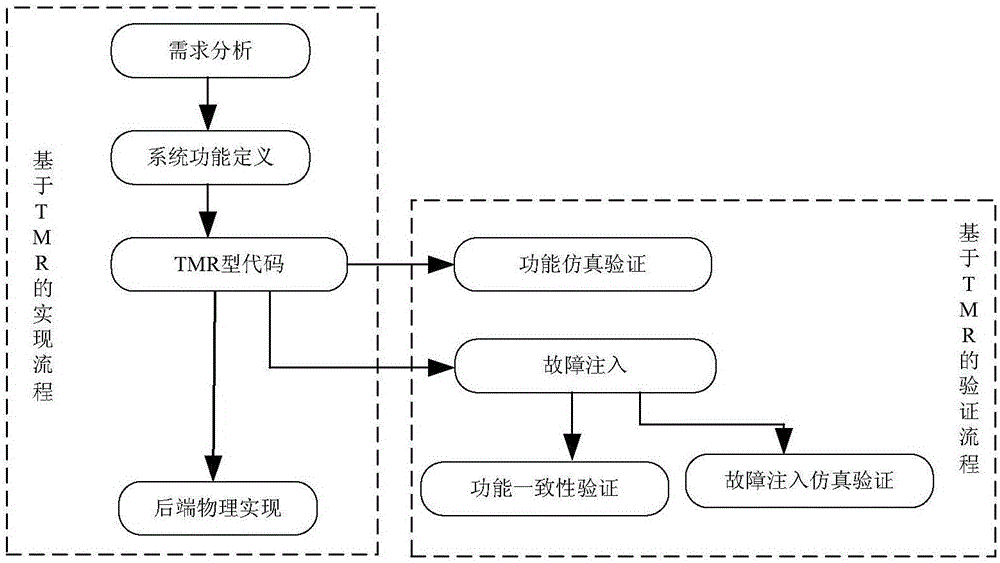

[0045] The unified TMR-based implementation and fault injection simulation platform of the present invention, as attached Figure 5 As shown, it includes five major parts, which are function design sub-platform, database design sub-platform, unified design sub-platform, injection simulation sub-platform and unified implementation sub-platform. The details of each part are as follows.

[0046] 1. Functional design sub-platform.

[0047] According to the requirements analysis, the system function definition is obtained, and the hardware description language is used to complete the RTL code description of the basic function system. As mentioned above, the designer does not need to face the design difficulty and complexity of the TMR code at this time. On this sub-platform, it is necessary to de...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More