High-speed parallel D/A clock synchronization apparatus

A clock synchronization, high-speed technology, applied in the direction of control/adjustment system, instrument, computer control, etc., can solve the problems of channel out of synchronization, difficult synchronization, difficult to guarantee delay time difference, etc., achieve stable synchronous work and solve synchronization problems , the effect of good stability and reliability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0032] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be further described in detail below in conjunction with specific embodiments and with reference to the accompanying drawings.

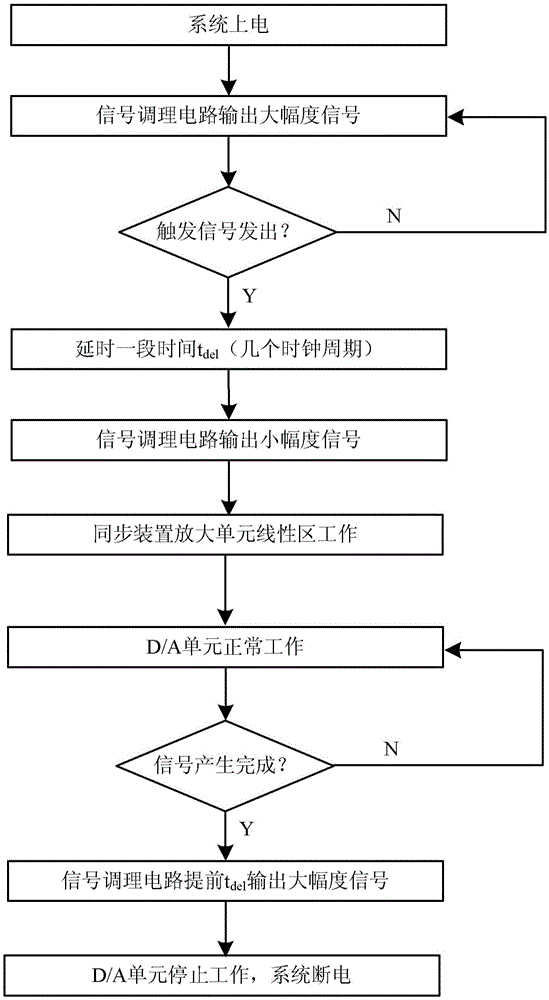

[0033] The invention discloses a clock synchronization device, which has the characteristics of low jitter and low time deviation. By configuring peripheral circuits, the unstable time at the initial moment of triggering can be greatly compressed, and the influence of errors caused by clock jitter can be effectively overcome, so that multiple signals can be generated. The unit works completely in synchronous state.

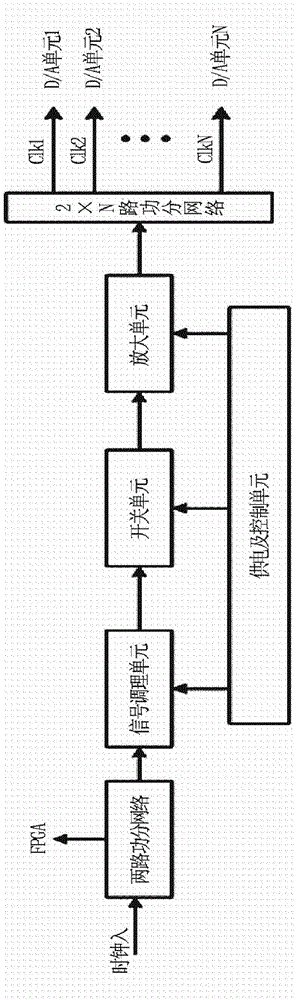

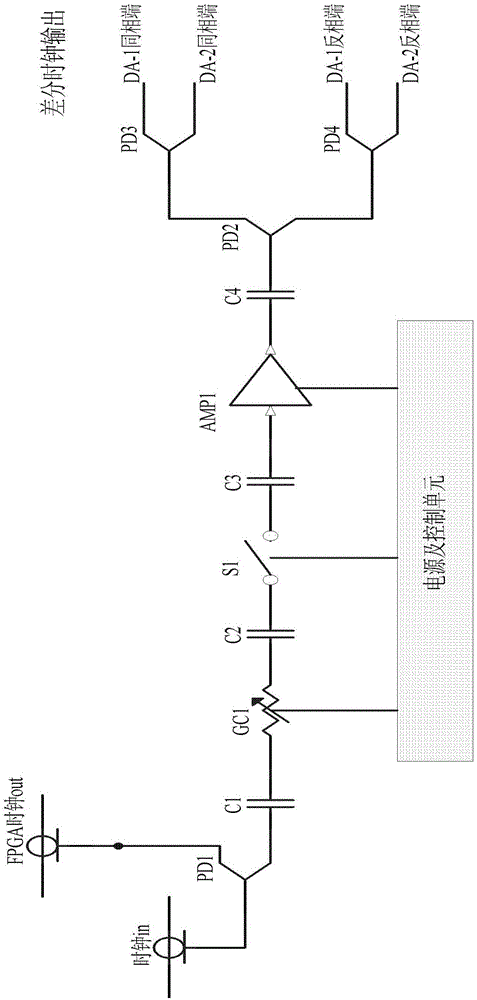

[0034] The technical solution adopted by the high-speed parallel D / A clock synchronization device of the present invention is to adjust the amplitude level of the input clock signal by configuring the signal conditioning unit circuit, and before the switch unit is turned on, the signal amplitude is increased t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More