Fabrication method of low-temperature polycrystalline silicon thin-film transistor (TFT) substrate structure and low-temperature polycrystalline silicon TFT substrate structure

一种低温多晶硅、制作方法的技术,应用在半导体/固态器件制造、半导体器件、电气元件等方向,能够解决晶粒一致性和晶粒的大小不能做到有效控制、驱动TFT电性一致性和电性稳定性差、多晶硅晶粒一致性差等问题,达到避免画质不良、电性稳定性好、晶粒一致性好的效果

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0037] In order to further illustrate the technical means adopted by the present invention and its effects, the following describes in detail in conjunction with preferred embodiments of the present invention and accompanying drawings.

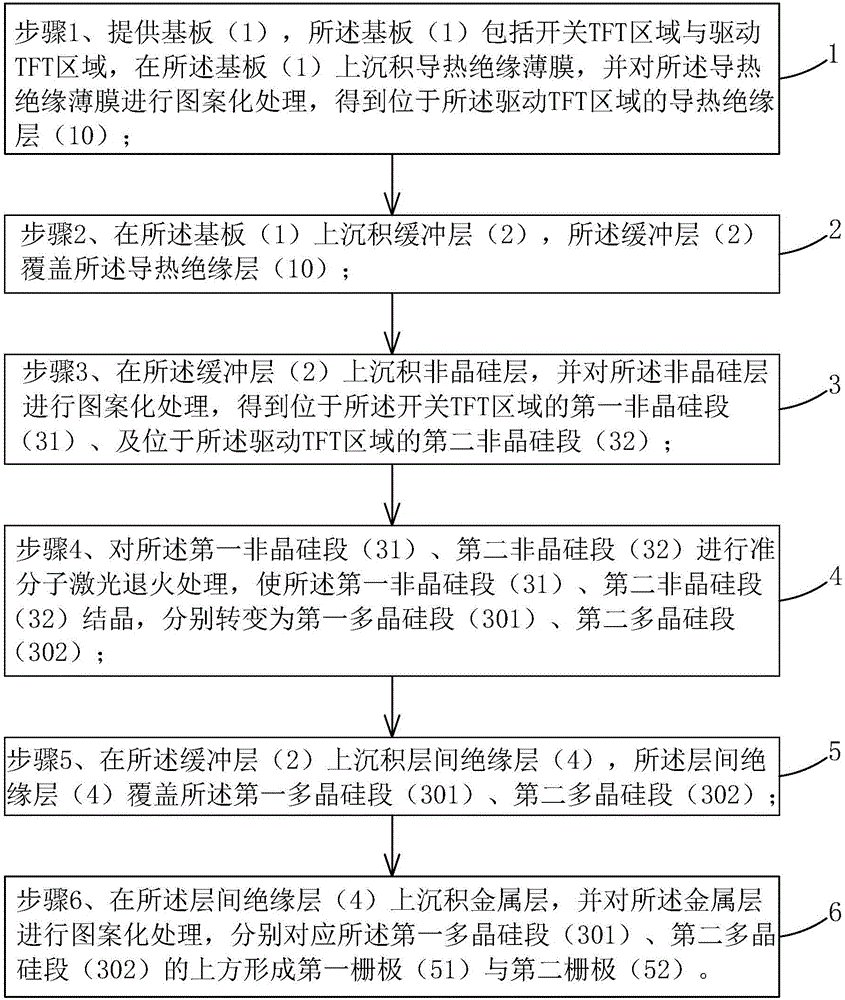

[0038] see figure 1 , the present invention at first provides a kind of fabrication method of low-temperature polysilicon TFT substrate structure, comprises the following steps:

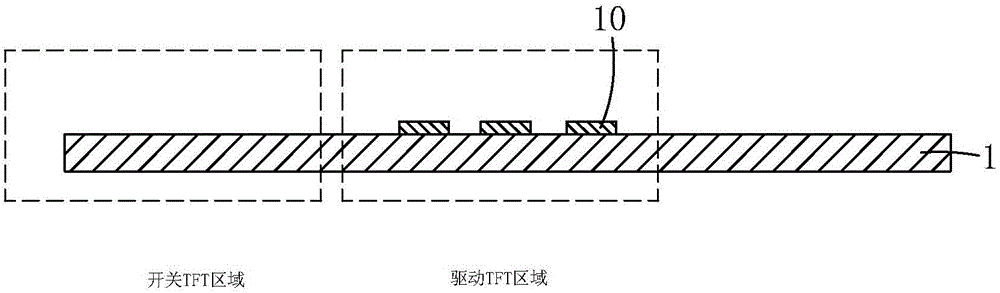

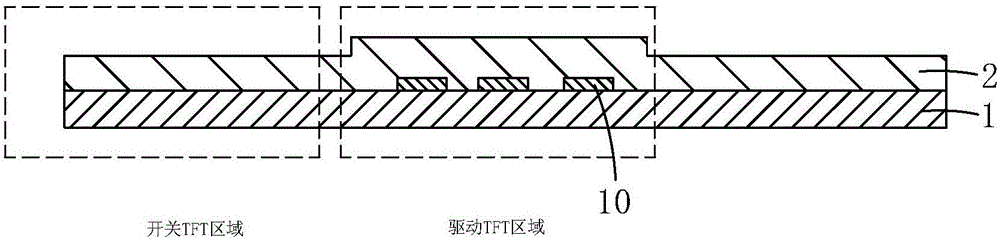

[0039] Step 1, such as figure 2 As shown, a substrate 1 is provided. The substrate 1 includes a switching TFT area and a driving TFT area. A thermally conductive insulating film is deposited on the substrate 1, and the thermally conductive insulating film is patterned to obtain a TFT located in the driving TFT area. The thermally conductive insulating layer 10.

[0040] Specifically, the substrate 1 may be a glass substrate or a silicon substrate.

[0041] Specifically, the material of the thermally conductive insulating layer 10 is magnesium oxide or aluminum ox...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com