Formation method of package structure

A technology of packaging structure and plastic sealing layer, which is applied in the direction of electrical components, electric solid devices, circuits, etc., can solve the problem of reducing the thickness and size of the packaging structure, and achieve the effect of accurate relative position, fixed and stable

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0042] As mentioned in the background technology, the existing stacked chip packaging technology faces process limitations and cost constraints, which limits the popularization and application of the technology. Moreover, the stacked chip packaging technology is also facing the problem of further reducing the thickness of the packaging structure, in order to further Improve chip integration and reduce size.

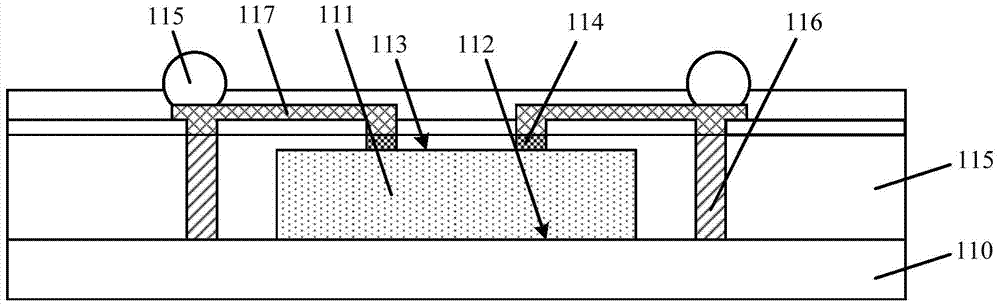

[0043] The stacked chip packaging technology can be realized through a through silicon via (TSV for short) technology or a through molding via (TMV for short) technology. However, both the TSV technology and the TSV technology have certain defects.

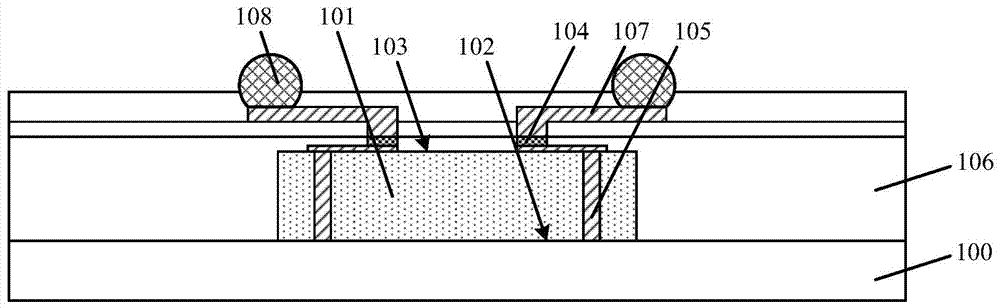

[0044] Please refer to figure 1 , figure 1It is a schematic cross-sectional structure diagram of introducing a through-silicon via structure in the packaging structure to realize the conduction between chips, including: a carrier 100; a chip 101 fixed on the surface of the carrier 100, and the chip 101 includes an opposite ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More