FPGA single event upset fault simulation test system and method

A technology of single event flipping and fault simulation, applied in testing/monitoring control systems, general control systems, electrical testing/monitoring, etc., can solve the problem of inability to verify the function of the on-orbit monitoring program, the reservation of the device under test by the accelerator, and the failure to solve the functional verification and other problems, to achieve the effect of intuitive and clear test results, easy debugging and verification, and low test cost

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

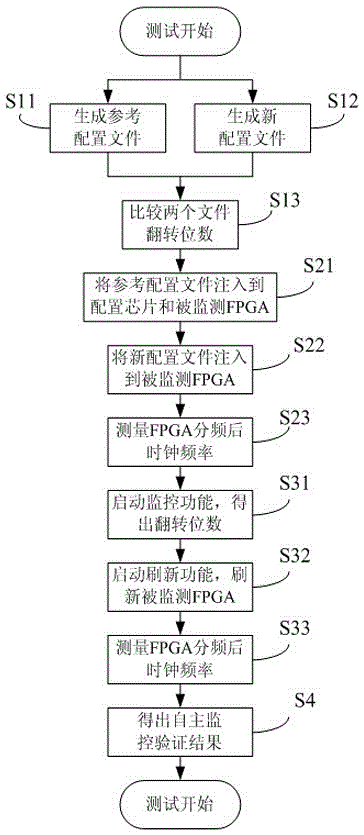

[0040] The following combination Figure 1 to Figure 4 , a preferred embodiment of the present invention is described in detail.

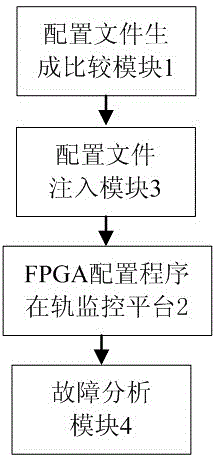

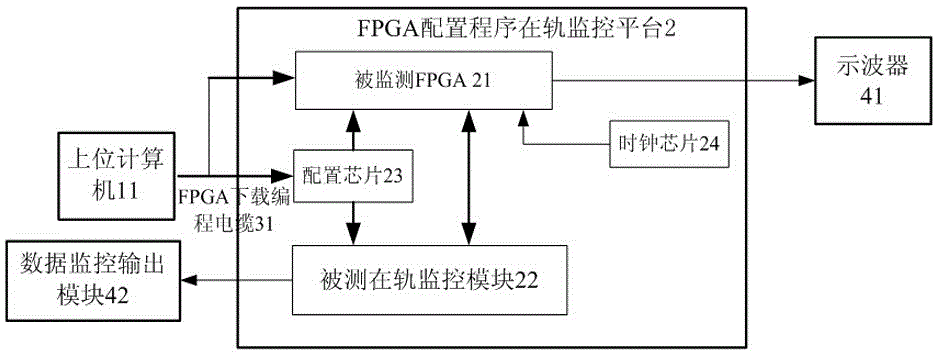

[0041] Such as figure 1 As shown, the FPGA single event upset fault simulation test system provided by the present invention includes: configuration file generation comparison module 1; FPGA configuration program on-orbit monitoring platform 2; configuration file injection module 3, which is connected to the configuration file Generate comparison module 1 and FPGA configuration program on-orbit monitoring platform 2; fault analysis module 4, which is connected with said FPGA configuration program on-orbit monitoring platform 2.

[0042] Such as figure 2 As shown, the configuration file generation and comparison module 1 is implemented by a host computer 11 to generate a reference configuration file and a new configuration file, and compare the flipped bits of the two.

[0043]Described configuration file injecting module 3 adopts FPGA download ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More