On-chip network multi-core framework

A network-on-chip, multi-core technology, applied in data exchange network, advanced technology, digital transmission system, etc., can solve the problems of lack of unified clock, difficult to control clock misalignment, low SOC communication efficiency, etc., to achieve the effect of improving resource utilization

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0029] The embodiments listed in the present invention are only used to help understand the present invention, and should not be interpreted as limiting the protection scope of the present invention. For those of ordinary skill in the art, they can also Improvements and modifications are made to the present invention, and these improvements and modifications also fall within the protection scope of the claims of the present invention.

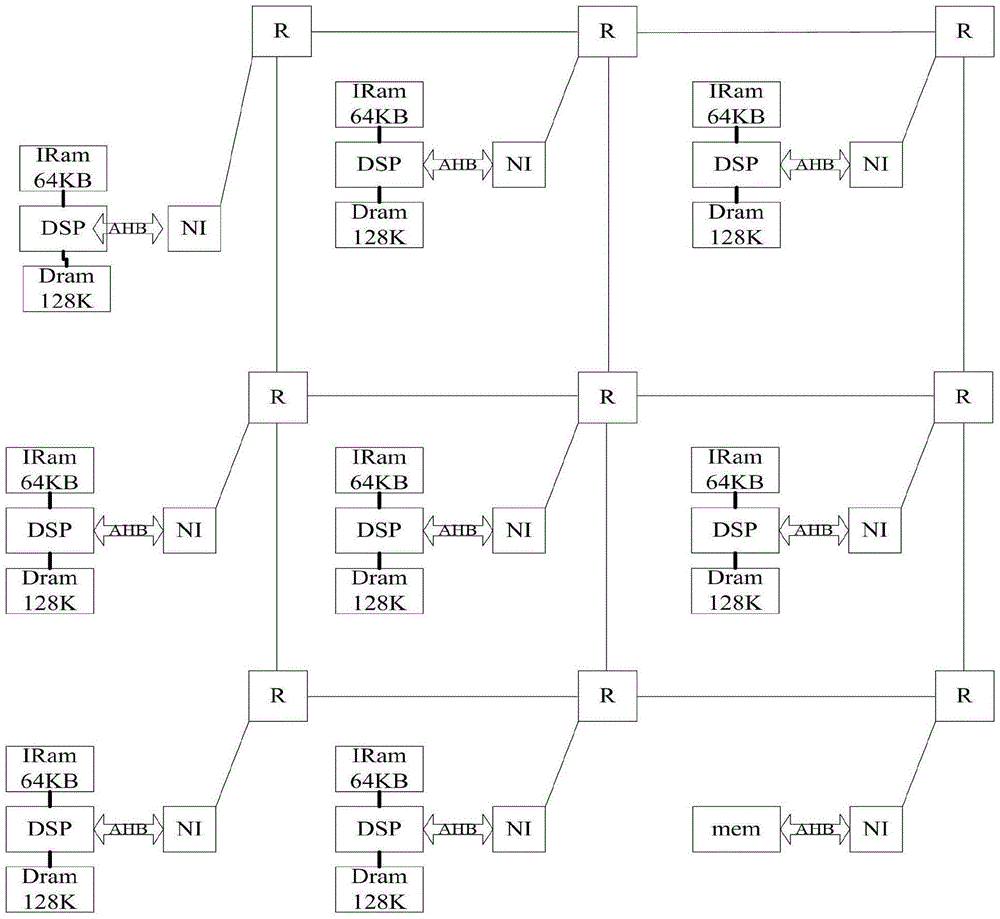

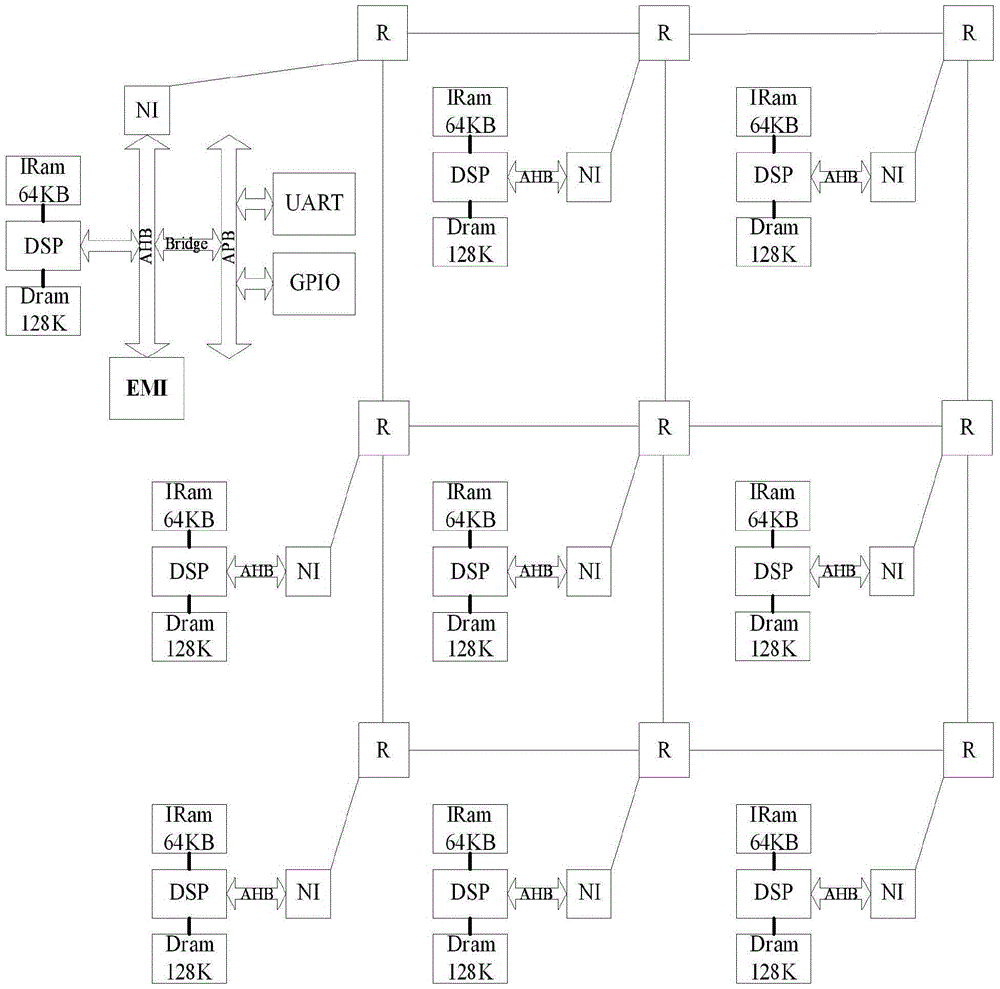

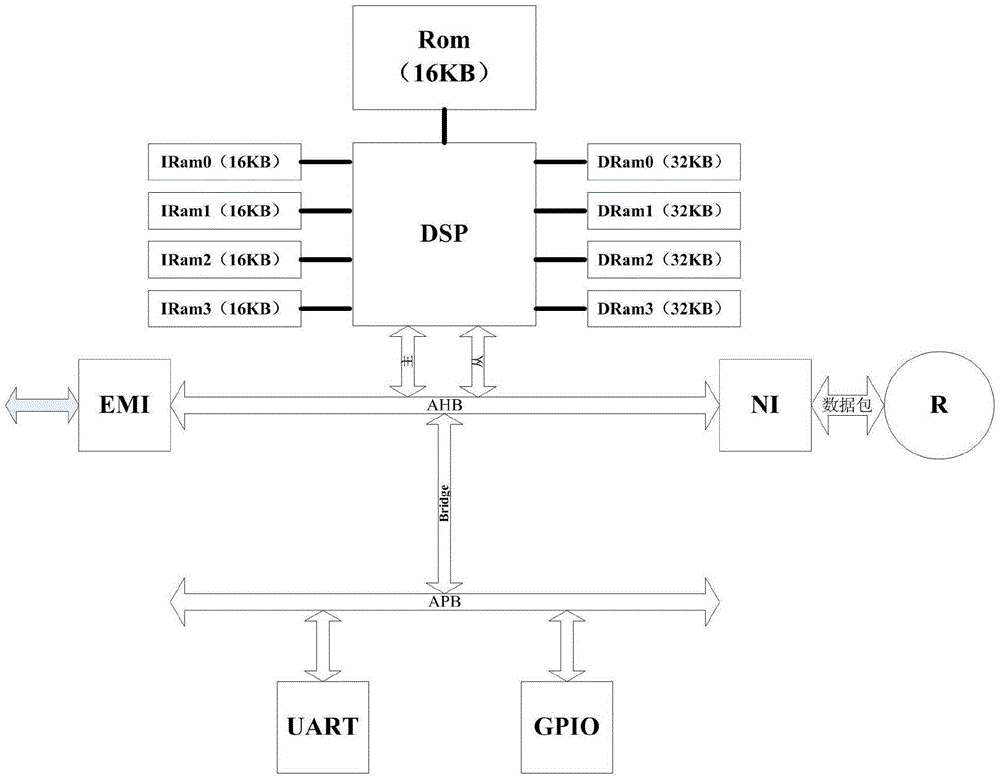

[0030] With the RTL multi-core network design verification test platform, the overall structure of the NOC multi-core architecture of the present invention is as follows figure 2 , using a 3x3 2D-MeshNOC architecture, R in the figure represents a router, the router R in the upper left corner is connected to the master control core node, the master control core node is a computing unit, and the rest of the routers R are connected to multiple computing cores Nodes, multiple computing core nodes are multiple computing units, and the main control ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More