Preparation method of integrated circuit chip failure analysis sample

A technology for failure analysis samples and integrated circuits, which is applied in the preparation of test samples, circuits, electrical components, etc., and can solve the problems of no packaging equipment, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0020] In order to make the objects, features and advantages of the present invention more comprehensible, specific implementations of the present invention will be described in detail below in conjunction with the accompanying drawings.

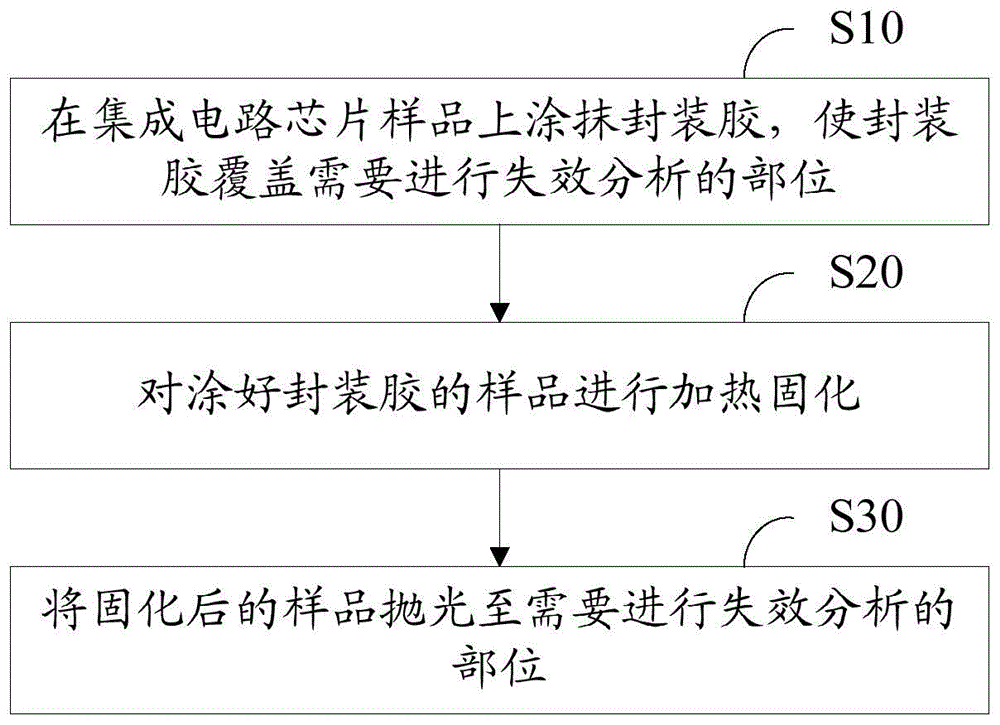

[0021] figure 1 It is a flowchart of a method for preparing samples for failure analysis of integrated circuit chips in an embodiment.

[0022] S10, apply encapsulation glue on the integrated circuit chip sample, so that the encapsulation glue covers the parts to be subjected to failure analysis.

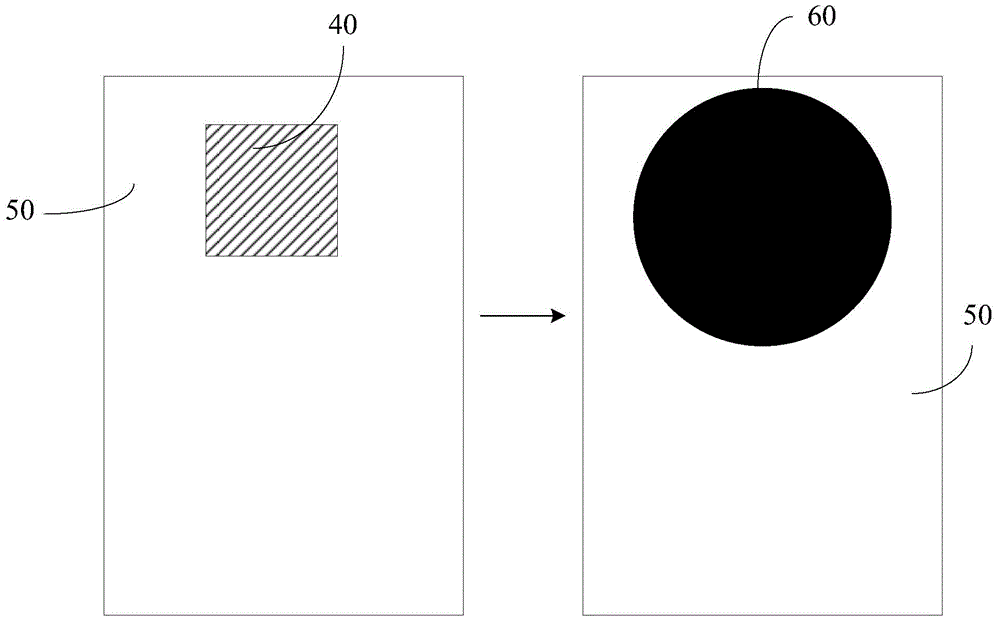

[0023] For the case where the sample is large and does not require positioning analysis, the operator can polish to the desired position more accurately without relying on the mark during subsequent polishing, so an appropriate amount of encapsulant can be directly applied to the sample. Common gluing tools such as brushes and needles can be used for gluing.

[0024] S20, heating and curing the sample coated with encapsulant.

[0025] Heat with...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More