Read-only register verification test platform and verification method based on UVM (Universal Verification Methodology Manual)

A verification methodology and verification test technology, applied in the field of read-only register verification and read-only register verification test platform, can solve the problems of unable to see the DUT hierarchy, rewrite register values, unable to verify the correct reading of register data, etc. Increase verification reliability, facilitate construction, reduce programming volume and programming difficulty

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

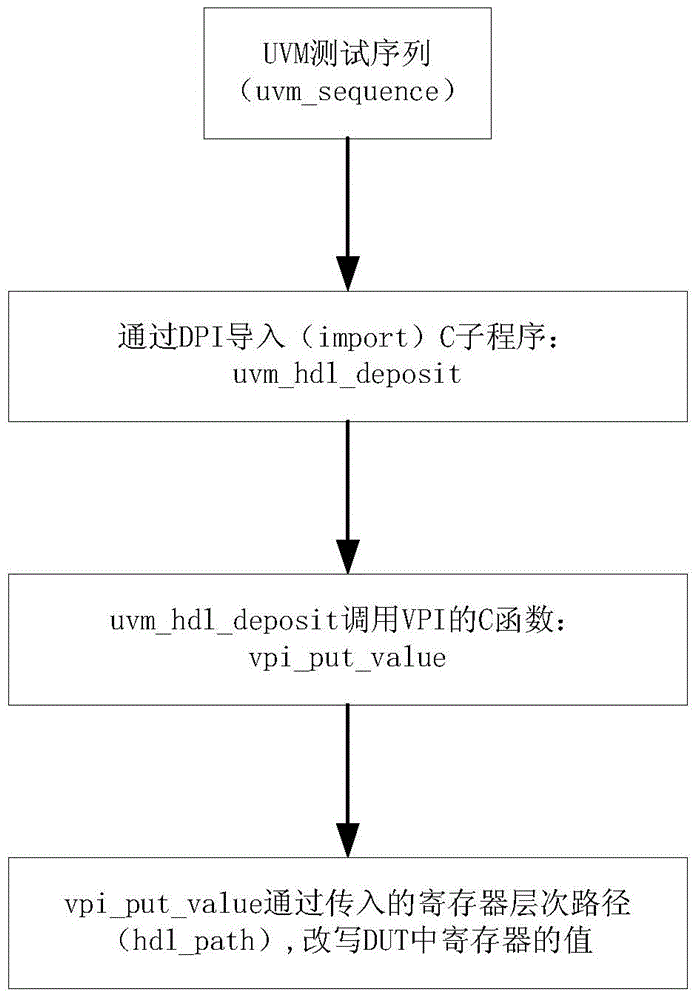

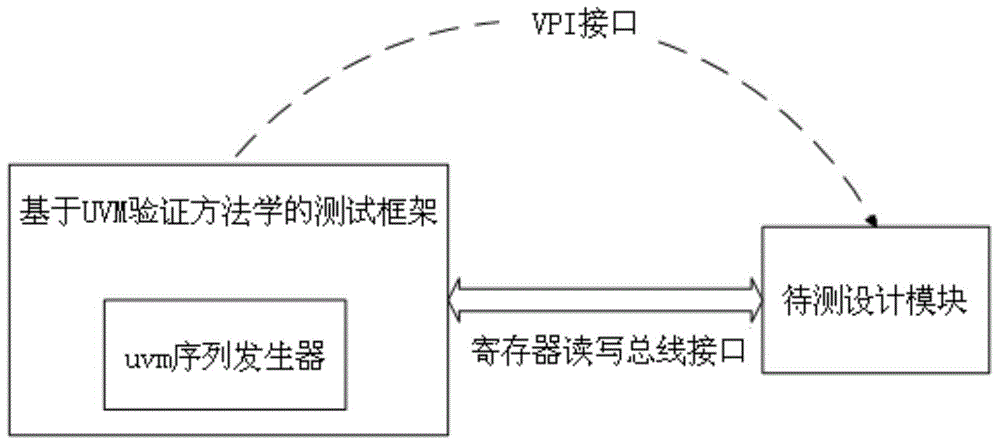

[0015] Such as figure 1 As shown, the UVM test sequence is imported (import) the C subroutine uvm_hdl_deposit through DPI (direct programming interface); the UVM test sequence is passed through uvm_hdl_deposit(stringhdl_path, inputuvm_hdl_data_tvalue; string indicates that the incoming hdl_path parameter is a string type, and hdl_path stores a register Hierarchical path; input indicates that the following value variable is the subroutine input, uvm_hdl_data_t indicates the data type of value, which is a data type defined in uvm, which is equivalent to register data, and value is the value that will be stored in the register eventually) The task calls the C function vpi_put_value of the VPI interface, according to the hierarchical relationship of the read-only register in the DUT [or as figure 2 As shown, the value of the read-only register is overwritten by the passed register hierarchy path (hdl_path)]. As mentioned above, the UVM test sequence cannot directly refer to the ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More