Shield grid groove type MOSFET process method

A process method and trench-type technology, applied in electrical components, semiconductor/solid-state device manufacturing, circuits, etc., can solve problems such as high gate leakage, poor quality of oxide film between polysilicon, and the thickness of oxide film between polysilicon cannot be controlled separately

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

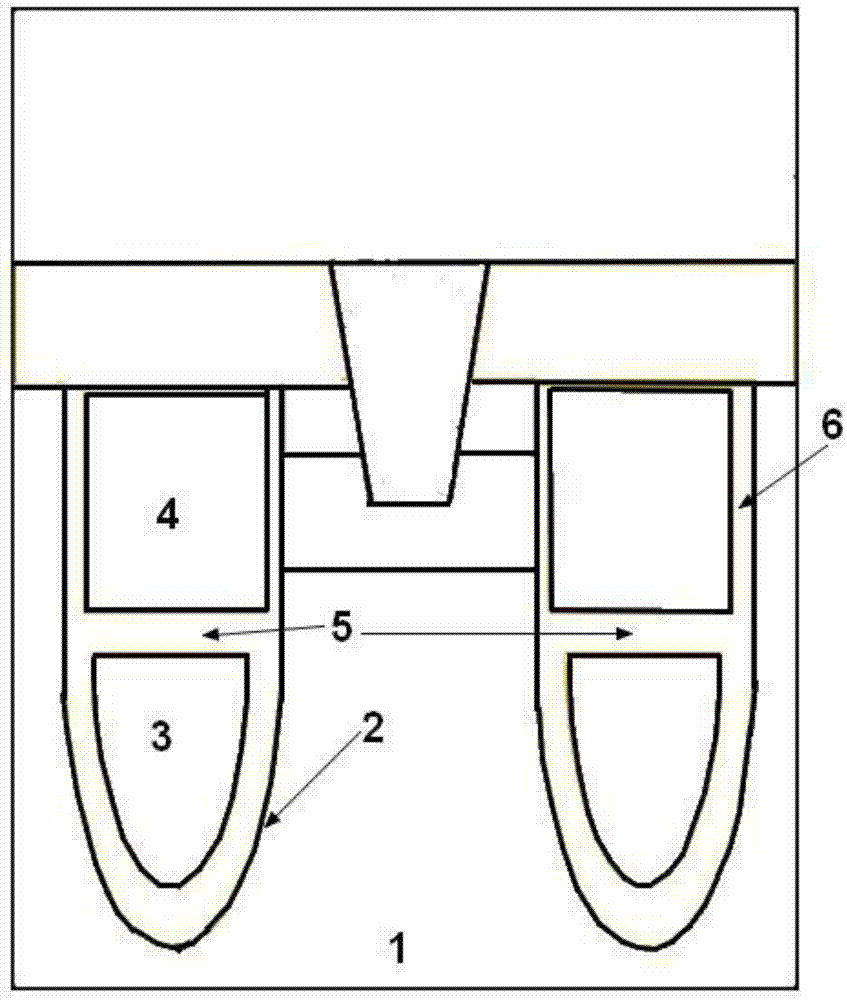

[0027] The shielded gate trench MOSFET process method of the present invention comprises the following process steps:

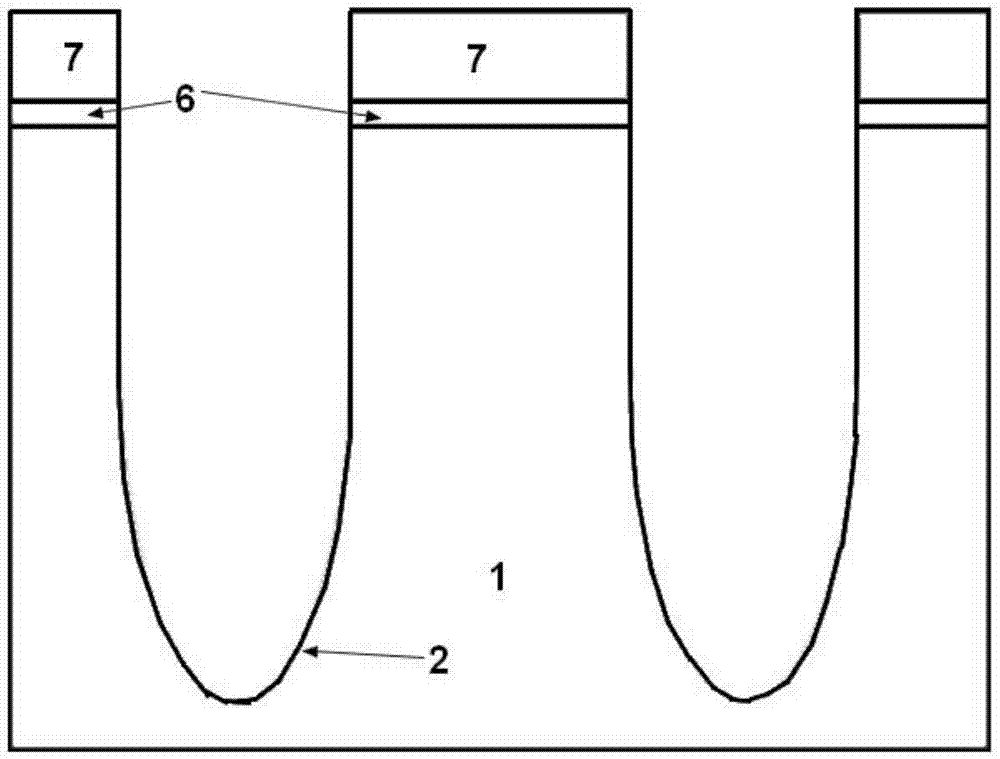

[0028] Step one, such as image 3 As shown, a layer of silicon oxide 6 is deposited on the silicon substrate 1, and then a layer of silicon nitride 7 is deposited. The photoresist defines a trench region on the silicon nitride and silicon oxide, and the photoresist is removed. Using silicon nitride and silicon oxide as hard masks, the substrate is etched to form trenches 2 .

[0029] Step 2, deposit a layer of silicon oxide 6 on the sidewall and bottom of the trench 2, such as Figure 4 shown.

[0030] Step three, such as Figure 5 As shown, the trench 2 is filled with polysilicon 3 and etched back, and the polysilicon is etched back until the surface is flush with the silicon oxide 6 on the substrate surface.

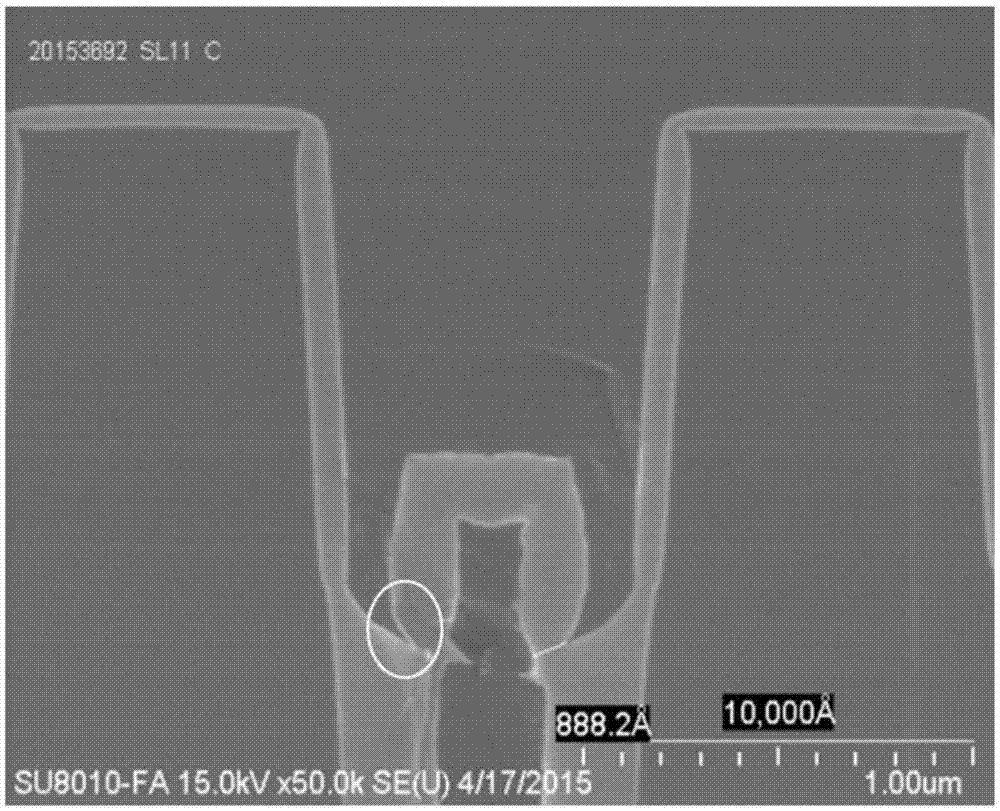

[0031] Step 4, etching back the polysilicon, and removing the silicon oxide 6 on the sidewall of the trench. The polysilicon is etched back unti...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More