Patents

Literature

444results about How to "Prevent dislocation" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

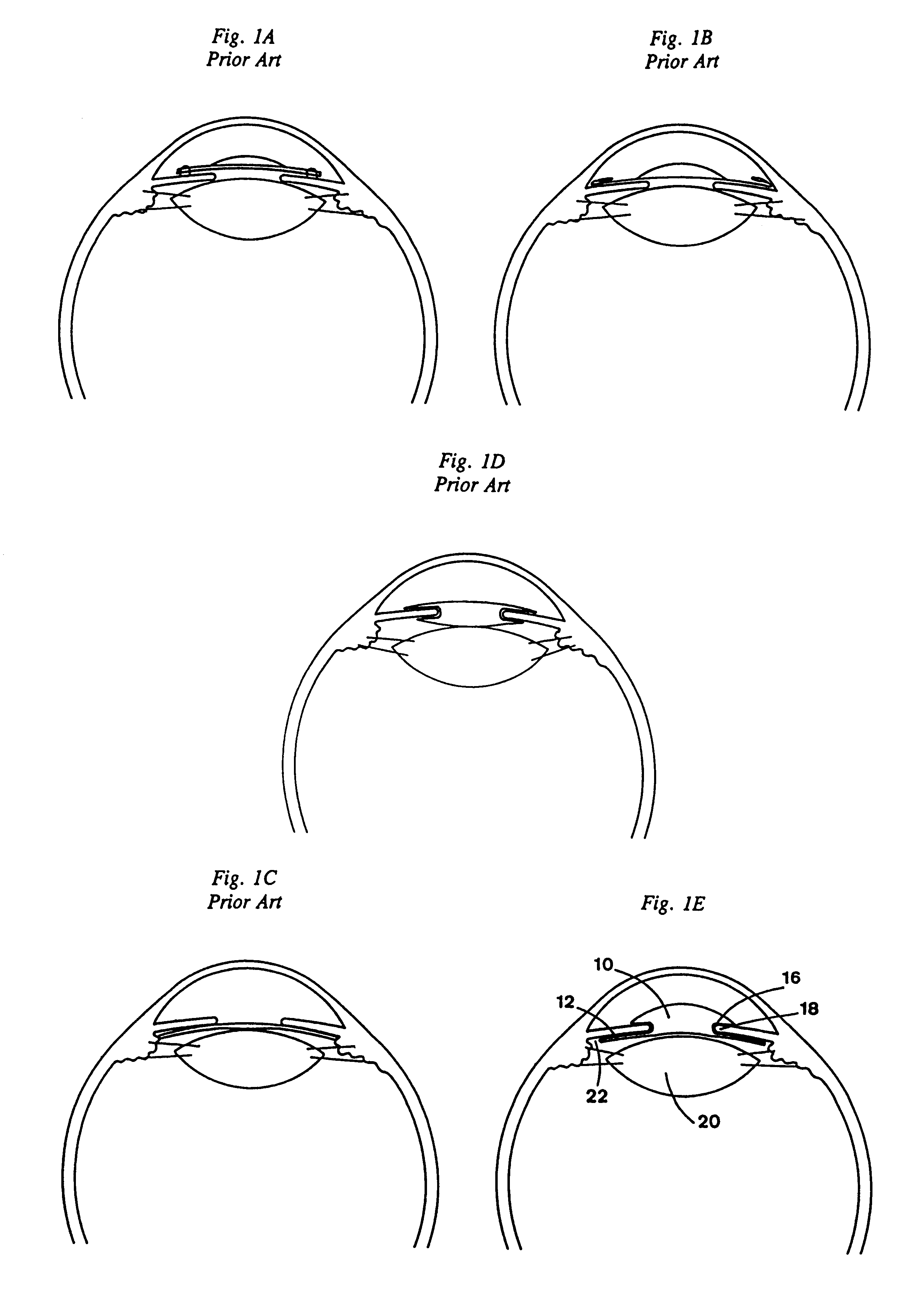

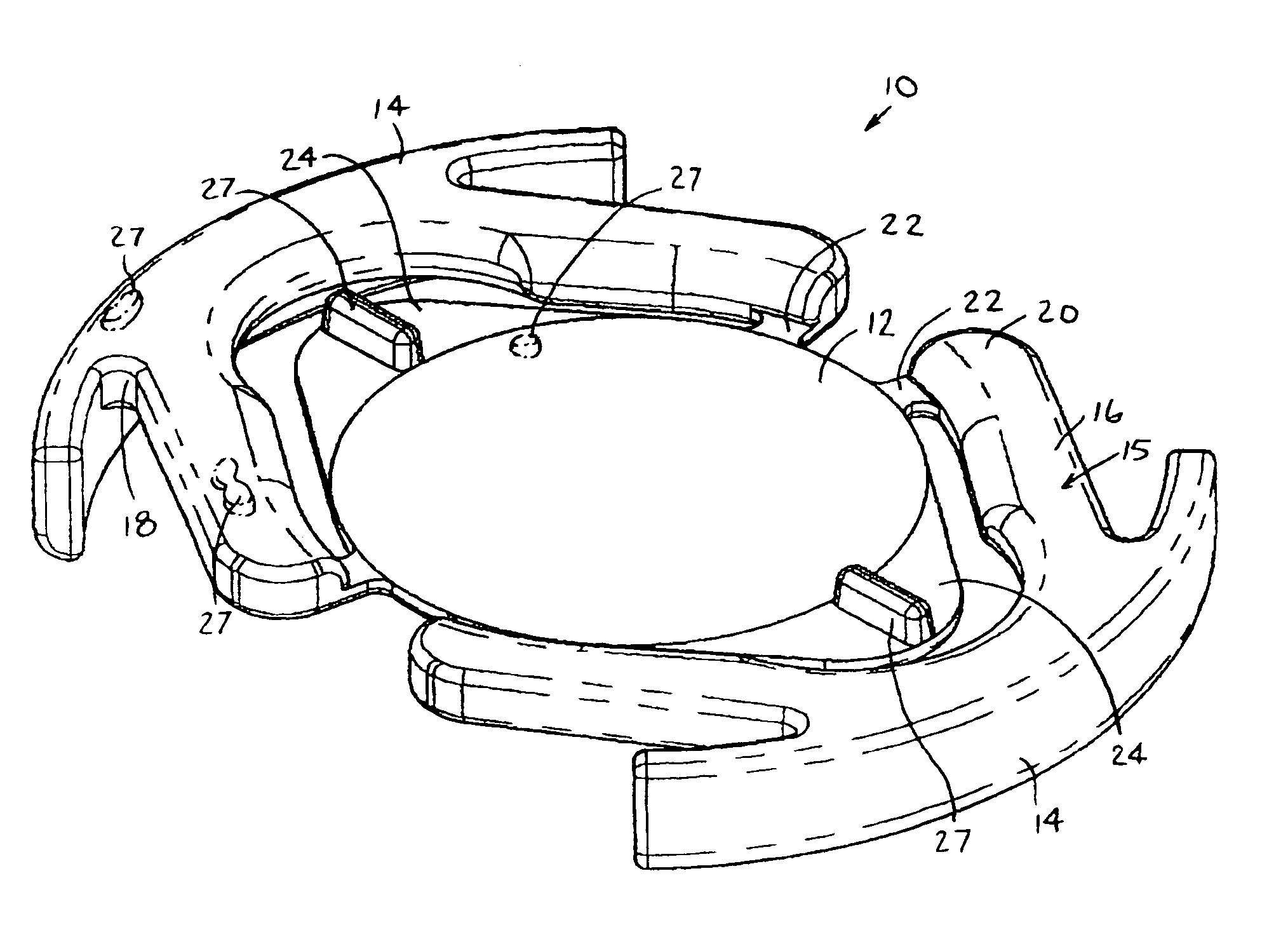

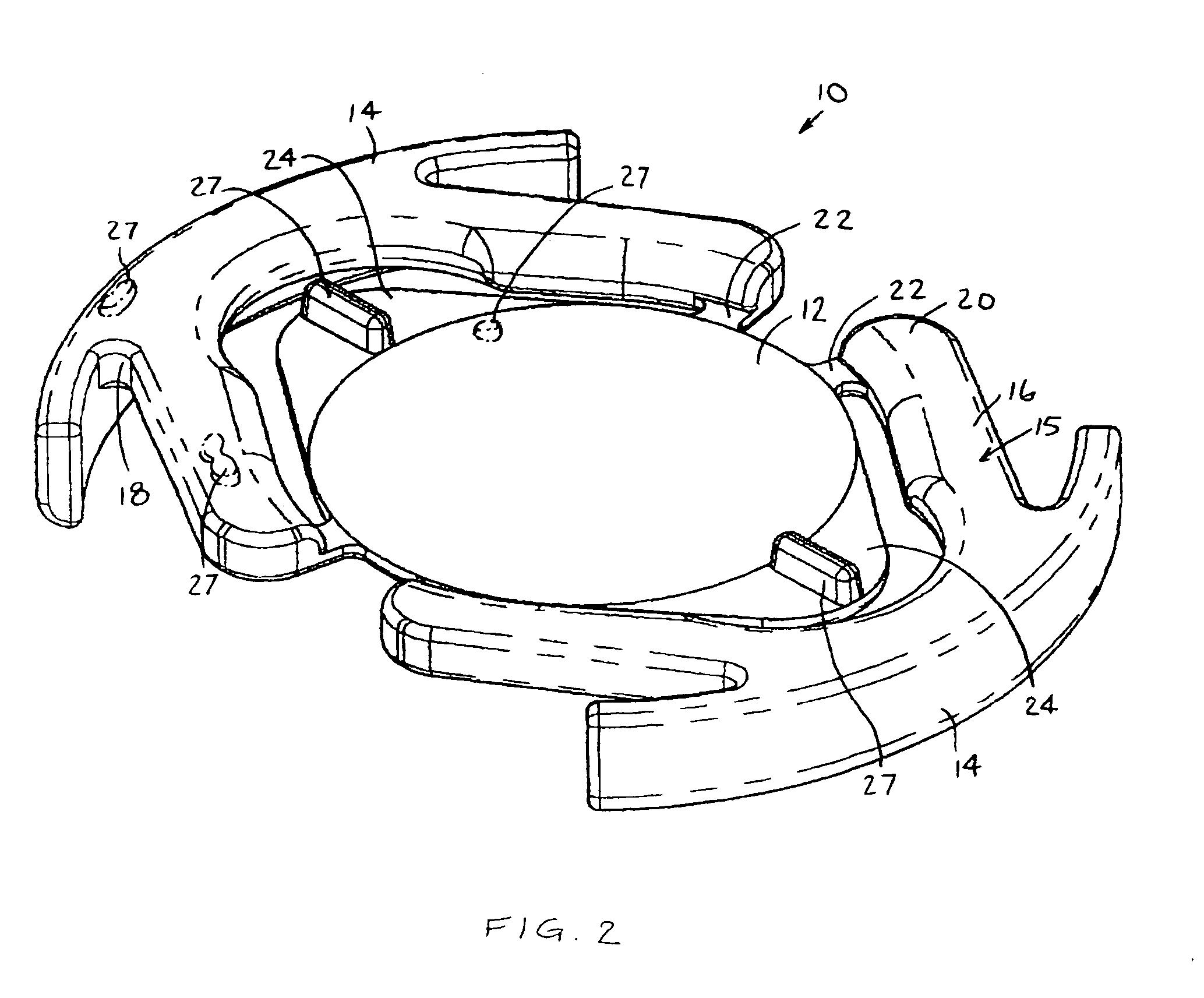

Intraocular lens with accommodative properties

InactiveUS6200342B1Focus assistPrevent excessive lateral movement and luxationIntraocular lensPupil diameterIntraocular lens

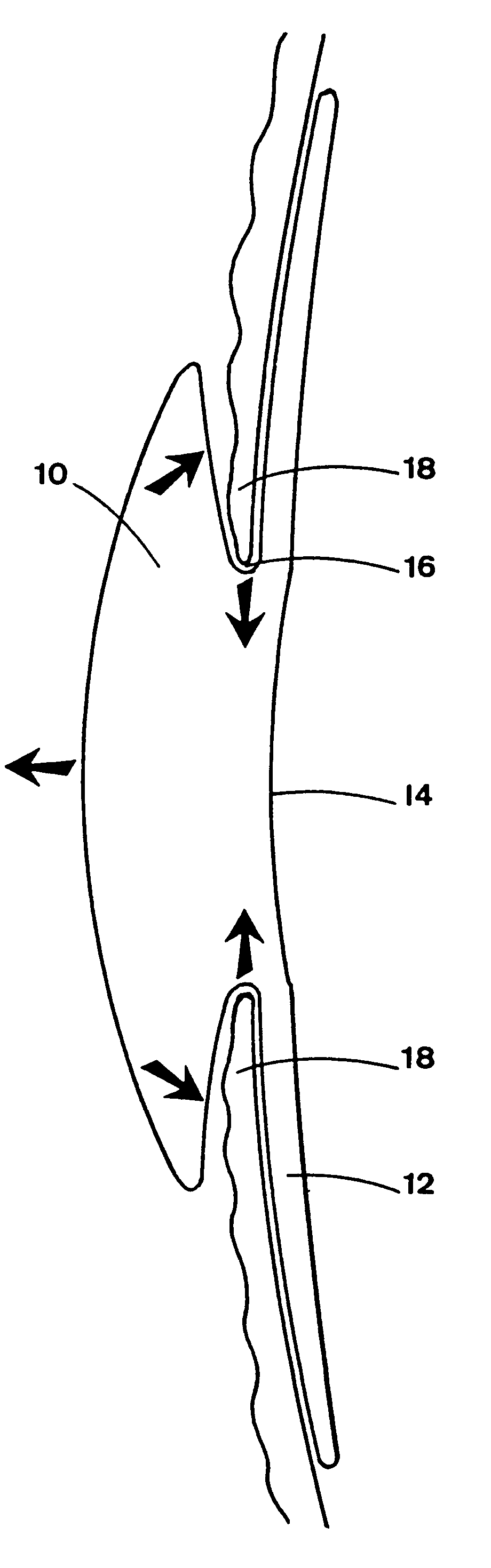

A new lens design and method of implantation uses the change in pupil diameter of the eye concurrent with the changes induced by a contraction of the ciliary muscle during the accommodative reflex, in order to assist in focusing of nearby objects. This new intraocular lens consists of two parts. The posterior part or haptic part is inserted behind the iris and in front of the natural lens or artificial implant. Its main purpose is to participate in the accommodative mechanism and to prevent excessive lateral movement and luxation of the lens. An anterior or optical part is made of flexible material and is placed before the iris. Its diameter is variable but should be large enough to cover the pupillary margins to some degree under various conditions of natural dilation. The anterior and posterior part of the lens are separated by a compressible circular groove in which the iris will settle. The diameter of this groove is slightly larger than the pupillary diameter measured under normal photopic daylight conditions and for distance vision. Since the pupil becomes smaller in near vision, the iris will exert a slight pressure at the level of the groove of the lens which will cause a progressive and evenly distributed flexing of the anterior part of the intraocular lens, as the diameter of the compressible circular groove slightly decreases. This flexing will induce an increase in refractive power which corresponds to a variable part of the amount necessary for focusing nearby objects.

Owner:TASSIGNON MARIE JOSE B

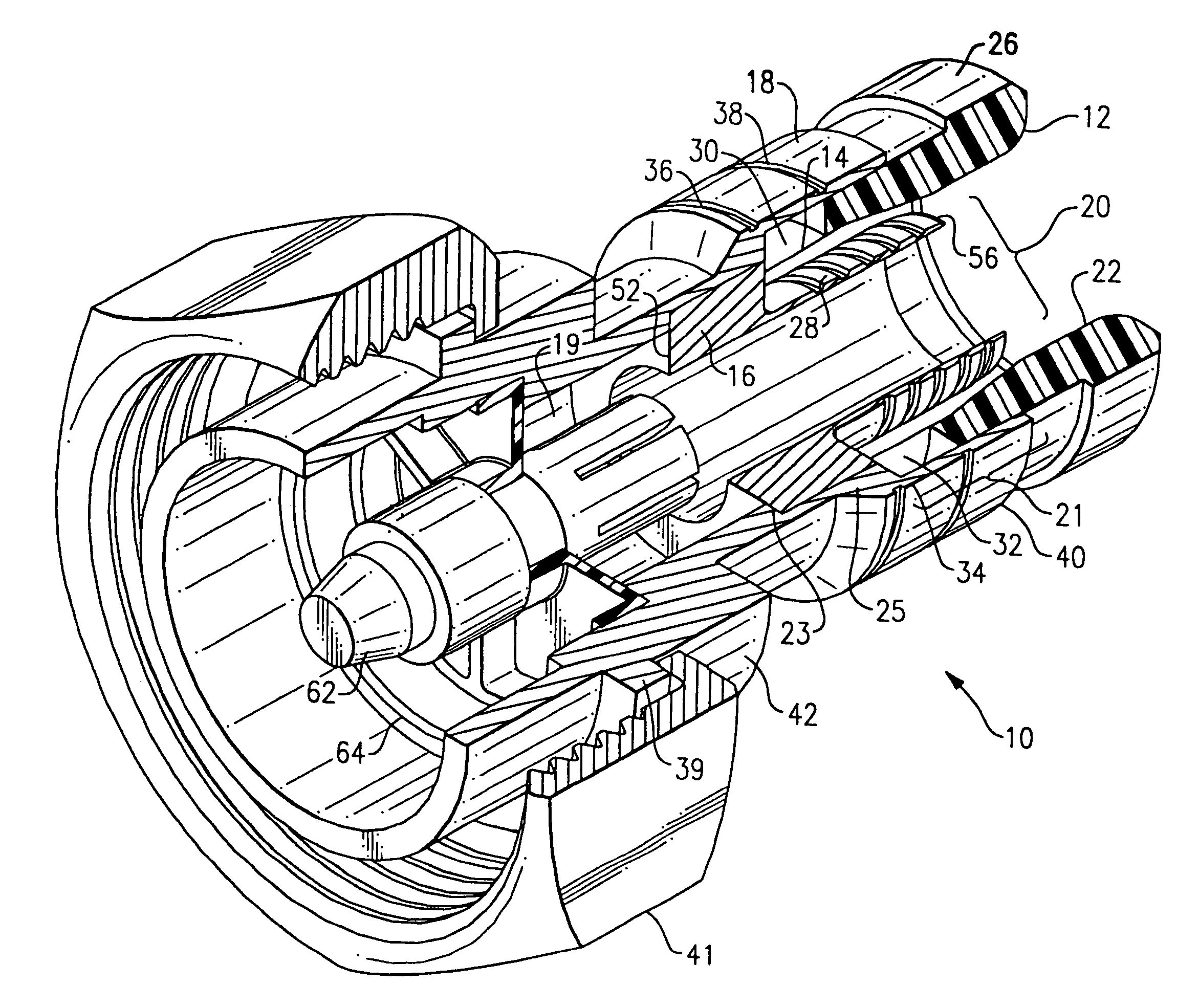

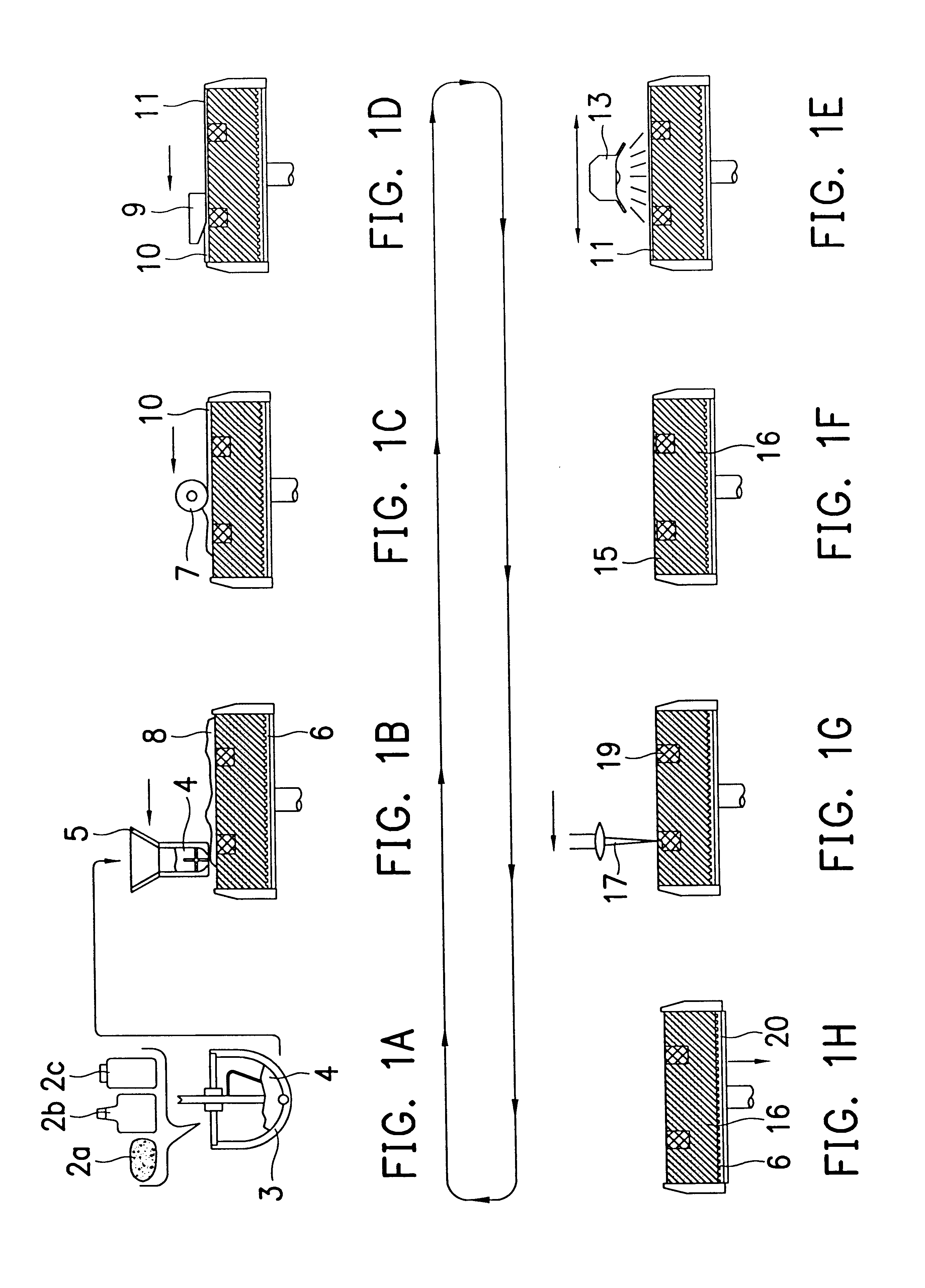

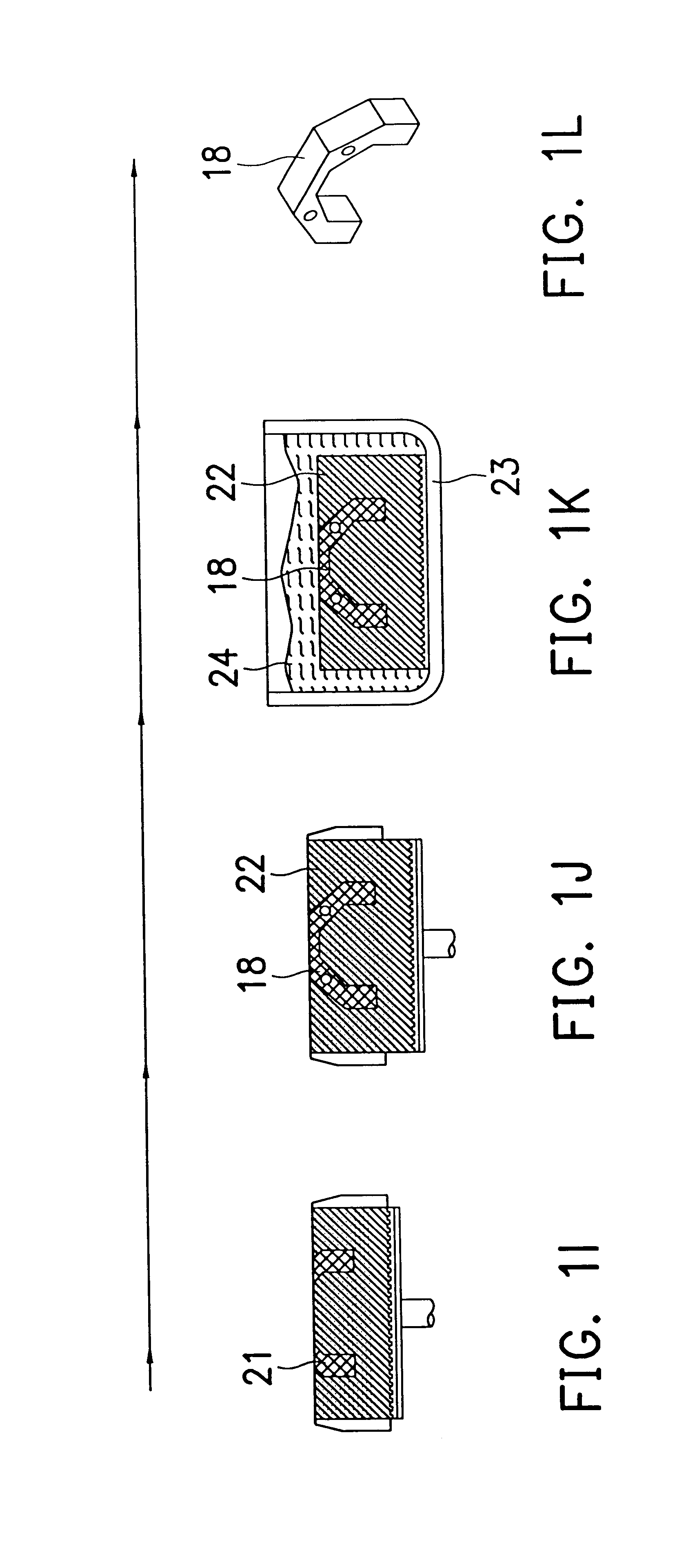

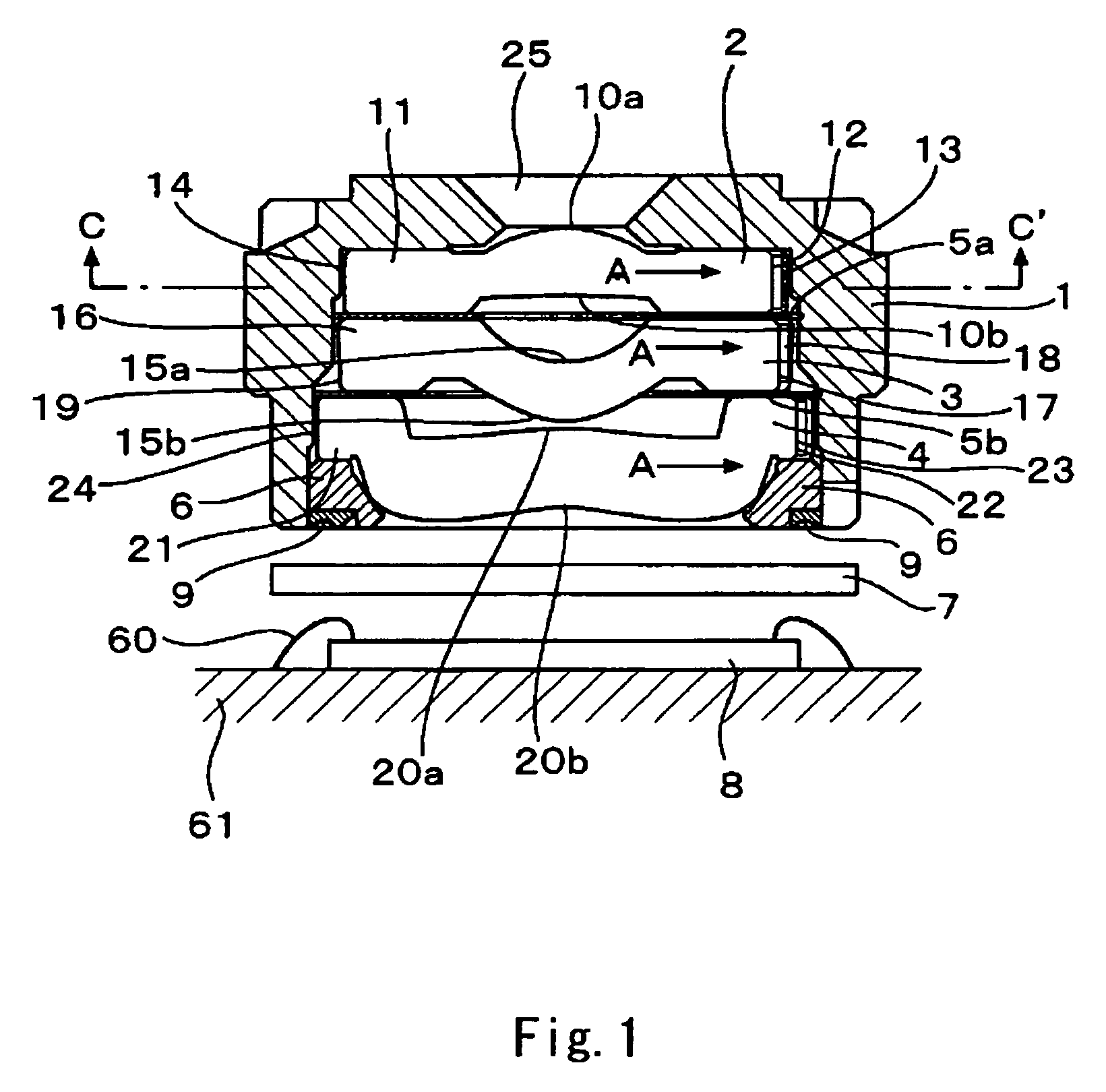

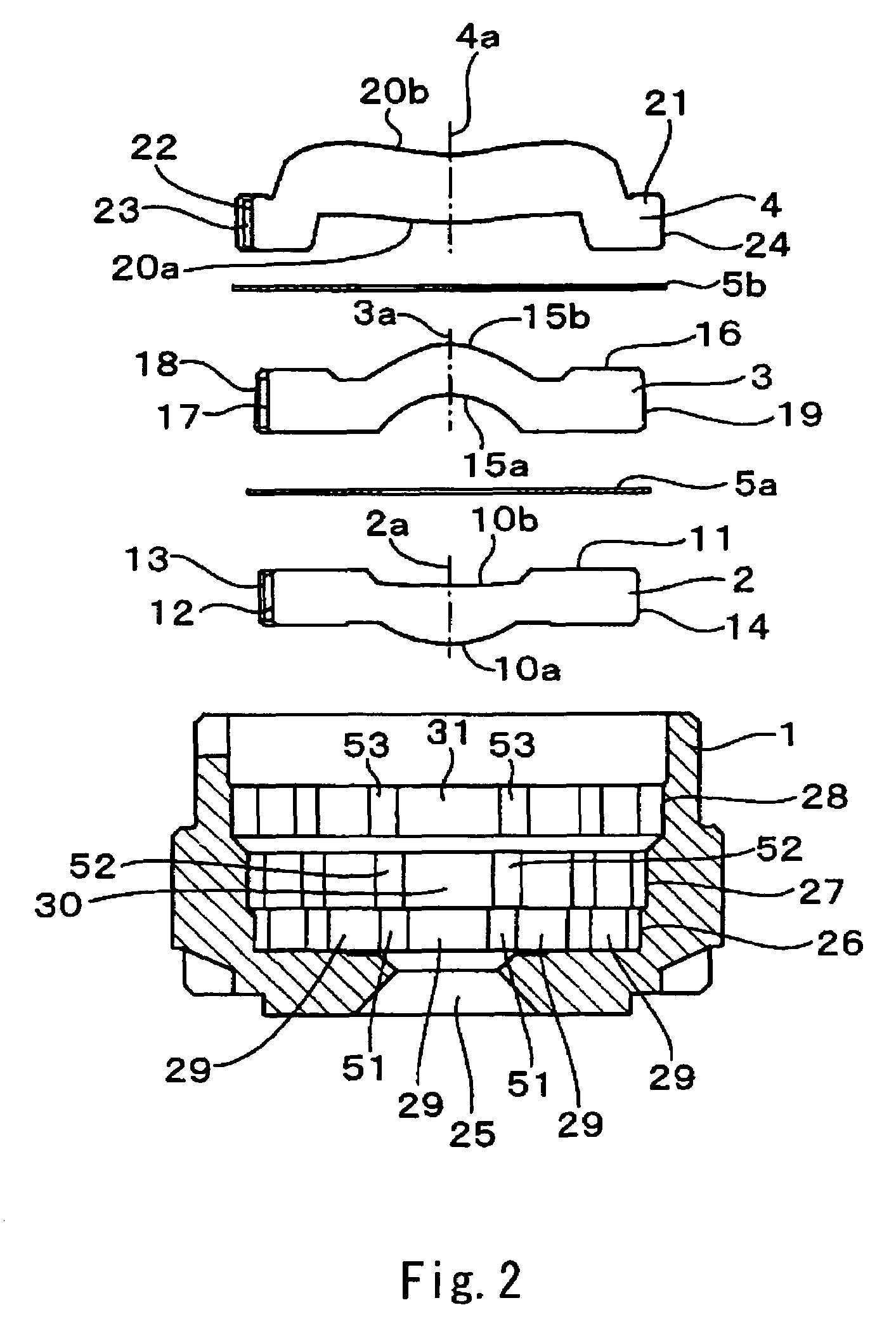

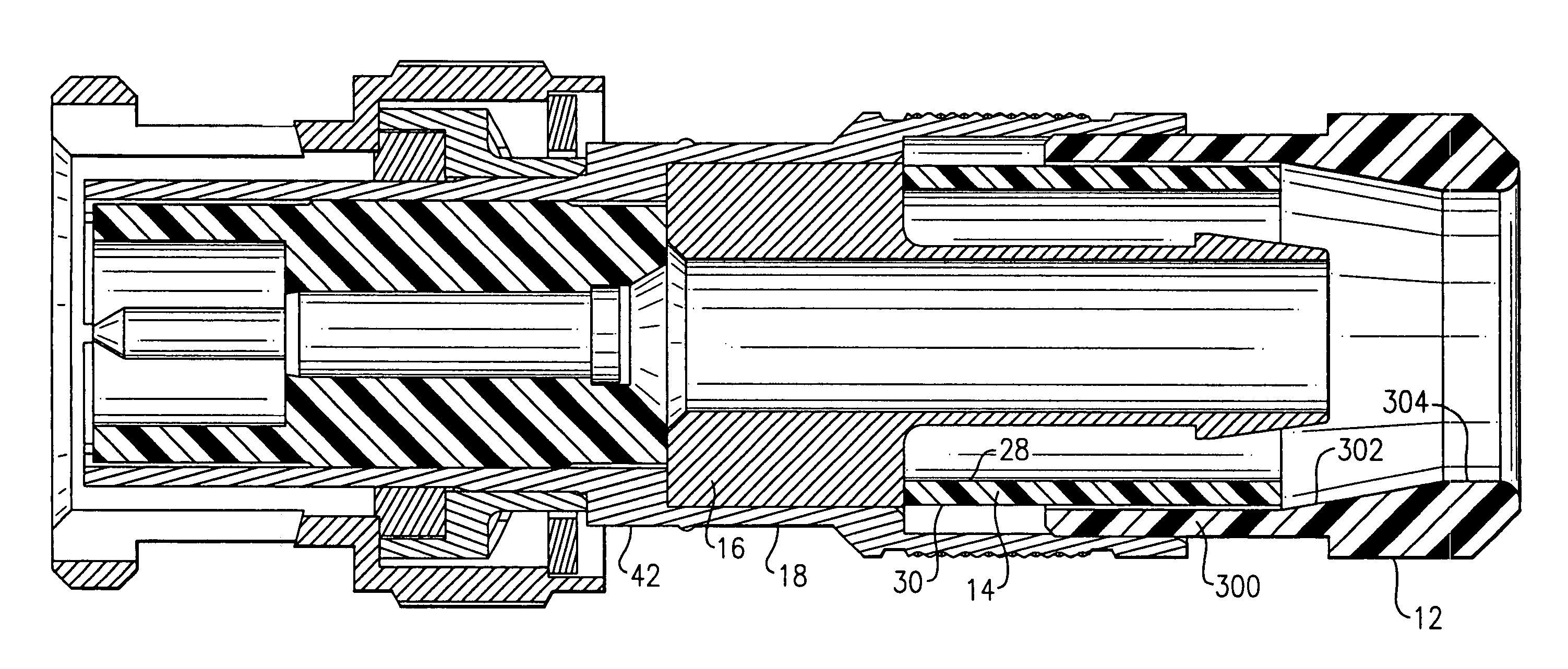

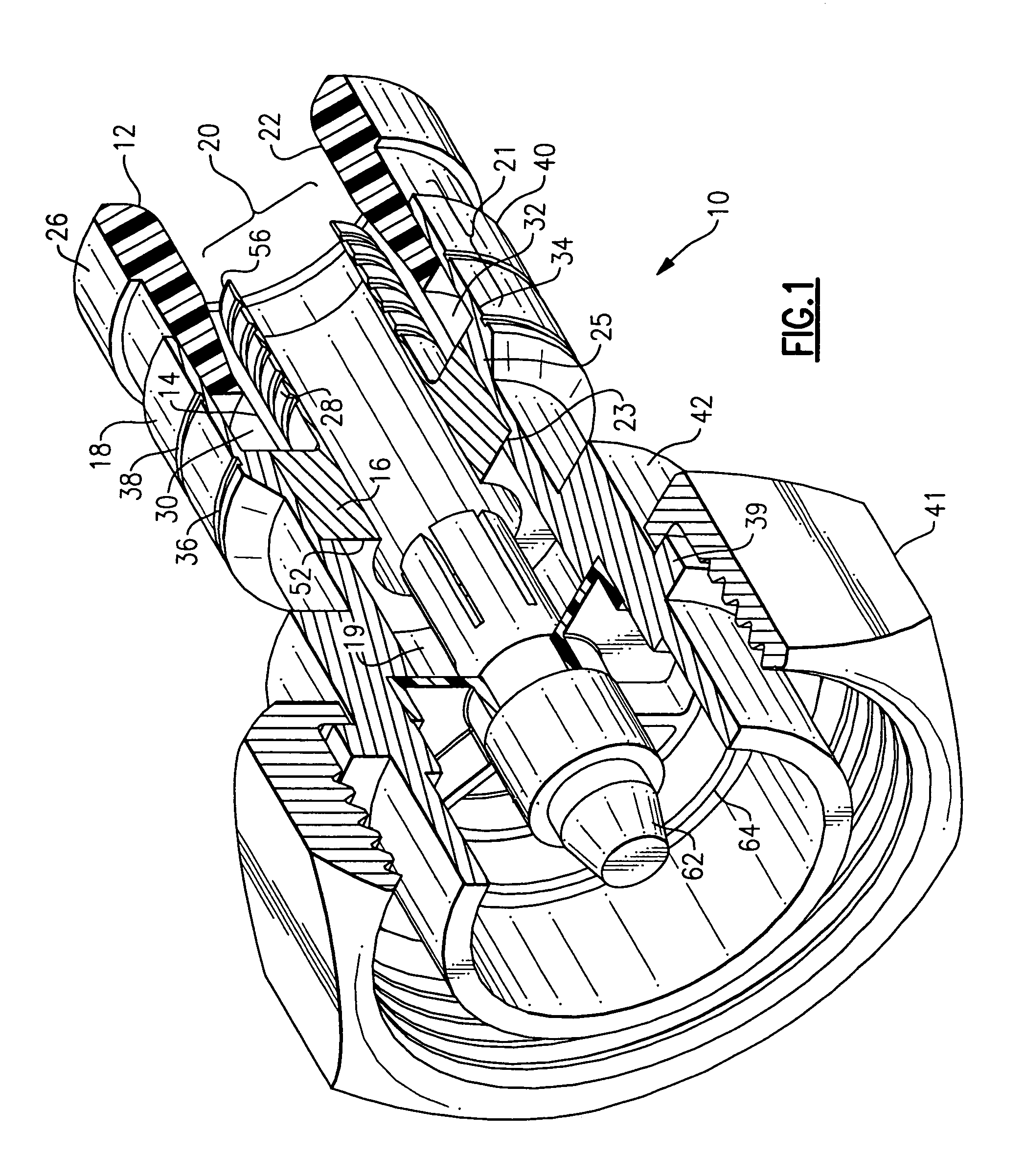

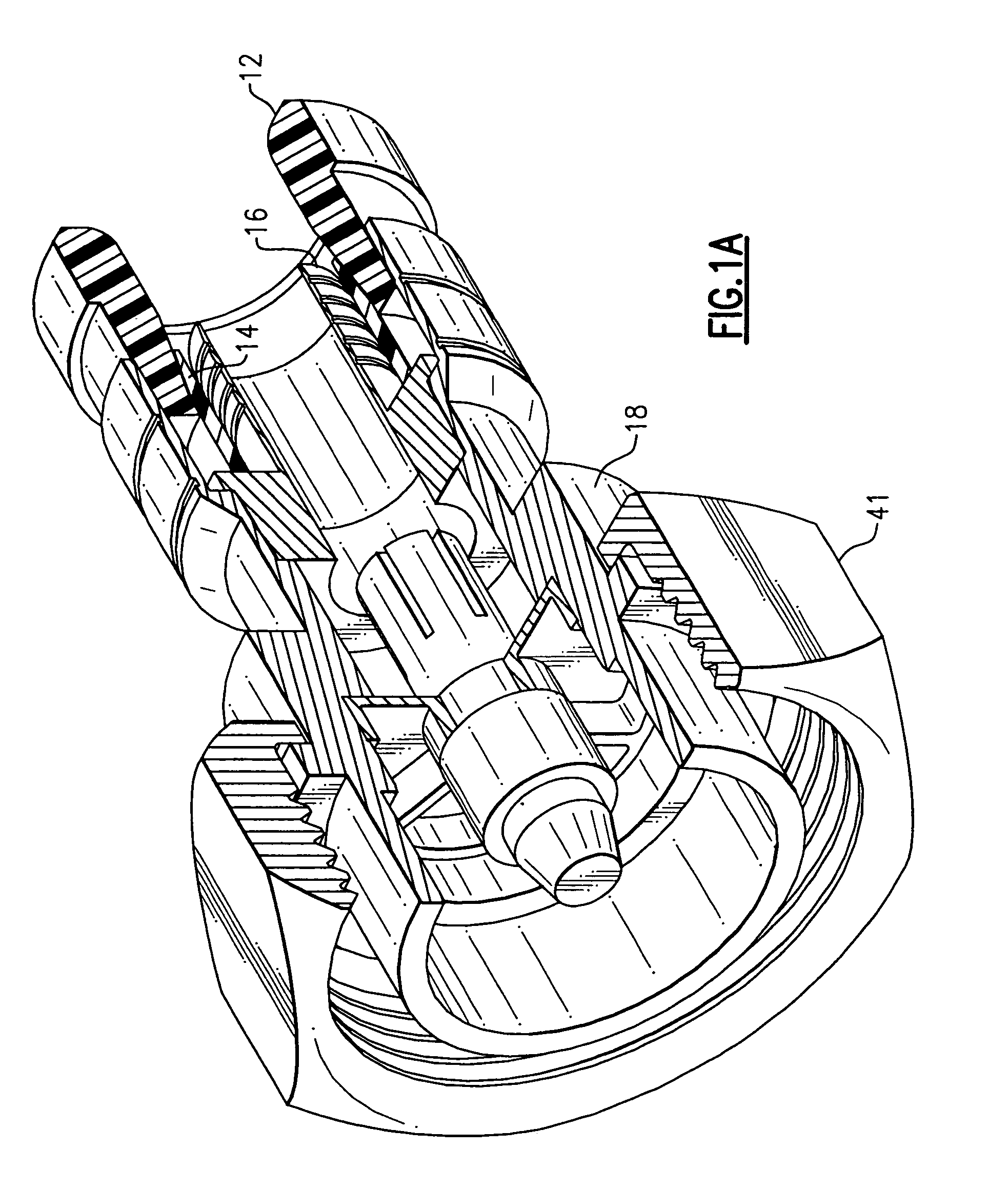

Compression connector for coaxial cable

ActiveUS7131868B2Reduce distanceReducing required insertion lengthTwo pole connectionsCoupling device detailsCoaxial cableElectrical conductor

A compression connector for the end of a coaxial cable. The coaxial cable has a center conductor surrounded by a dielectric layer, the dielectric layer being surrounded by a conductive grounding sheath, and the conductive grounding sheath being surrounded by a protective outerjacket. The compression connector includes a body, a post and a compression member. The body and / or the compression member can have various shapes and orientations to enable the compression connector to readily accommodate coaxial cable having various thicknesses, due to, for example, being made by different manufacturers.

Owner:RF IND

Compression connector for coaxial cable

ActiveUS7029326B2Reduce distanceReducing required insertion lengthElectrically conductive connectionsTwo pole connectionsCoaxial cableEngineering

A coaxial cable compression connector includes a connector body having a first end and a second end, and an internal passageway. The compression connector further includes a tubular post having a first end configured for engagement with the conductive grounding sheath of the coaxial cable and a second end configured for engagement with the internal passageway of the body. The connector further includes a compression member. The first end of the compression member includes an outer surface and a tapered inner surface, the outer surface is configured for engagement with a portion of the internal passageway at the first end of the body. The connector further includes a ring member which is configured for engagement with the tapered inner surface of the compression member.

Owner:RF IND

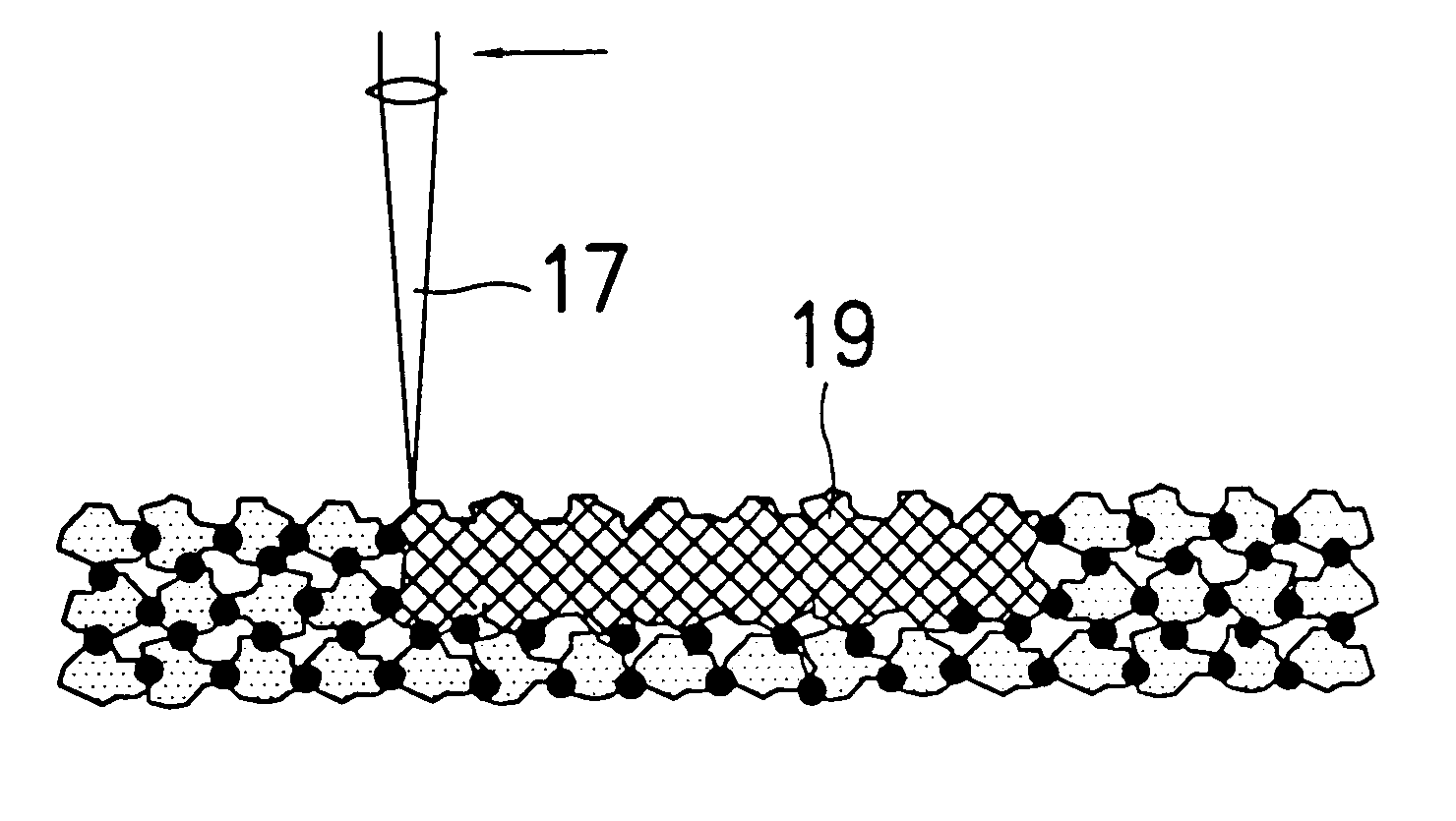

Method for rapid forming of a ceramic work piece

InactiveUS6217816B1Rapid productionPrevent dislocationAdditive manufacturing apparatusFeeding arrangmentsHeat fusionLaser beams

An inorganic binder and a dissolving agent are put into ceramic powder. They are mixed to form a plastic green mixture. Then the said mixture is formed into a thin green layer. Preferably, this thin green layer will be preheated and dried such that the thin green layer will be hardened due to the bonding effect of the inorganic binder. A portion of the thin green layer exposed under a directed high-energy beam is sintered, preferably by a laser beam, to cause ceramic molecules to bond together locally due to heat fusion. By controlling the scanning path of the high-energy beam, a two-dimensional thin cross section of the ceramic part in arbitrary form can be produced. A second thin ceramic layer can be built onto the first thin ceramic layer and bonded to it by the same method. After multiple repetitions of this procedure a three dimensional ceramic part can be fabricated layer upon layer. The green portion, which is not scanned by the high-energy beam, will be removed with suitable method. A ceramic part can be rapidly produced in this way.

Owner:NAT SCI COUNCIL

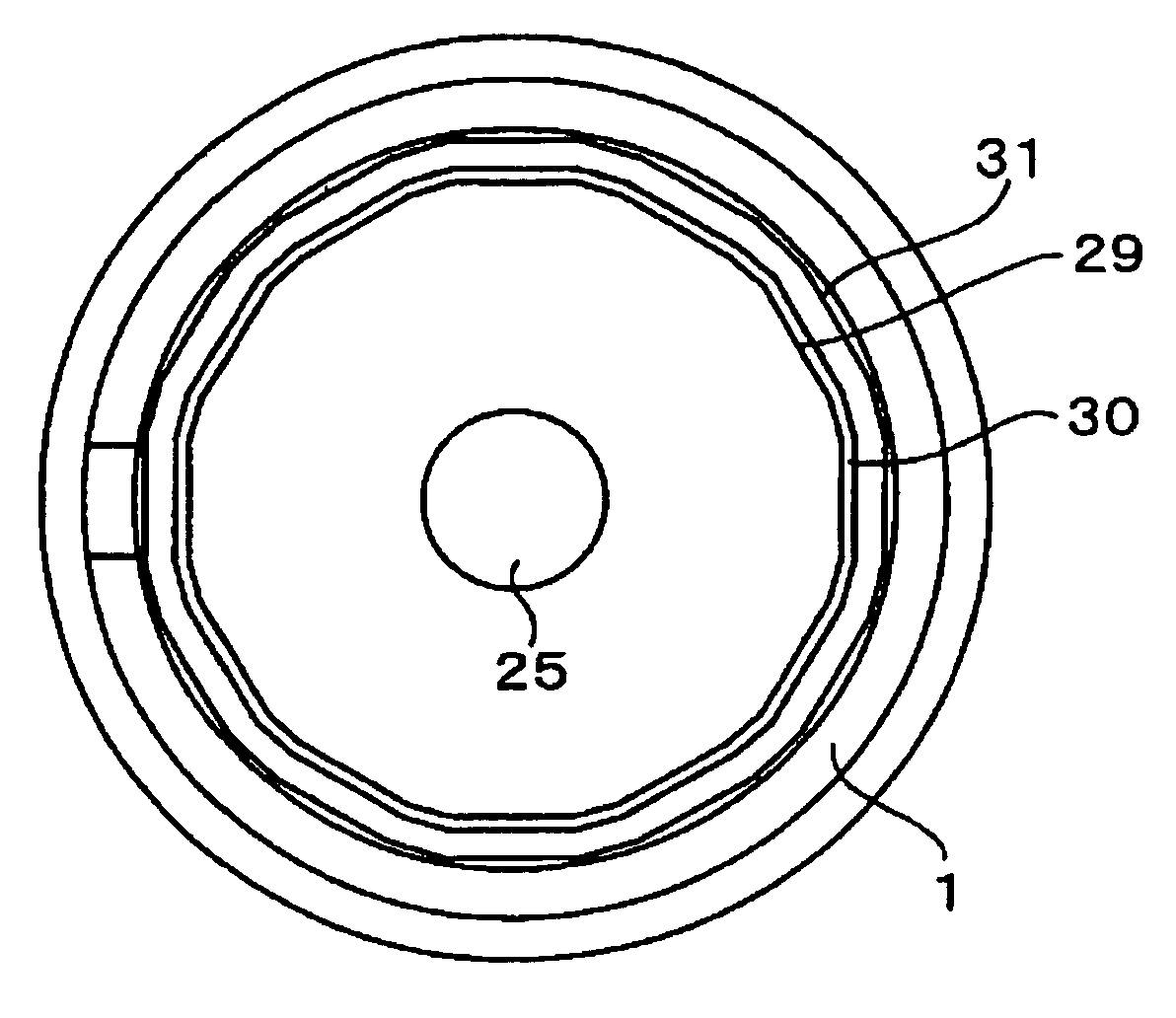

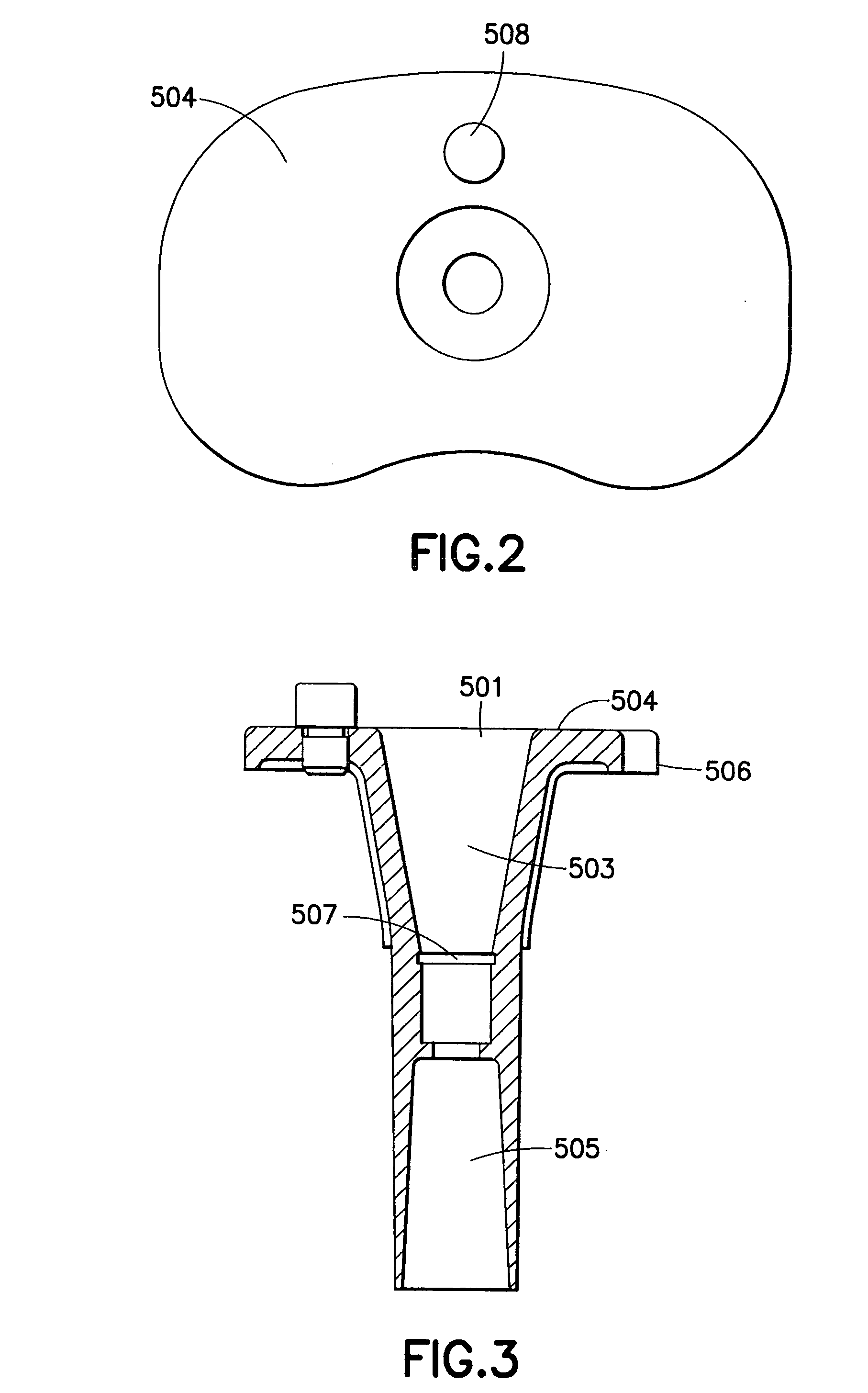

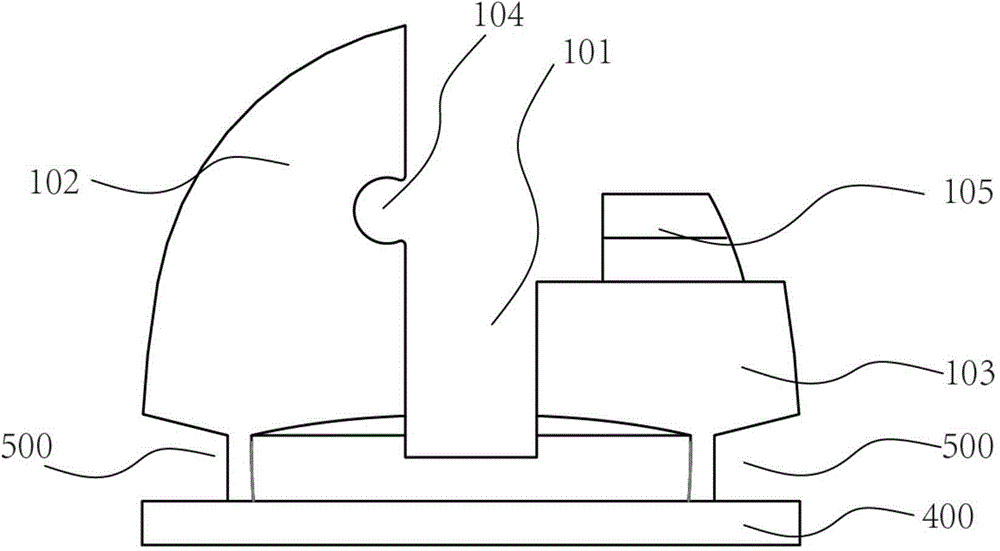

Lens device

ActiveUS7419315B2Prevent dislocationReduce misalignmentMountingsCamera body detailsCamera lensOptical axis

In a lens device, plastic lenses having circular outer periphery are placed in a plastic lens-barrel having an octagonal or more complex polygonal inner surface in such a way that the outer peripheral surfaces of the lenses are press contacted to the inner surface of the polygonal shape. This lens device has press contact portions that are pressed by the lens outer peripheral surface and the lens-barrel inner surface in the vicinity and in both sides of gate traces where optical axis displacement is large so as to suppress the displacement of the gate trace by the press contact portions.

Owner:MAXELL HLDG LTD

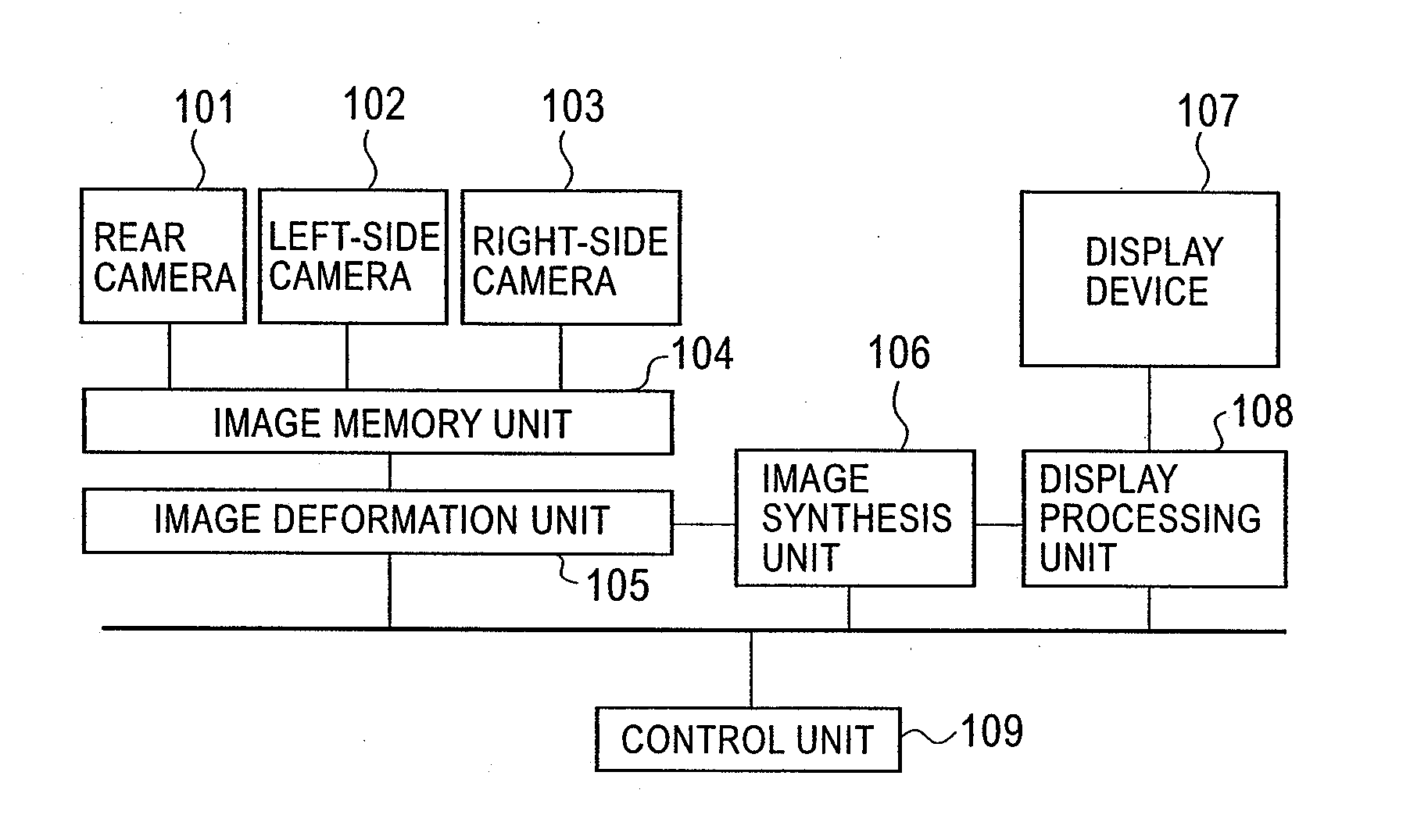

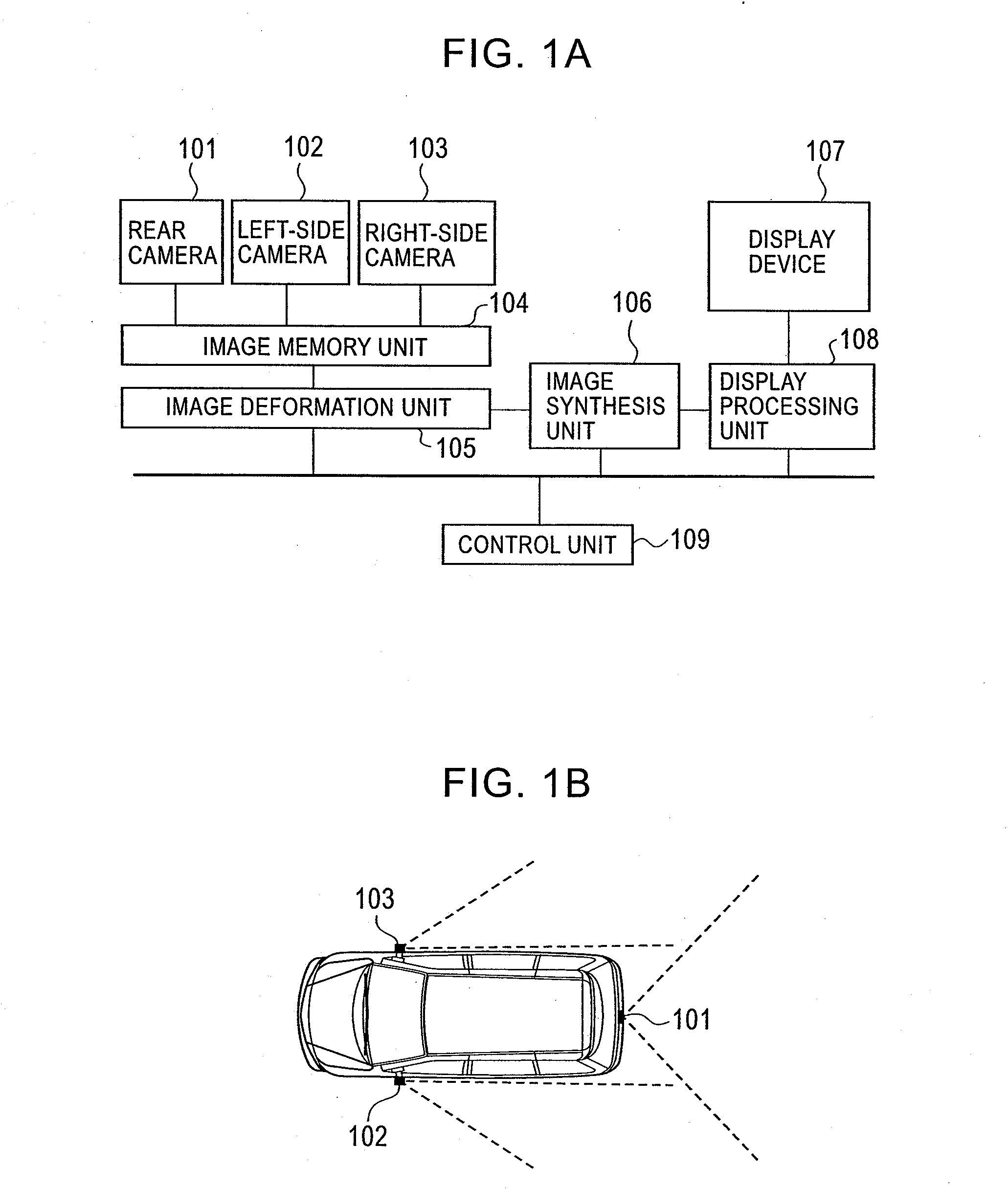

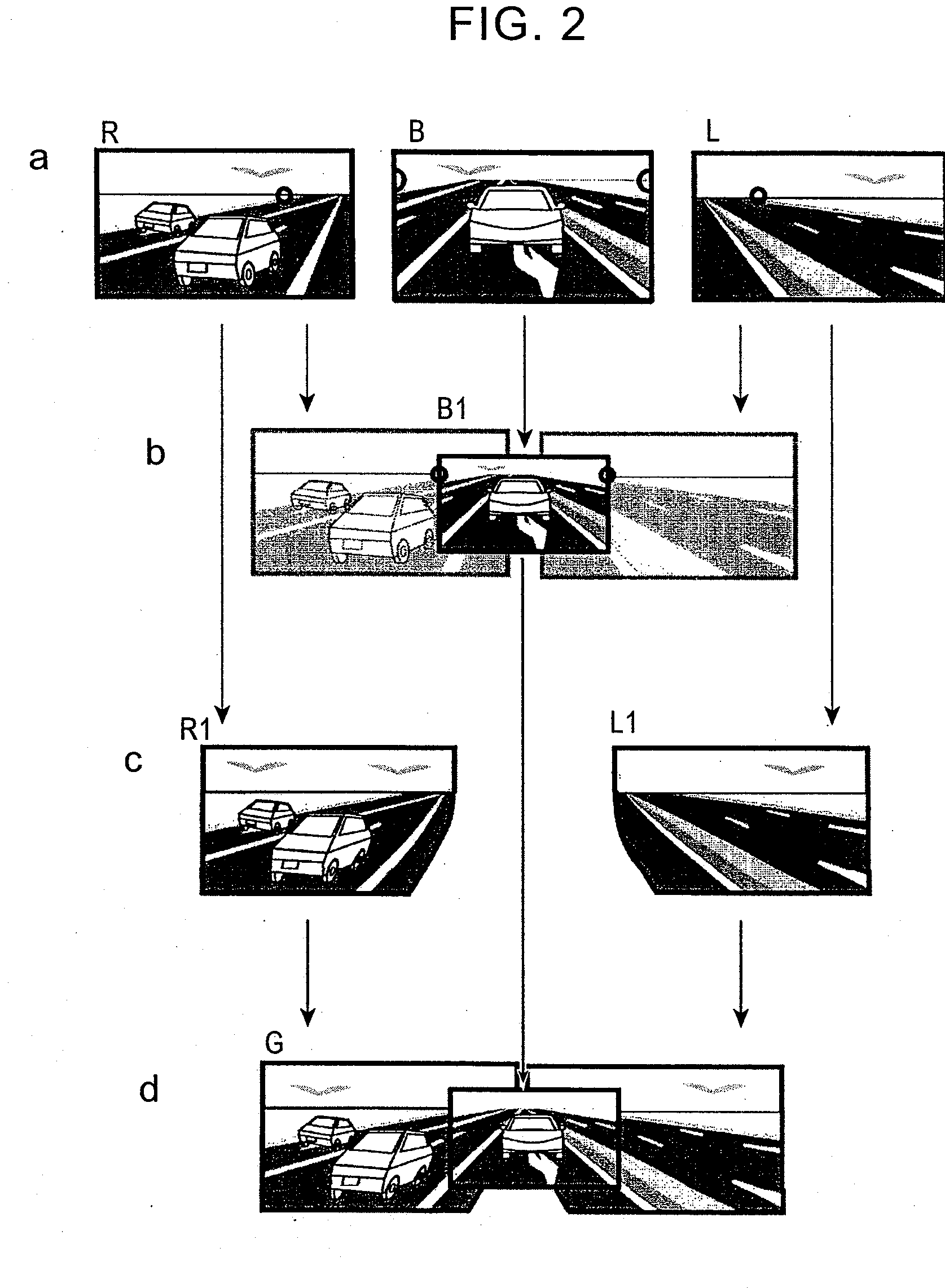

Vehicle Surrounding Image Display Device

ActiveUS20070165108A1Prevent dislocationReduce deformationCharacter and pattern recognitionColor television detailsViewpointsComputer graphics (images)

A vehicle surrounding image display device according to the present invention combines an image obtained by reducing in size an image taken by a camera provided at the center of the rear side of a vehicle, and images obtained by deforming images taken by cameras provided at the left and right sides of the vehicle such that the outward inclination of the inner side in the vehicle width direction of each of the left and right side images is gradually increased toward the lower end of the inner side. The vehicle surrounding image display device then generates a single image simulating the circumstances behind the user's own vehicle as observed from a single virtual viewpoint in a realistic form, and displays the generated image on a display device.

Owner:ALPINE ELECTRONICS INC

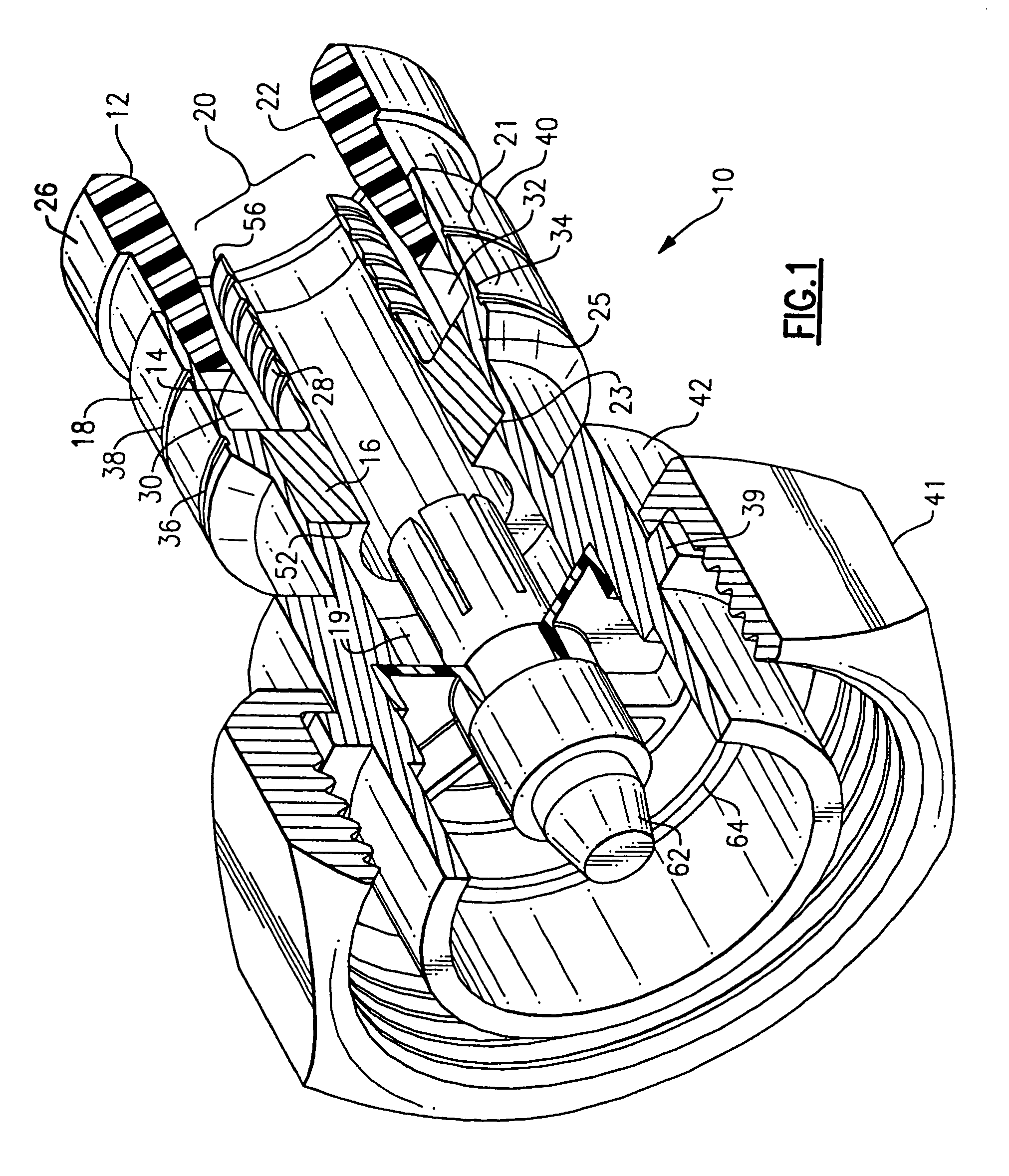

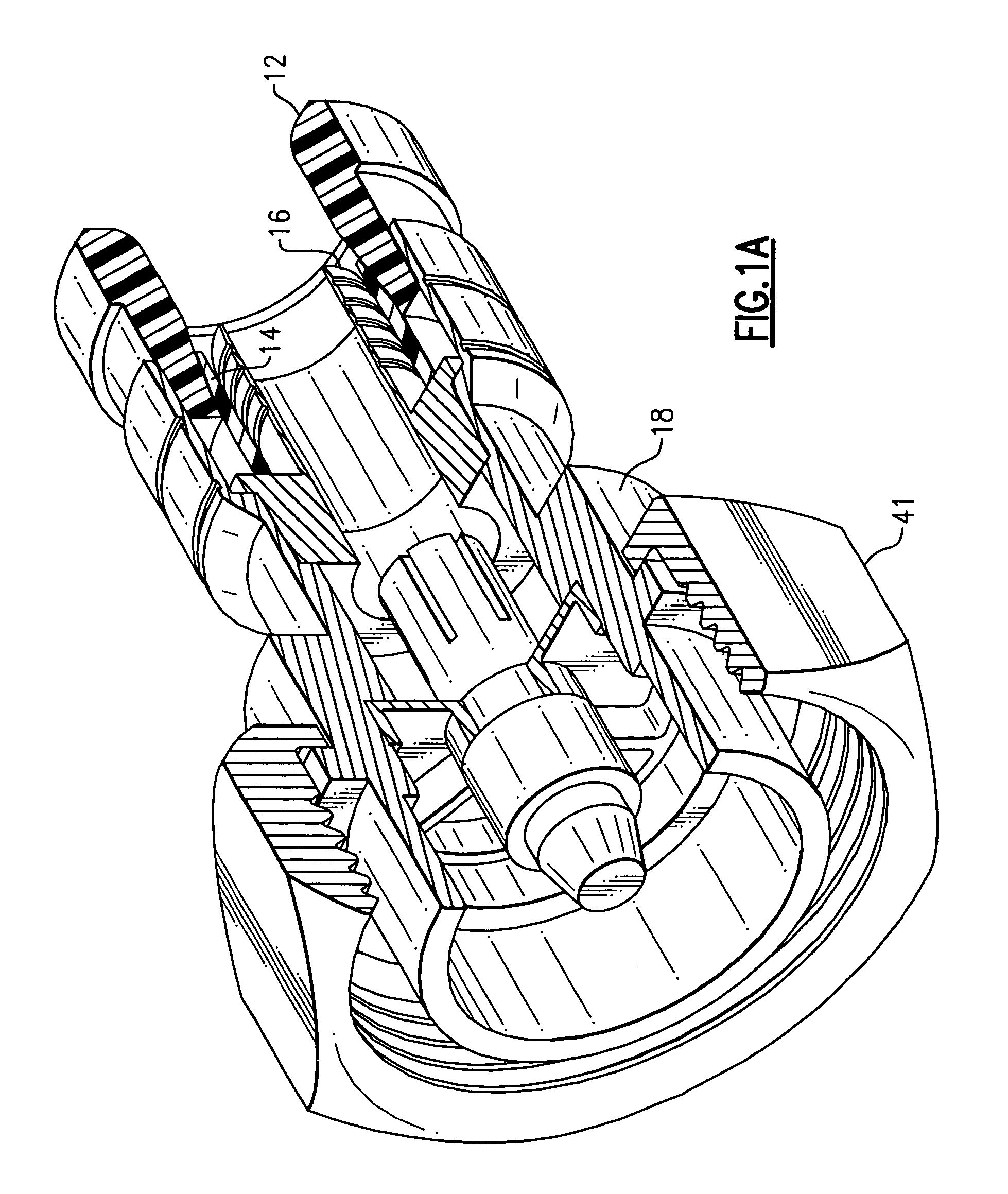

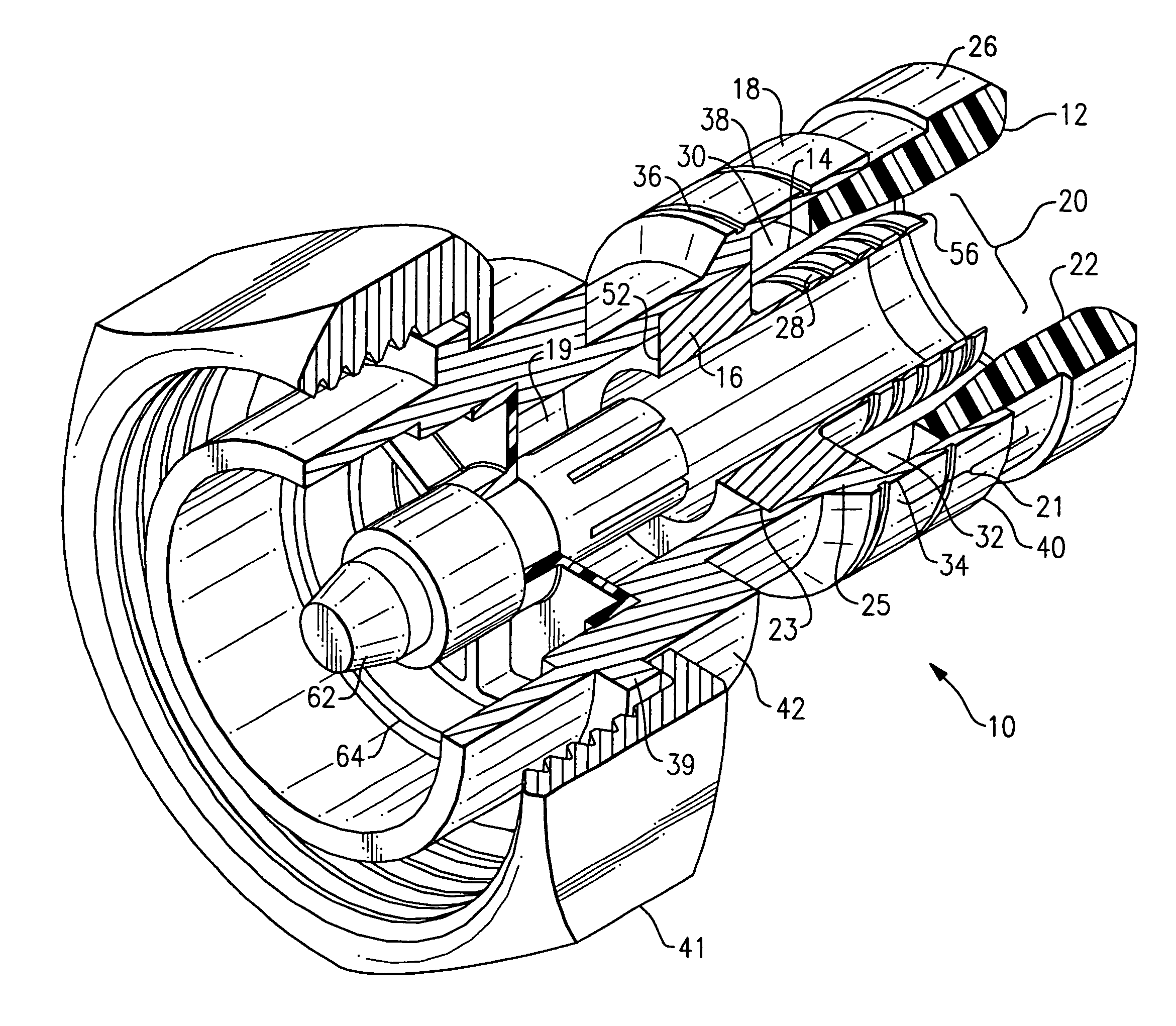

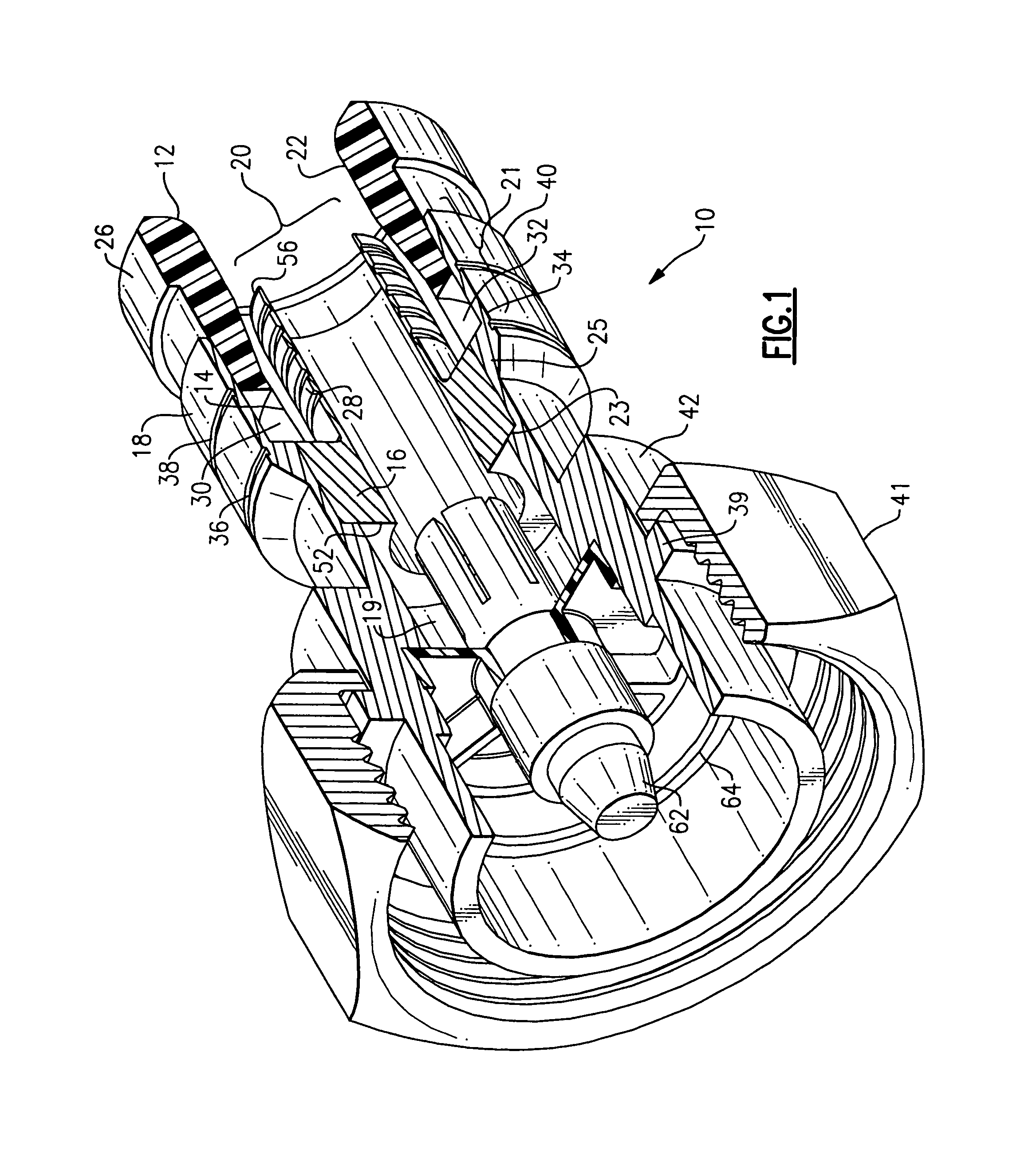

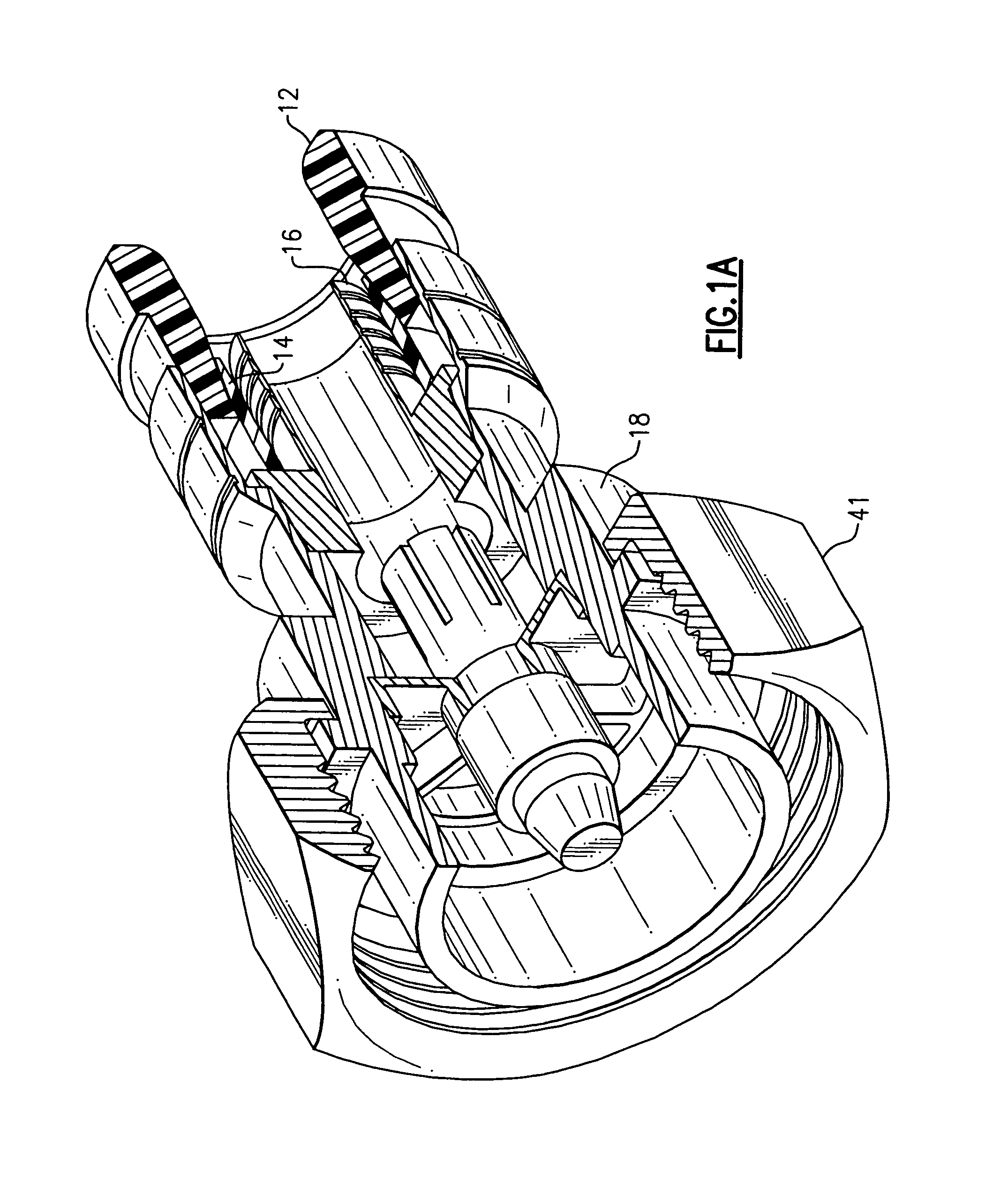

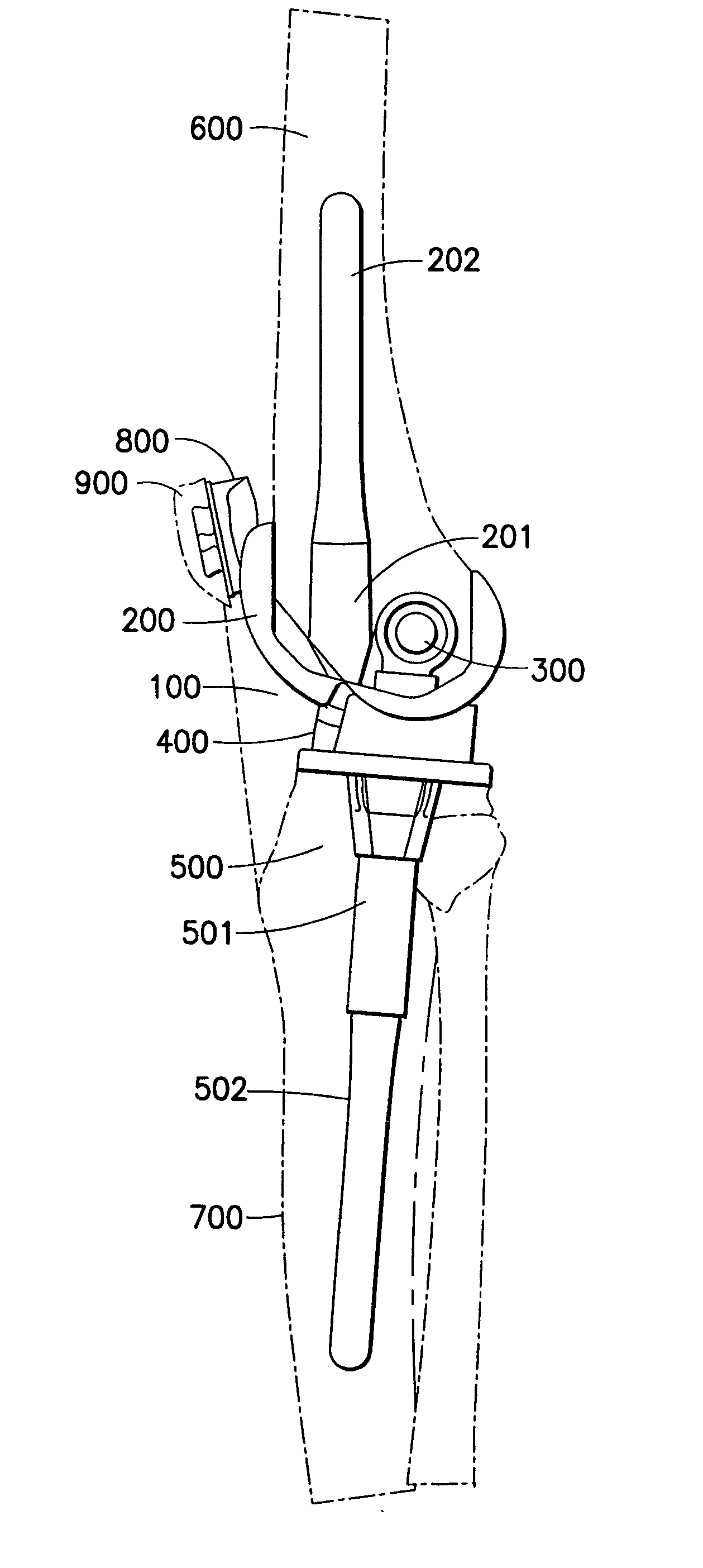

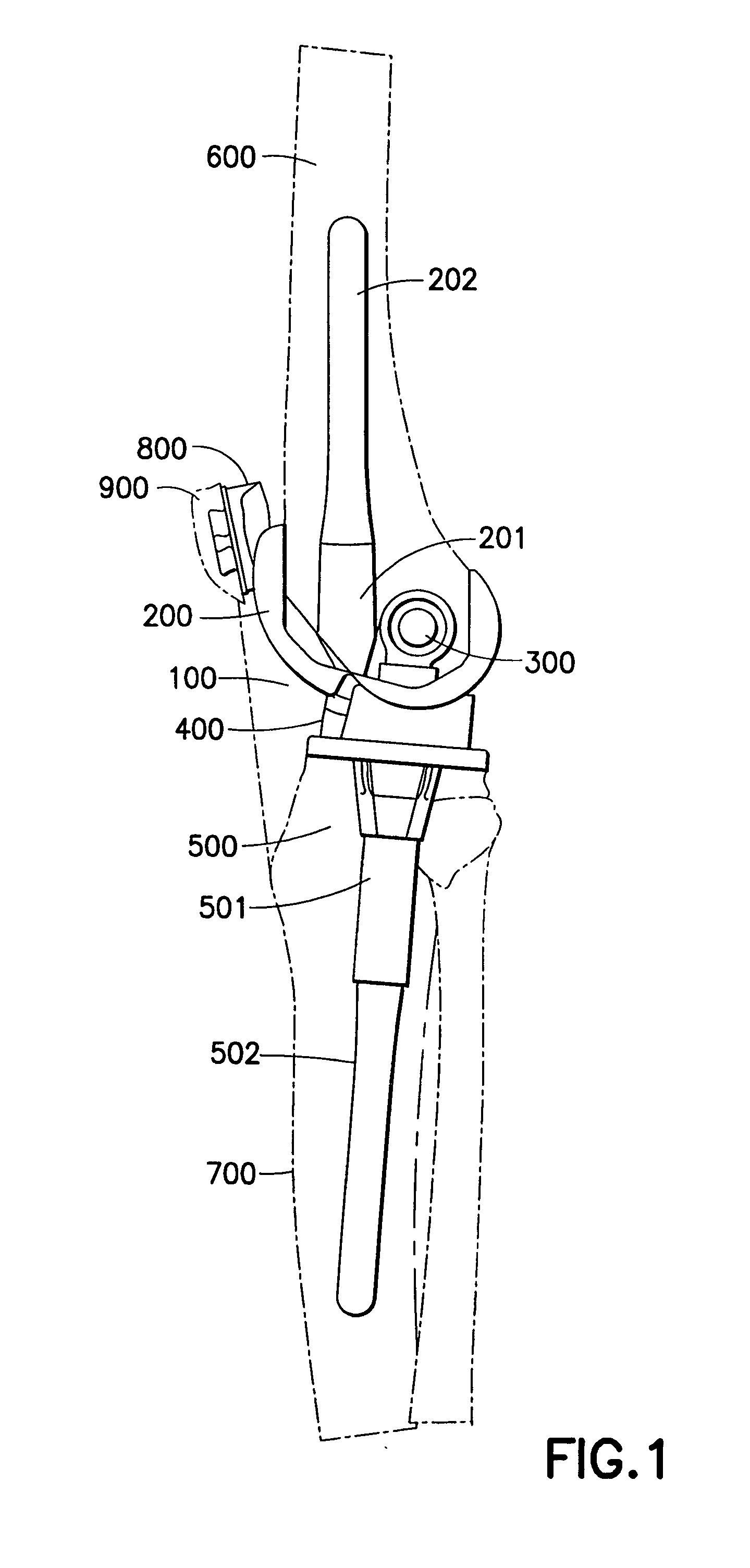

Prosthetic knee

A hinged knee prosthesis includes a femoral component with a tibiofemoral articular surface that is distinct from the patellofemoral articulating surface. Fully congruent tibiofemoral articulation is provided for virtually all flexion angles. Additionally, the bearing is capable of at least limited axial rotation relative to the tibial component but is restrained against dislocation. Accordingly, dislocation is much less likely even n those situations where collateral ligaments are insufficient.

Owner:BUECHEL PAPPAS TRUST

Compression connector for coaxial cable

ActiveUS7048579B2Reduce distanceReducing required insertion lengthElectrically conductive connectionsTwo pole connectionsCoaxial cableCompression member

A coaxial cable compression connector includes a connector body having a first end and a second end, and an internal passageway. The compression connector further includes a tubular post having a first end configured for engagement with the conductive grounding sheath of the coaxial cable and a second end configured for engagement with the internal passageway of the body. The connector further includes a compression member. The first end of the compression member includes an outer surface and a tapered inner surface, the outer surface is configured for engagement with a portion of the internal passageway at the first end of the body. The connector further includes a ring member which is configured for engagement with the tapered inner surface of the compression member.

Owner:RF IND

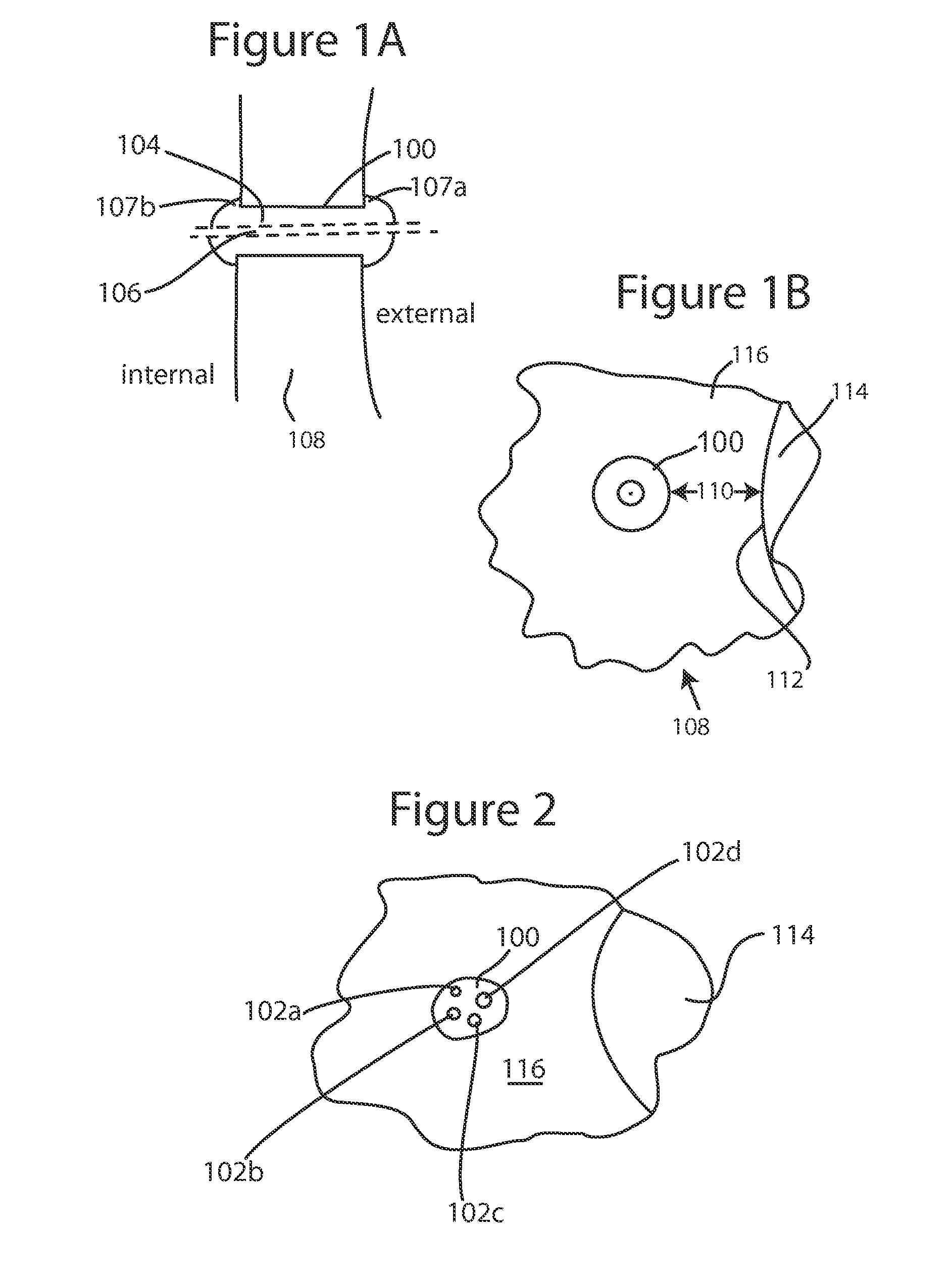

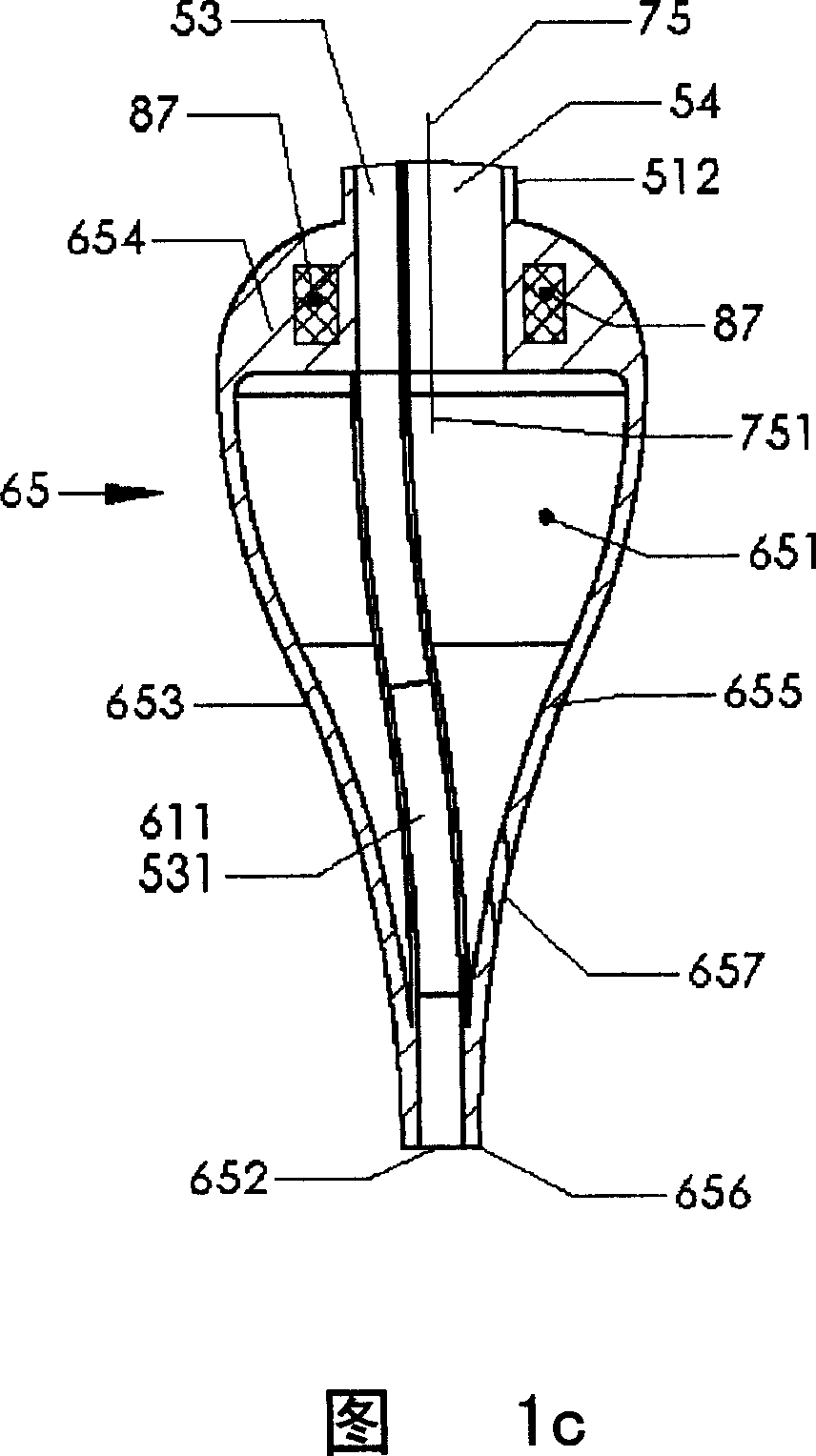

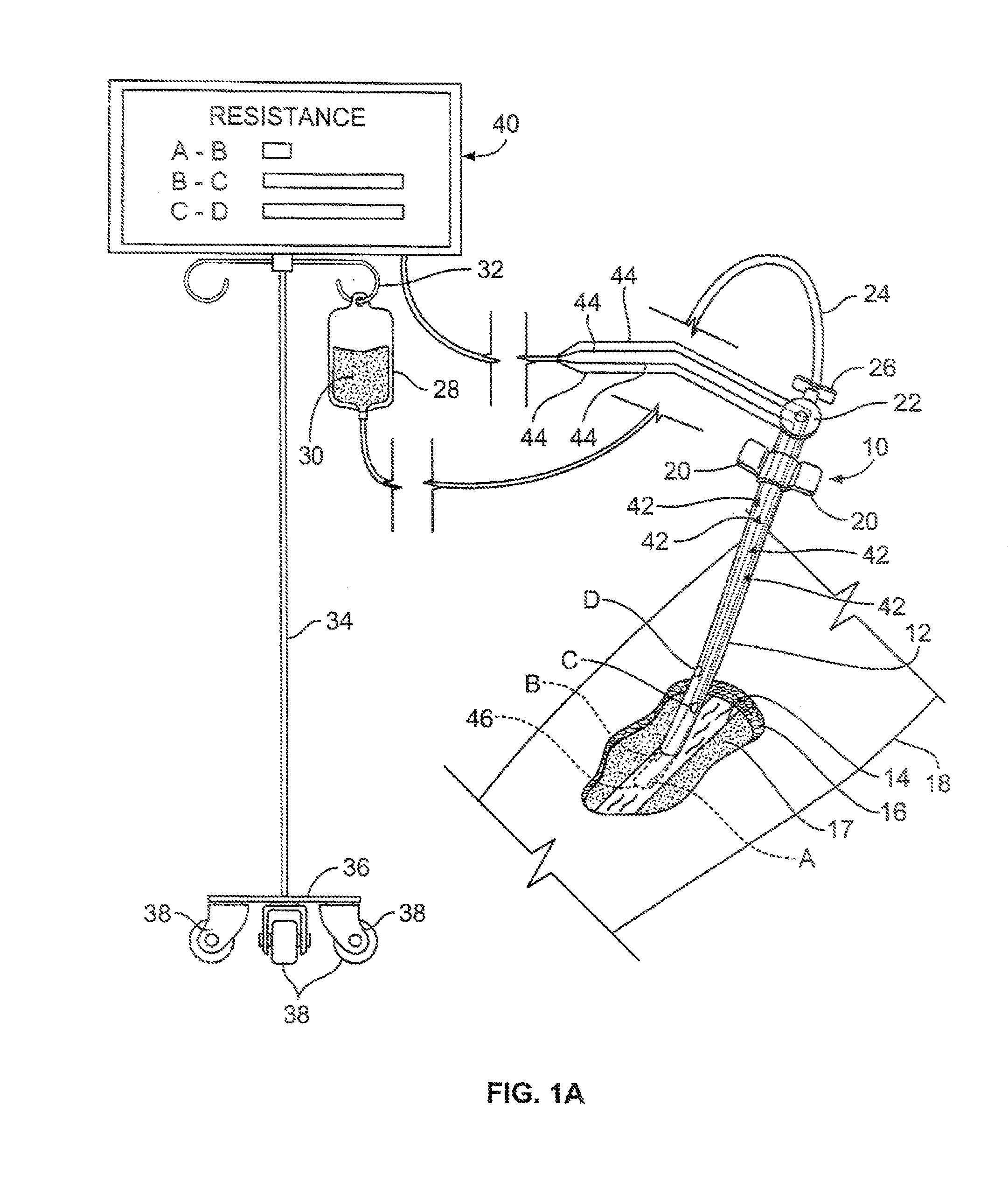

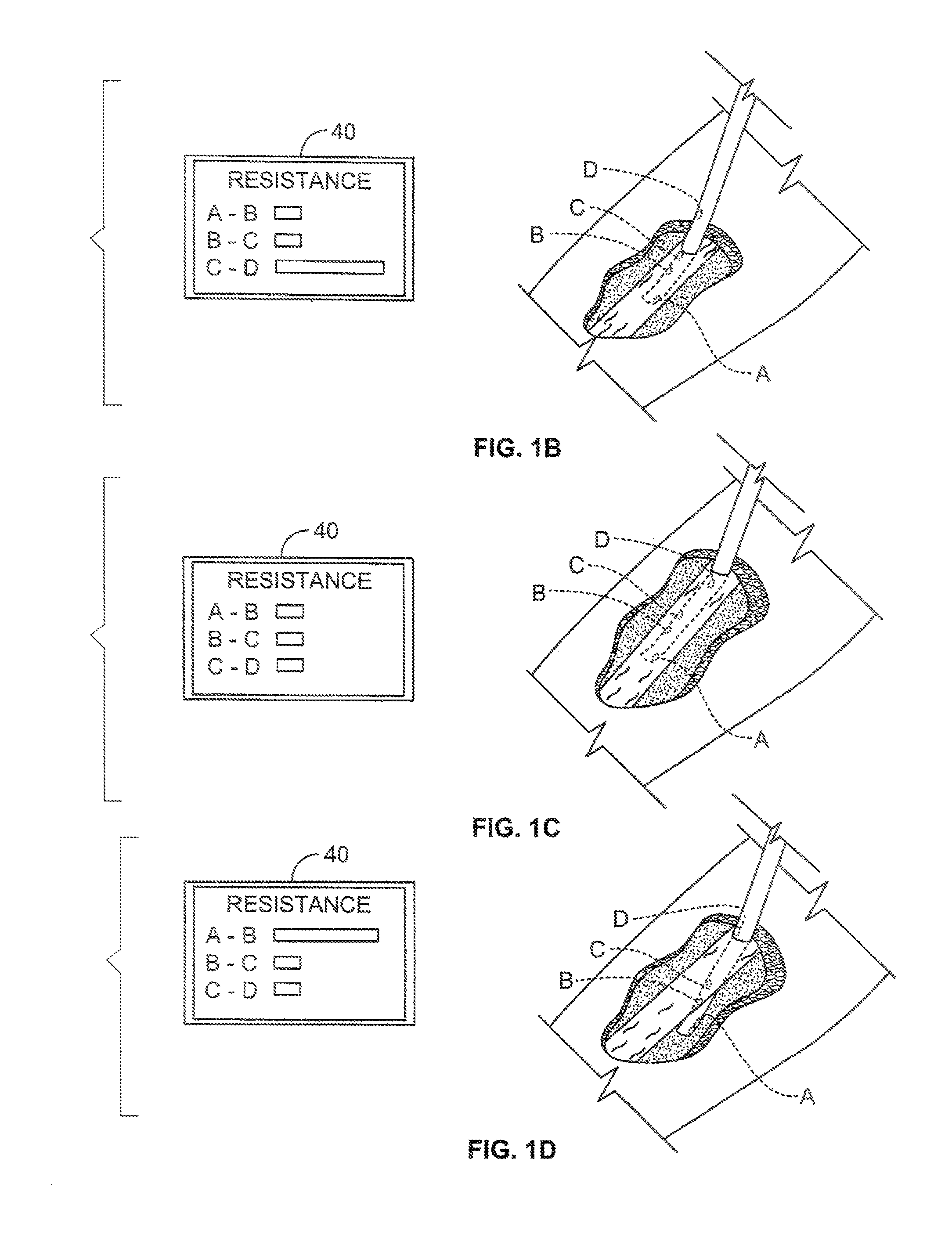

Glaucoma drainage device and uses thereof

InactiveUS20120089073A1Elevated intraocular pressure or glaucomaPrevent dislocationEye surgeryNanomedicineElevated intraocular pressureImplanted device

In one aspect, the present invention provides an implant device for use in an eye with elevated intraocular pressure or glaucoma. In another aspect, the present invention provides a method for lowering intraocular pressure and / or treating a condition associated with elevated intraocular pressure using the implant device of the present invention.

Owner:CUNNINGHAM JR EMMETT T

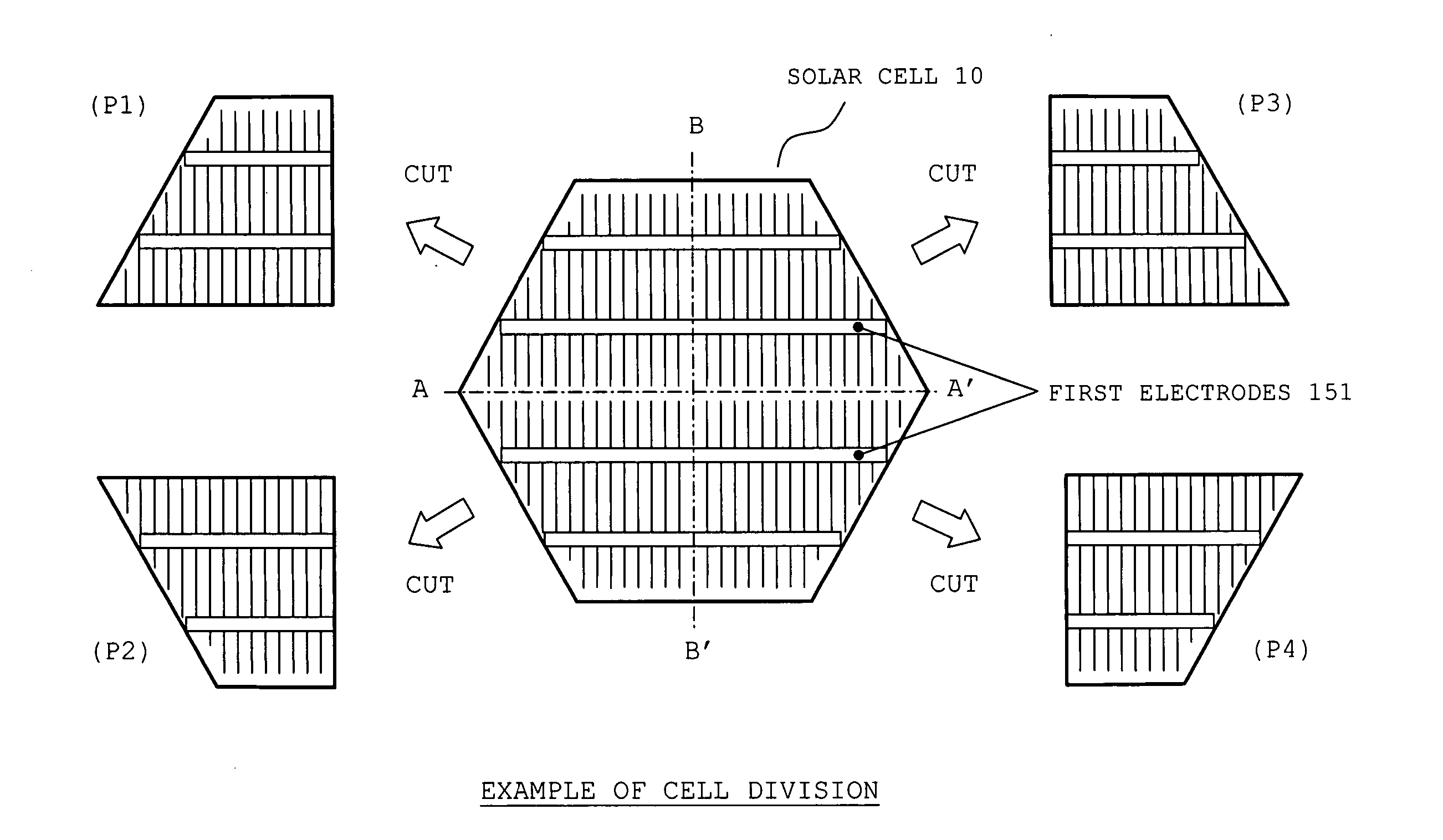

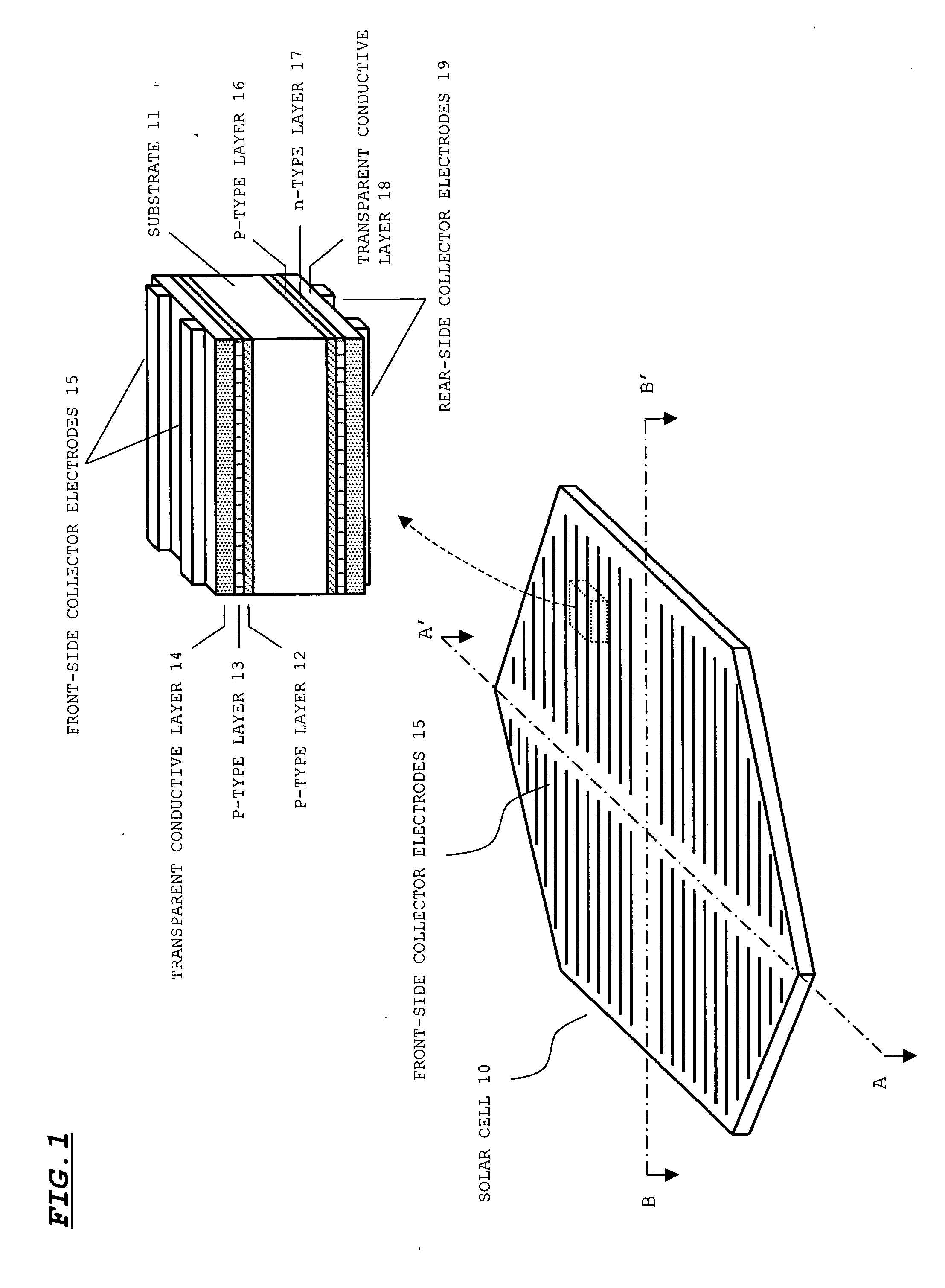

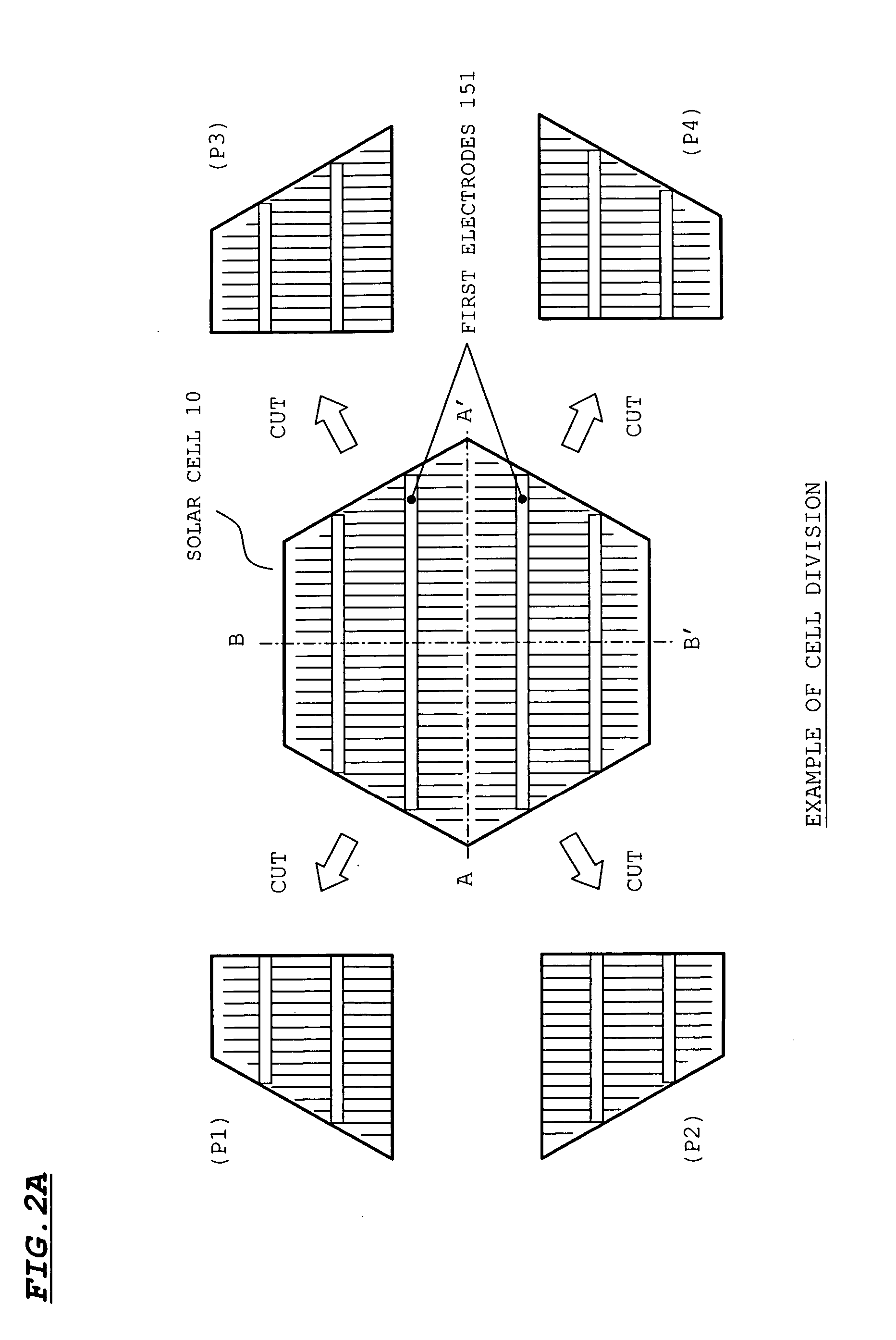

Manufacturing method of solar cell module, and solar cell and solar cell module

ActiveUS20070074756A1Electrical connectionConvenient ArrangementPV power plantsPhotovoltaic energy generationElectricityEngineering

A double-side light receiving solar cell in a planer regular hexagon shape and having first electrodes on both surfaces are divided into four pieces by a line A-A′ connecting two opposing apexes and by a line B-B′ perpendicular to the line A-A′ and connecting center points on two opposing sides. By matching oblique lines of two divided pieces without misalignment and with respective surfaces in an inversed state, the first electrodes on the same side of the two divided pieces align along the same single straight line. Then, the first electrodes that are on the same side are connected with a first inter connecter, thereby constructing a unit having a rectangular outline. Units thus constructed are arranged so that relevant sides match without misalignment. By handling on a unit basis as described above, it is possible to facilitate an arrangement of the cells and an electricity connection work.

Owner:SANYO ELECTRIC CO LTD

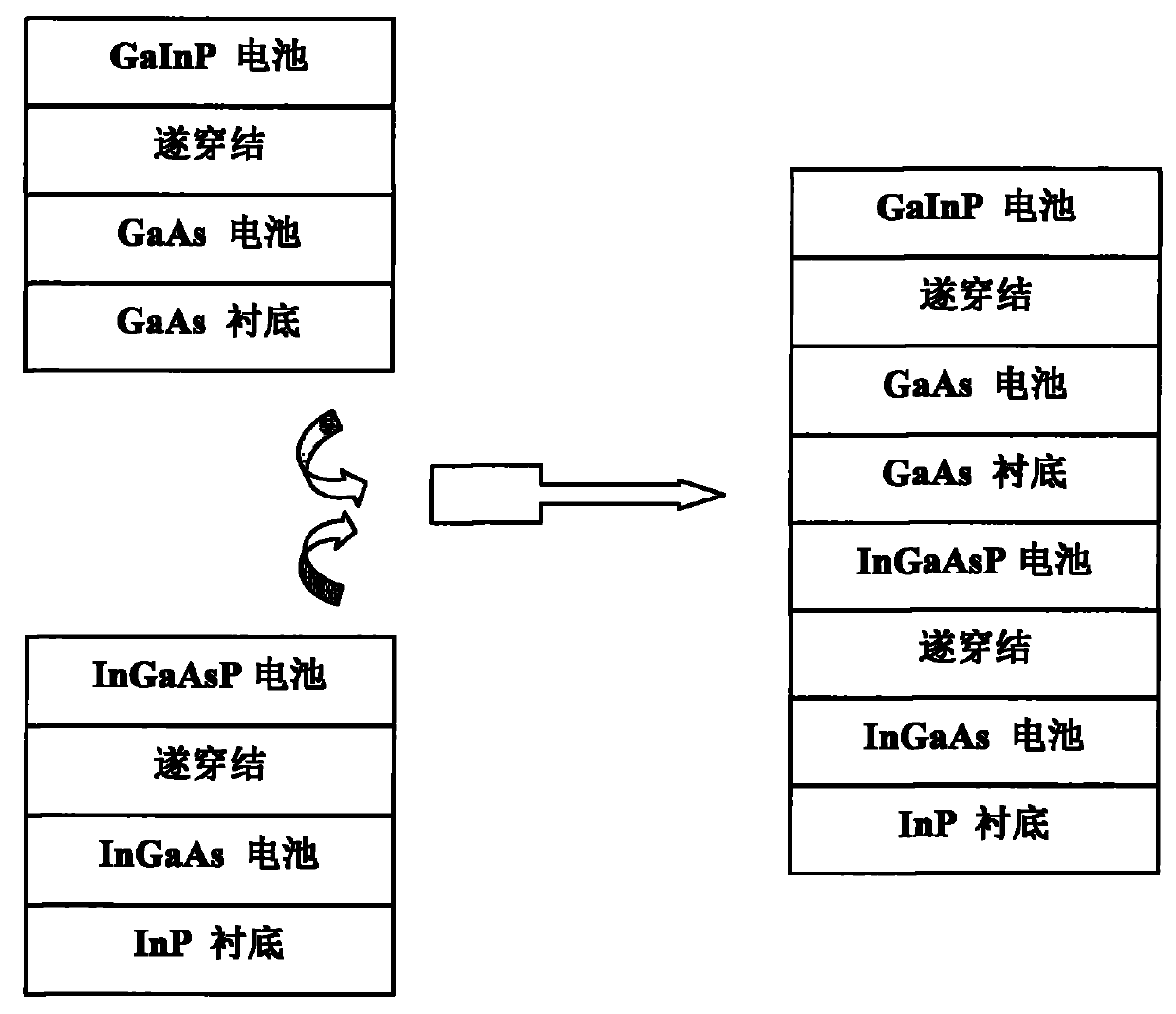

Manufacturing method of GaInP/GaAs/InGaAsP/InGaAs four-junction solar battery

InactiveCN101950774AReduce heat lossAchieve absorptionFinal product manufactureSemiconductor devicesBand gapCell material

The invention discloses a manufacturing method of a GaInP / GaAs / InGaAsP / InGaAs four-junction solar battery. By utilizing a wafer bonding method, the GaInP / GaAs / InGaAsP / InGaAs four-junction solar battery is integrated by a GaInP / GaAs double-junction solar battery growing based on a GaAs substrate and a InGaAsP / InGaAs double-junction solar battery growing based on an InP substrate; by utilizing the InP as a supporting substrate, the four-junction solar battery with respective band gap energies of 1.9 / 1.4 / 1.05 / 0.72 eV is realized, sunlight full spectral absorption and energy conversion are realized to a greater degree, and 32.8 percent of efficiency is realized in irradiation of AM1.5G and under the sun. Based on the development of two kinds of double-junction batteries, the bonded four-junction solar battery reduces the shortages of high cost caused by utilizing a plurality of different substrates in a mechanical cascade solar battery system and complex optical system and optical loss in an optical integrated battery, and effectively solves the problem of lattice mismatching of growing a uniwafer four-junction cascade semiconductor solar battery material. The high voltage and low current outputs are realized and the resistance consumption in a high concentrator battery is reduced.

Owner:SUZHOU INST OF NANO TECH & NANO BIONICS CHINESE ACEDEMY OF SCI

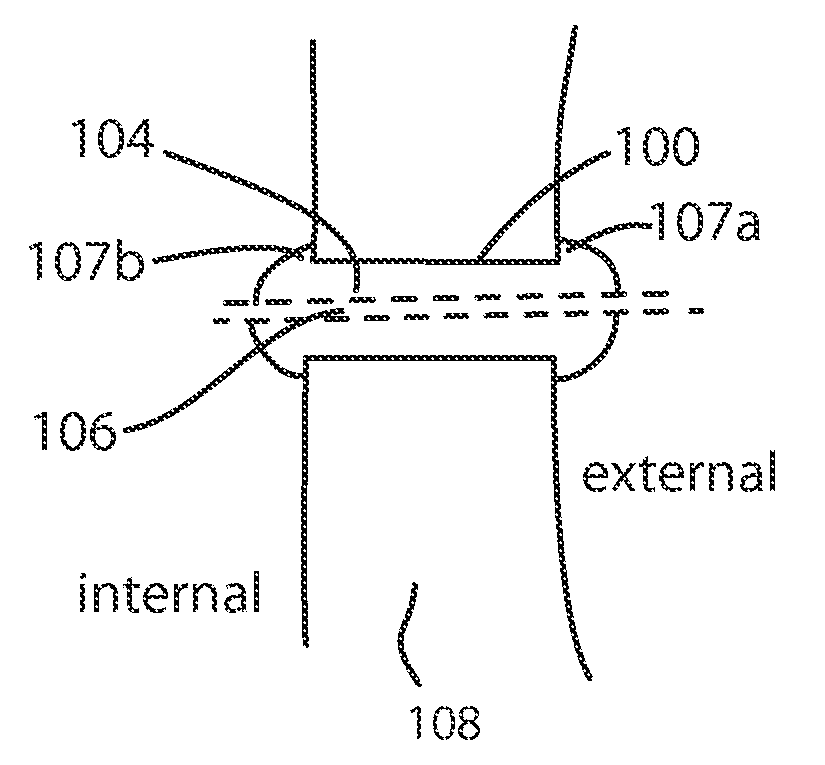

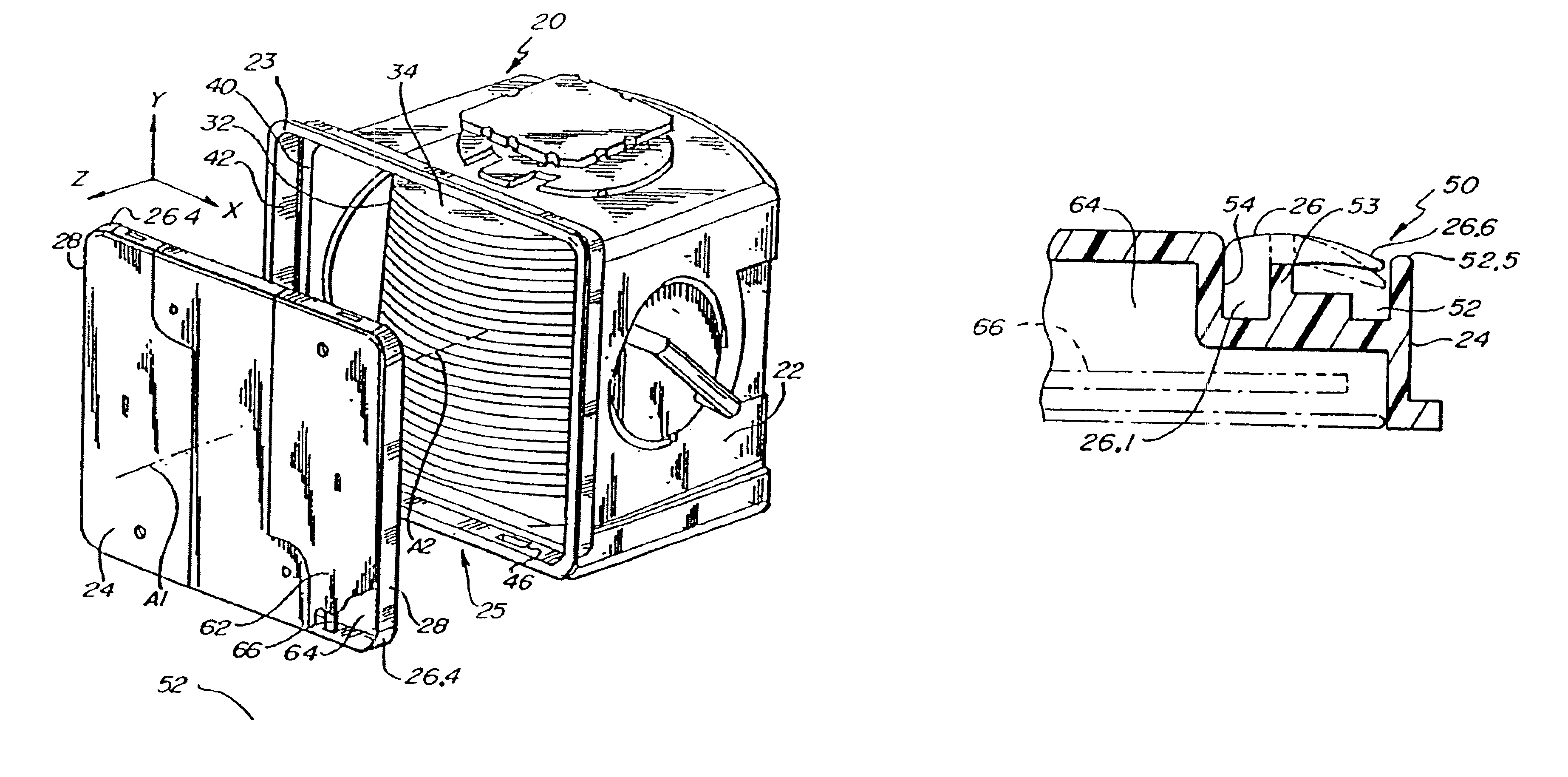

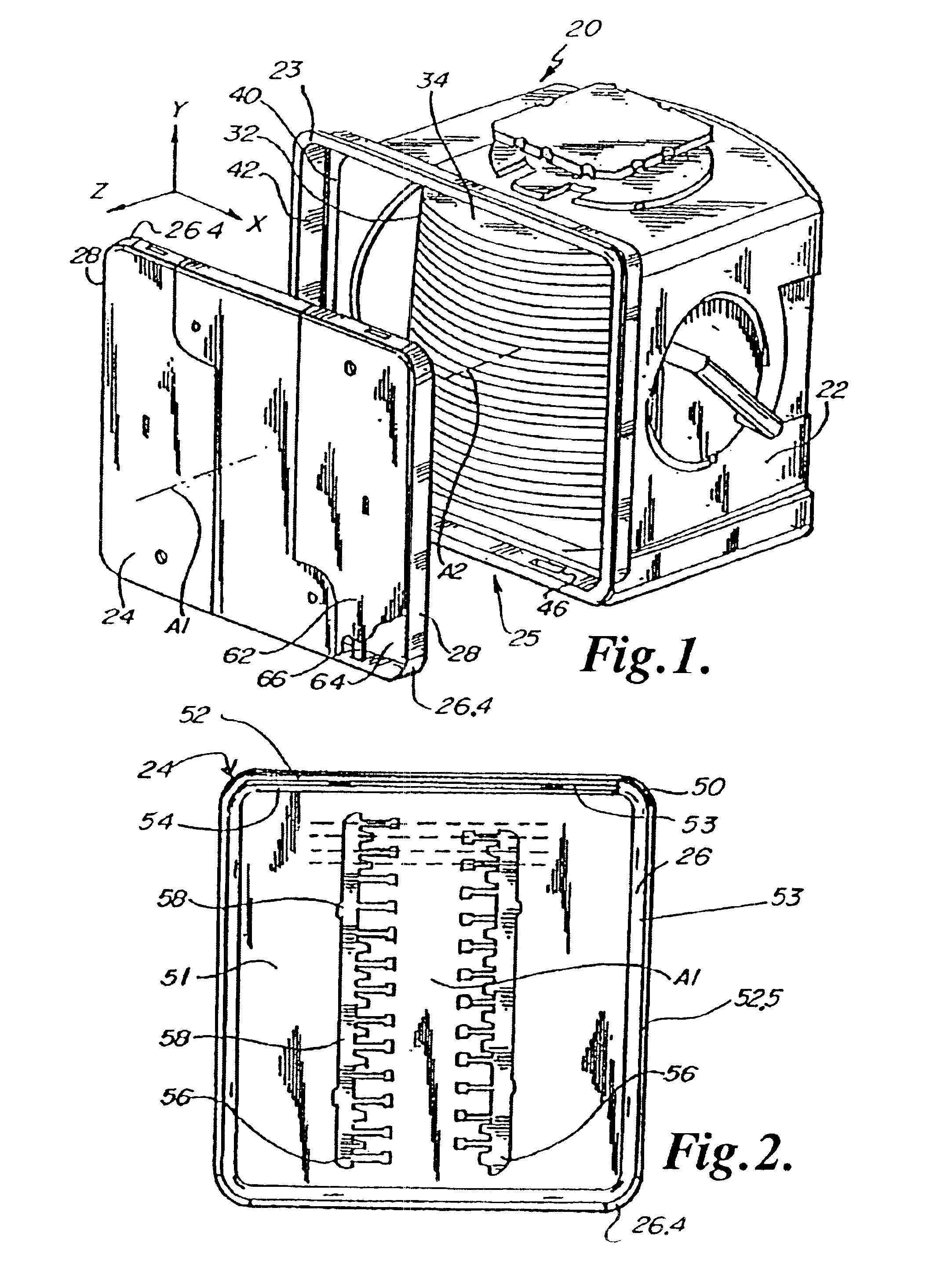

Wafer enclosure sealing arrangement for wafer containers

InactiveUS6848578B2Prevent dislocationPrevent lateral movementEngine sealsSemiconductor/solid-state device manufacturingElectrical and Electronics engineering

A wafer container comprises a housing with a door frame, defining an opening for insertion and removal of wafers, and a door for insertion into the door frame. The door includes a wafer enclosure sealing arrangement for hermetically sealing the door with the door frame of the housing. The wafer enclosure sealing arrangement includes a first groove disposed about a perimeter of the interior surface of the door and a second groove disposed adjacent to the first groove and spaced laterally from the perimeter of the door. The sealing arrangement includes a support member disposed between the first and second grooves. The sealing arrangement also includes an elastomeric seal member having a first portion that is frictionally inserted into the second groove and extends around the door and a second portion that cantilevers downward into the second groove when the door and housing are joined.

Owner:ENTEGRIS INC

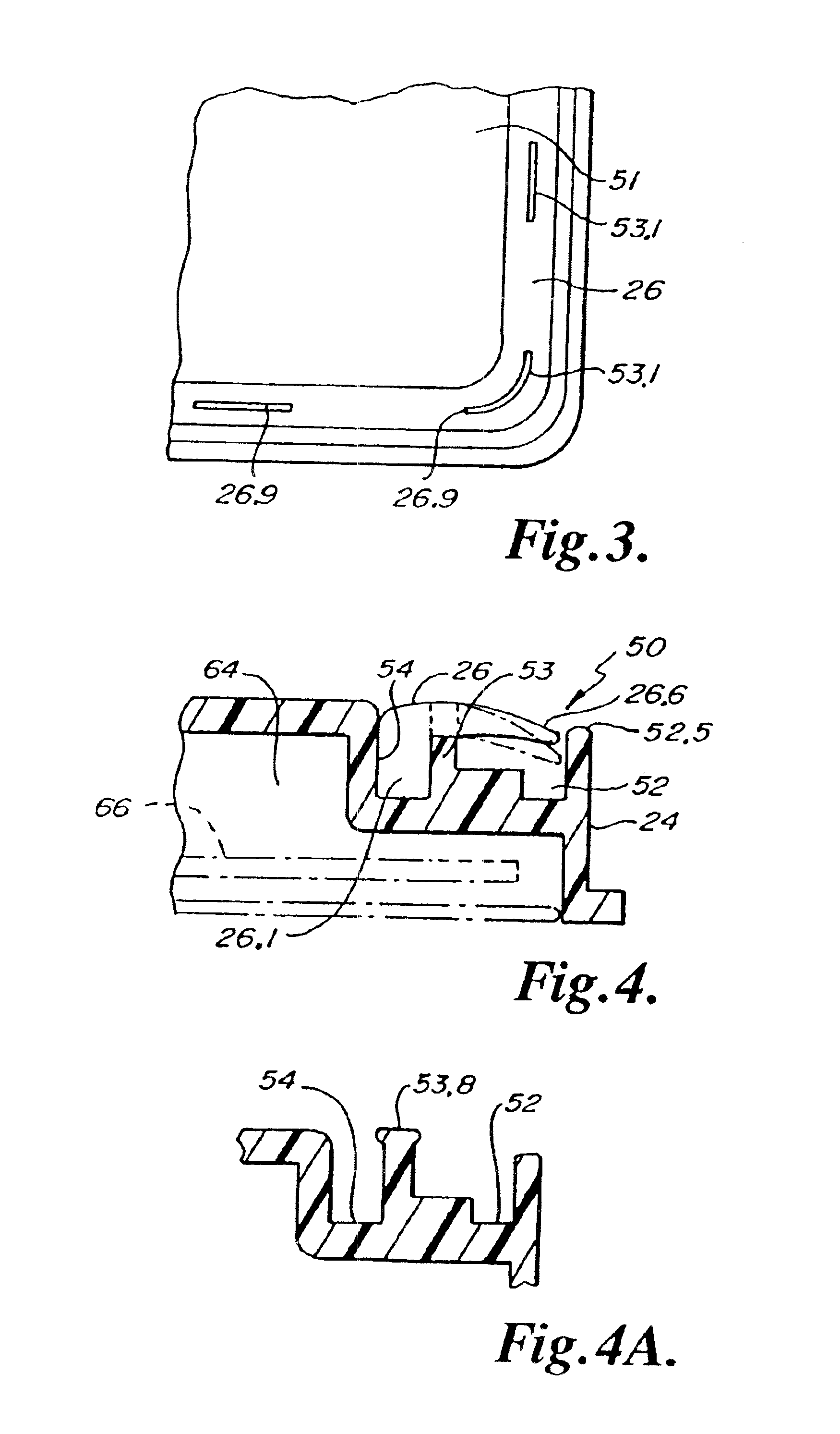

Modified self-insulating composite external wall material

InactiveCN102040361ANo damageMissing edges and cornersSolid waste managementCeramicwarePolyvinyl chlorideShock resistance

The invention discloses a modified self-insulating composite external wall material, and belongs to a gypsum building material. The material comprises the following components in percentage by weight: 75 to 84 percent of gel material, 0.2 to 1.5 percent of heat insulating material, 3 to 6 percent of modifying agent and 12 to 18 percent of water; the gel material consists of gypsum, fly ash, cement and lime, wherein the gypsum and the fly ash are in the majority; the heat insulating material is one or more of polyphenyl granules, rice hulls, straws, saw dust and expanded perlite; and the modifying agent is a common salt compound or a mixture of the common salt compound, aluminum powder and polyvinyl chloride (PVC) latex powder. The external wall material for manufacturing external wall building blocks or external wallboards by optimized proportion and modification treatment remarkably improves the comprehensive performance of water prevention, heat insulation, shock resistance and pressure resistance; and production and construction are convenient, the raw materials are easily obtained, industrial and agricultural byproducts are fully utilized, and environmentally-friendly and energy-saving requirements are met.

Owner:李宁 +1

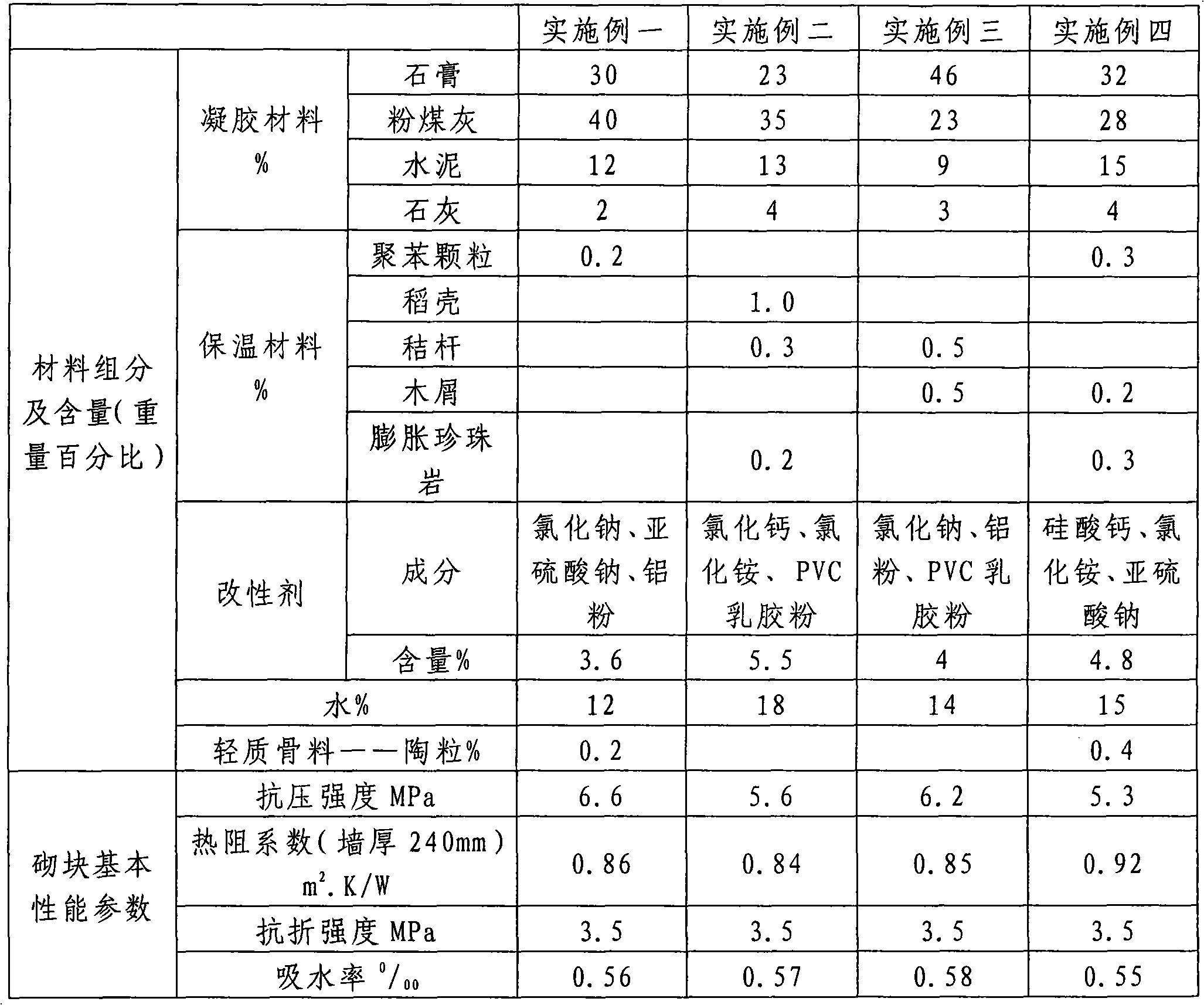

Image processing apparatus and method therefor

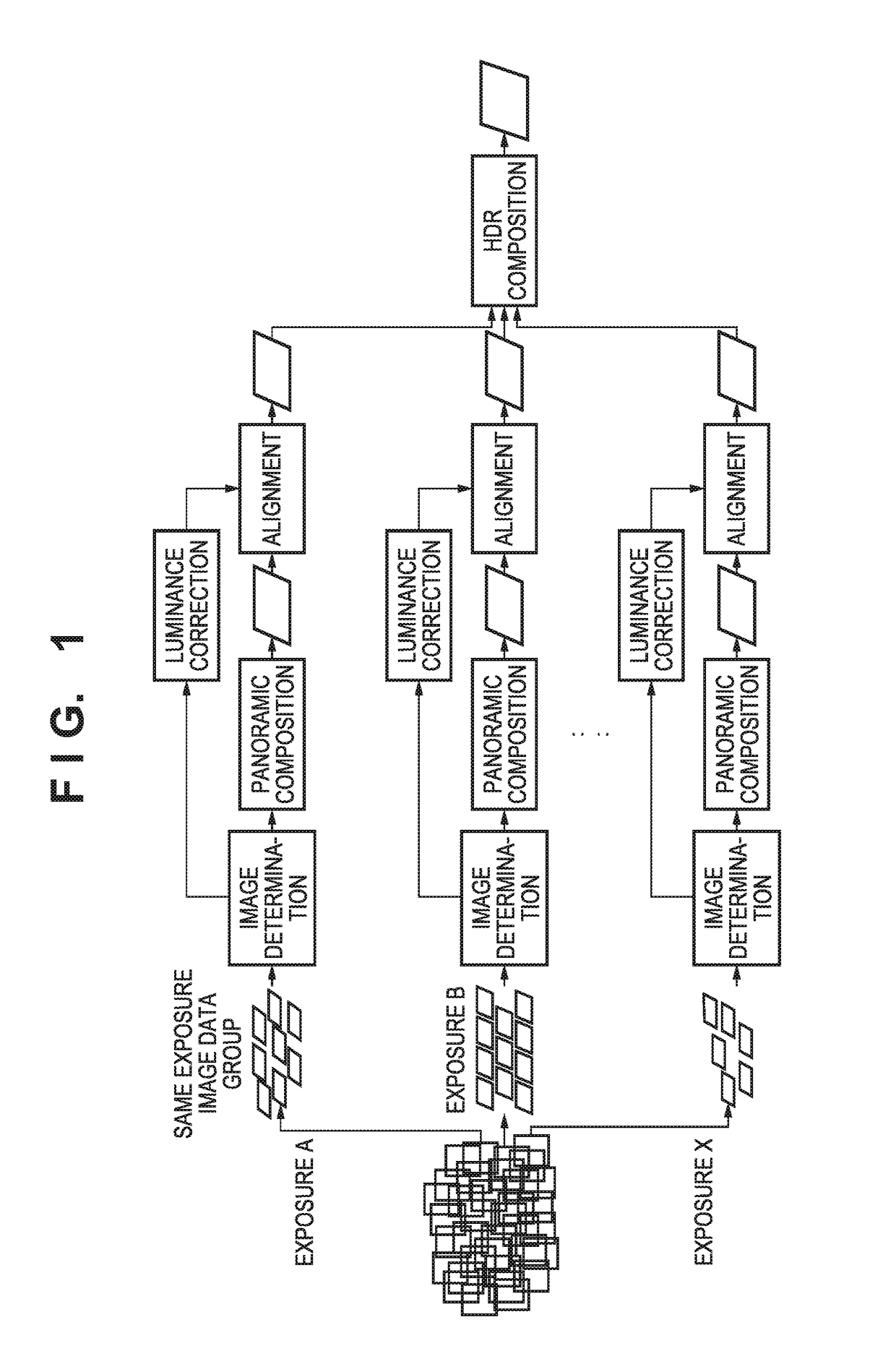

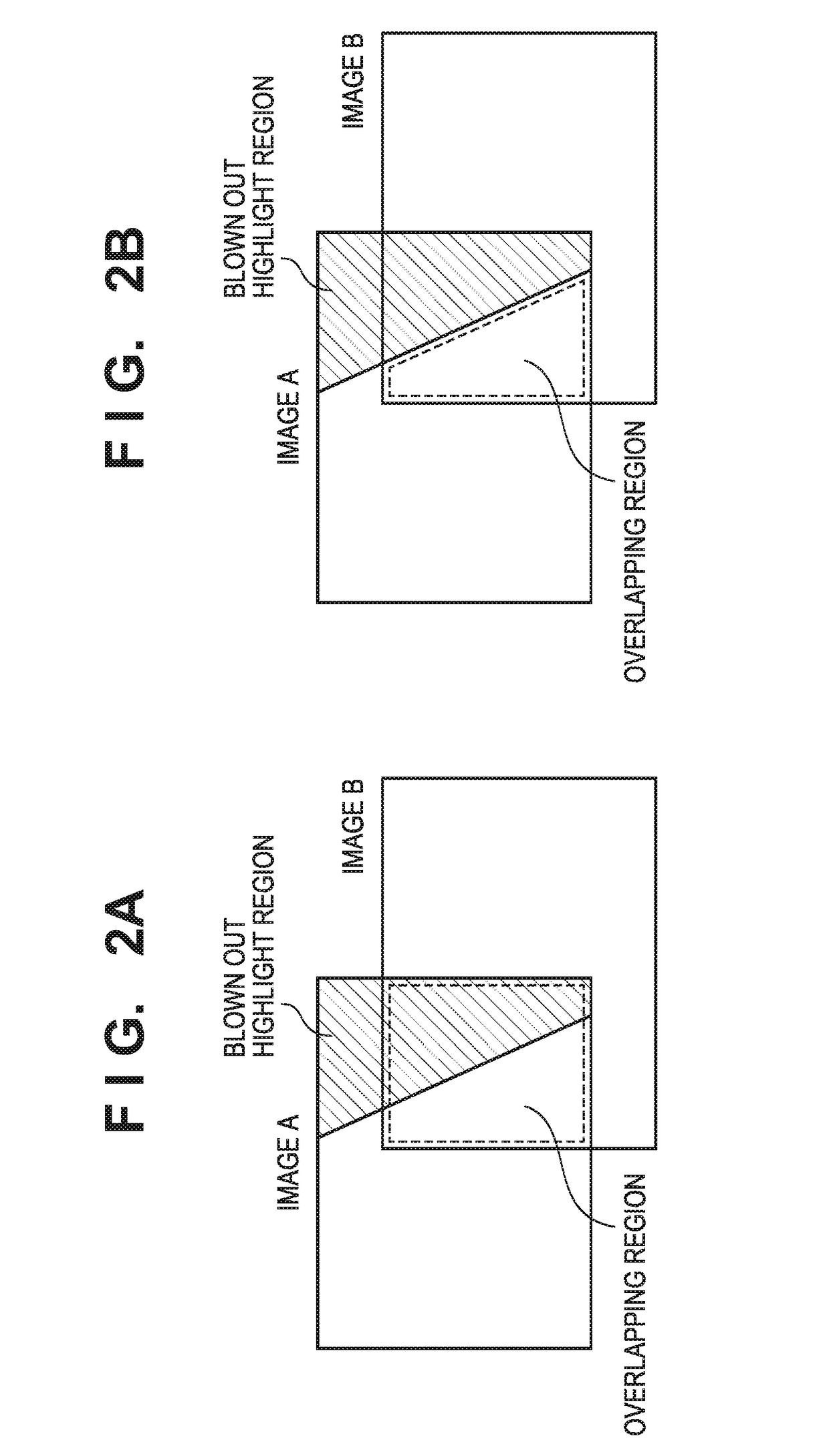

ActiveUS20170230577A1High imagingMisalignment of the joint between the images is suppressedImage enhancementTelevision system detailsImaging processingImaging data

An image processing apparatus comprises an input unit configured to input a plurality of image data shot with a plurality of different exposures; a determination unit configured to determine whether each of the plurality of image data includes an exposure defect; a generation unit configured to generate a plurality of panoramic images respectively corresponding to the plurality of exposures by panoramically composing a plurality of image data shot with the same exposure based on a result of the determination; an alignment unit configured to perform alignment between the plurality of panoramic images using image data determined not to include the exposure defect and image data obtained by performing luminance correction for image data determined to include the exposure defect; and a composition unit configured to perform high dynamic range composition for the plurality of aligned panoramic images.

Owner:CANON KK

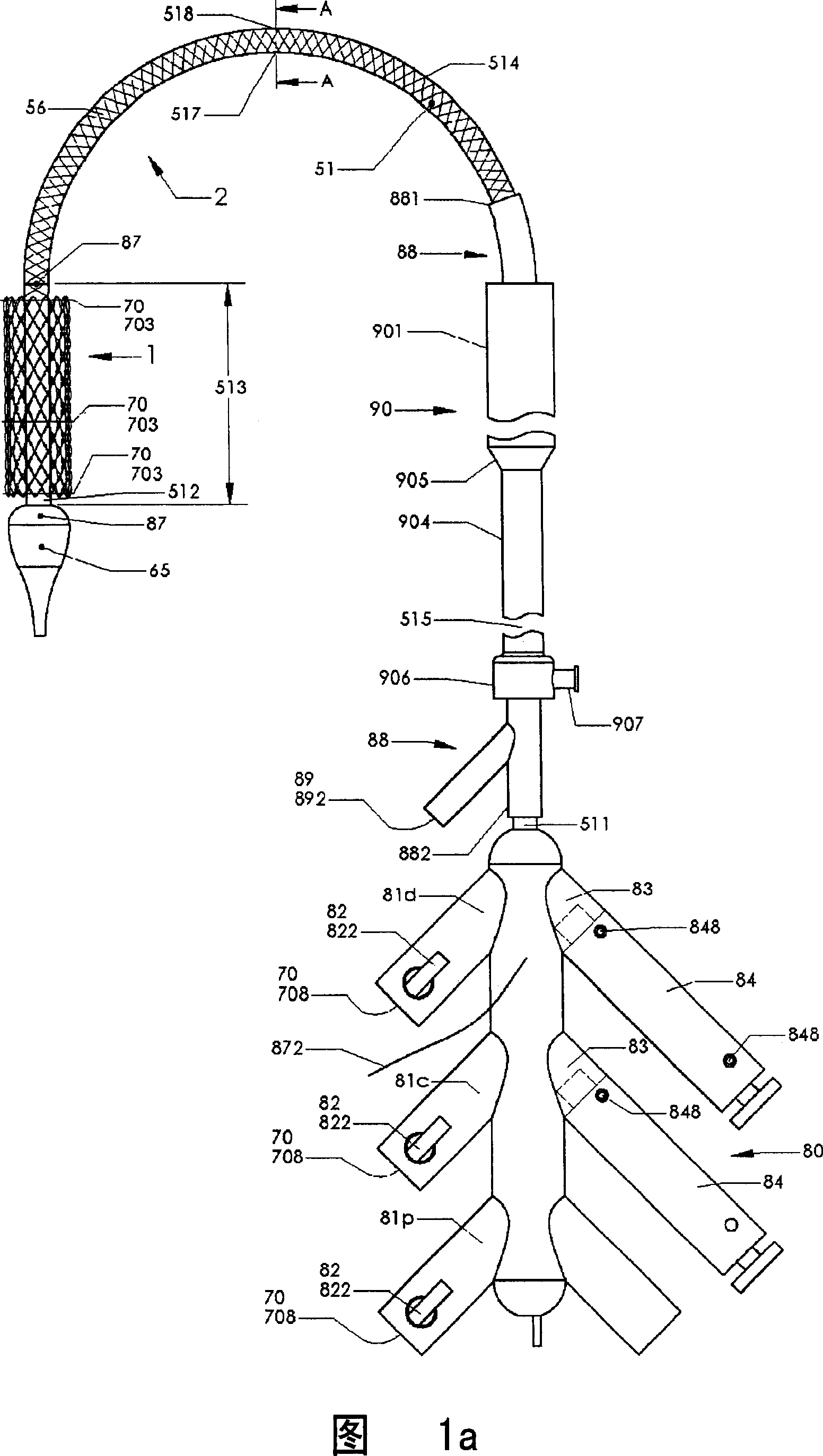

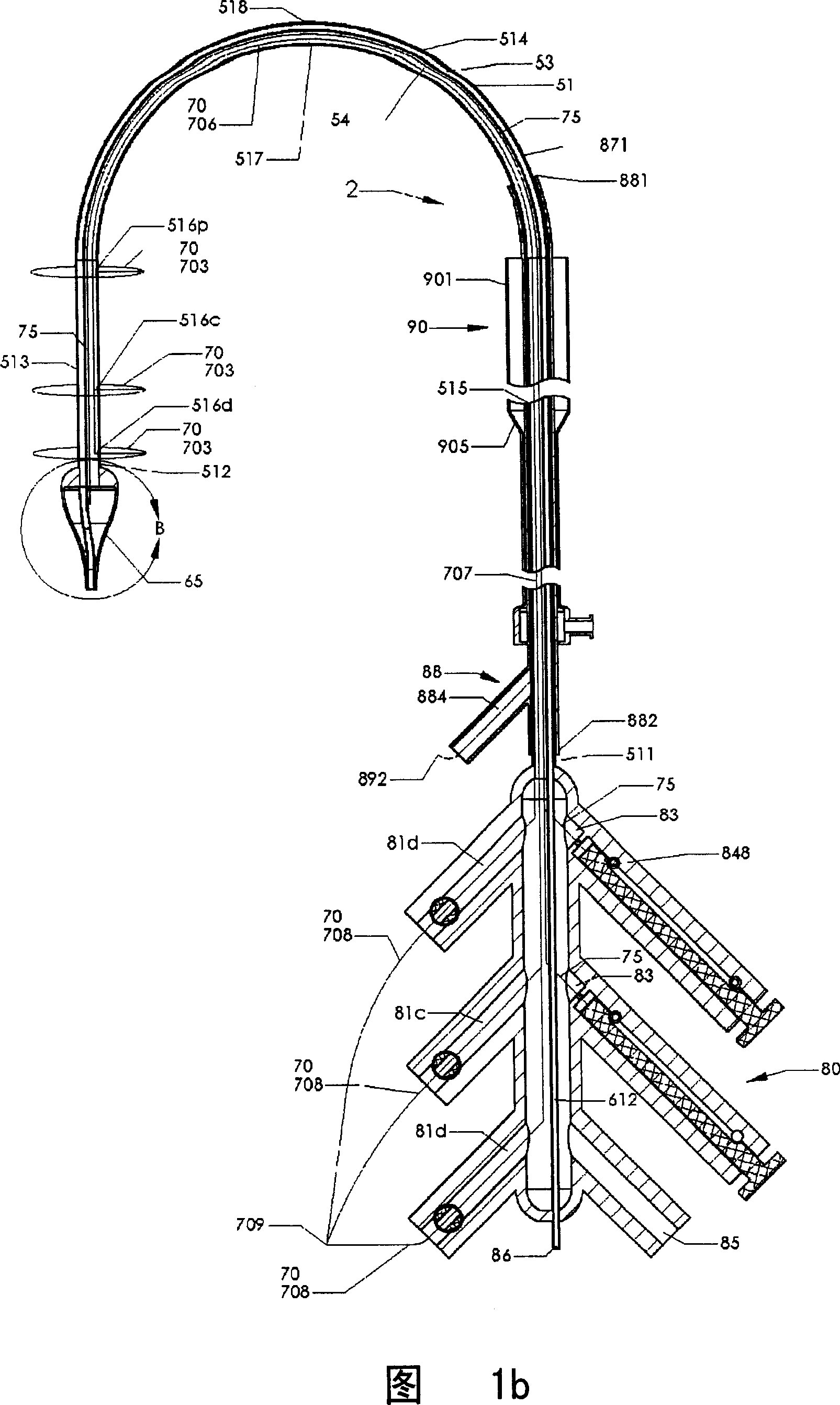

Apparatus for delivering artificial heart stent valve

The invention relates to a transmitter of artificial heart support valve, which comprises duct head, tube, near controller, middle tube, guide tube, external protector, at least one locking wire, and at least one support drawing line. The external protector can be external pin tube, or breakable external protector or the line compressor which can be twisted. The invention can rotationally position the valve, and effectively fix the expanded valve, reduce the abrasion, and avoid fall off.

Owner:BEIJING BALANCE MEDICAL

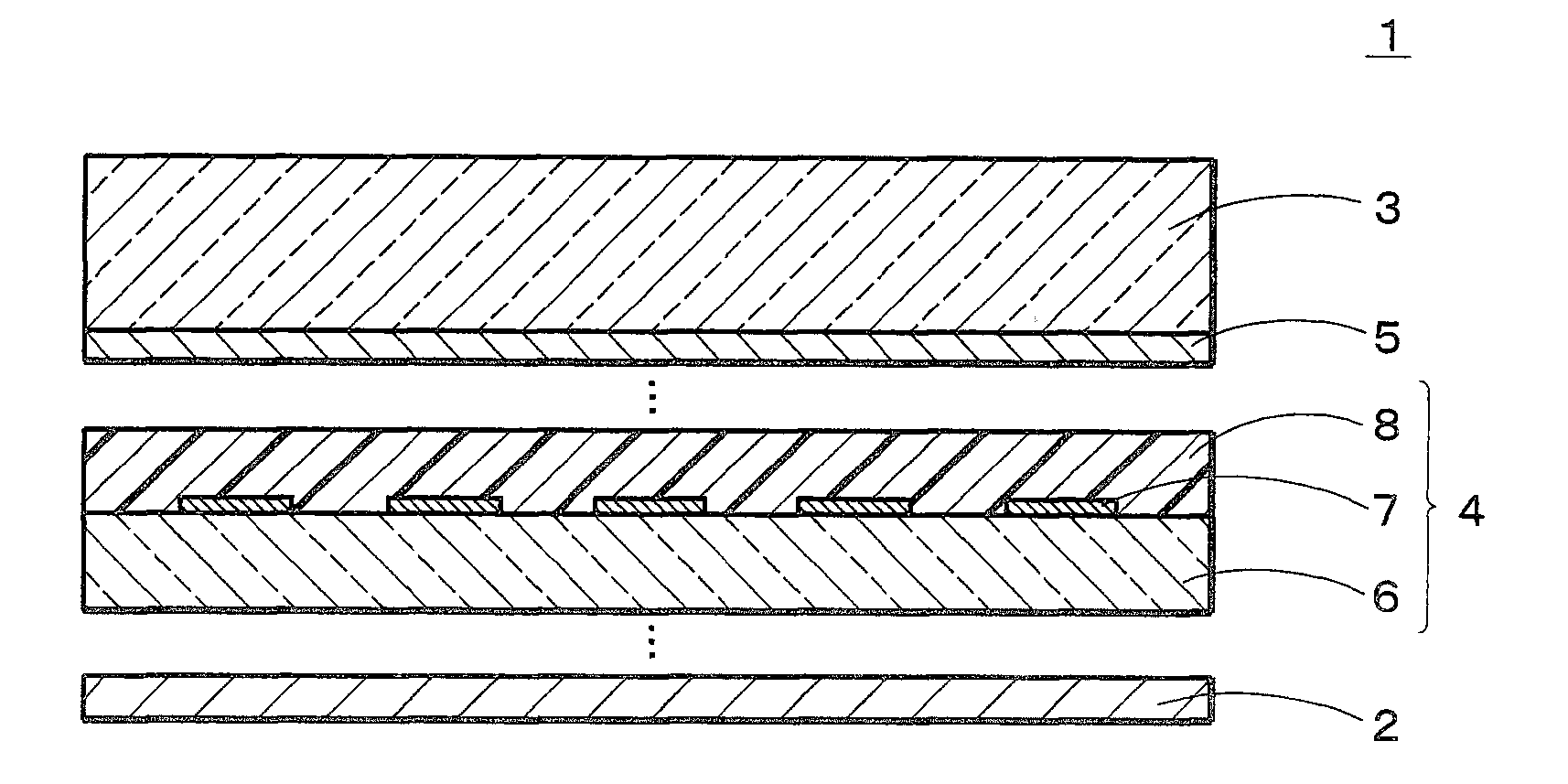

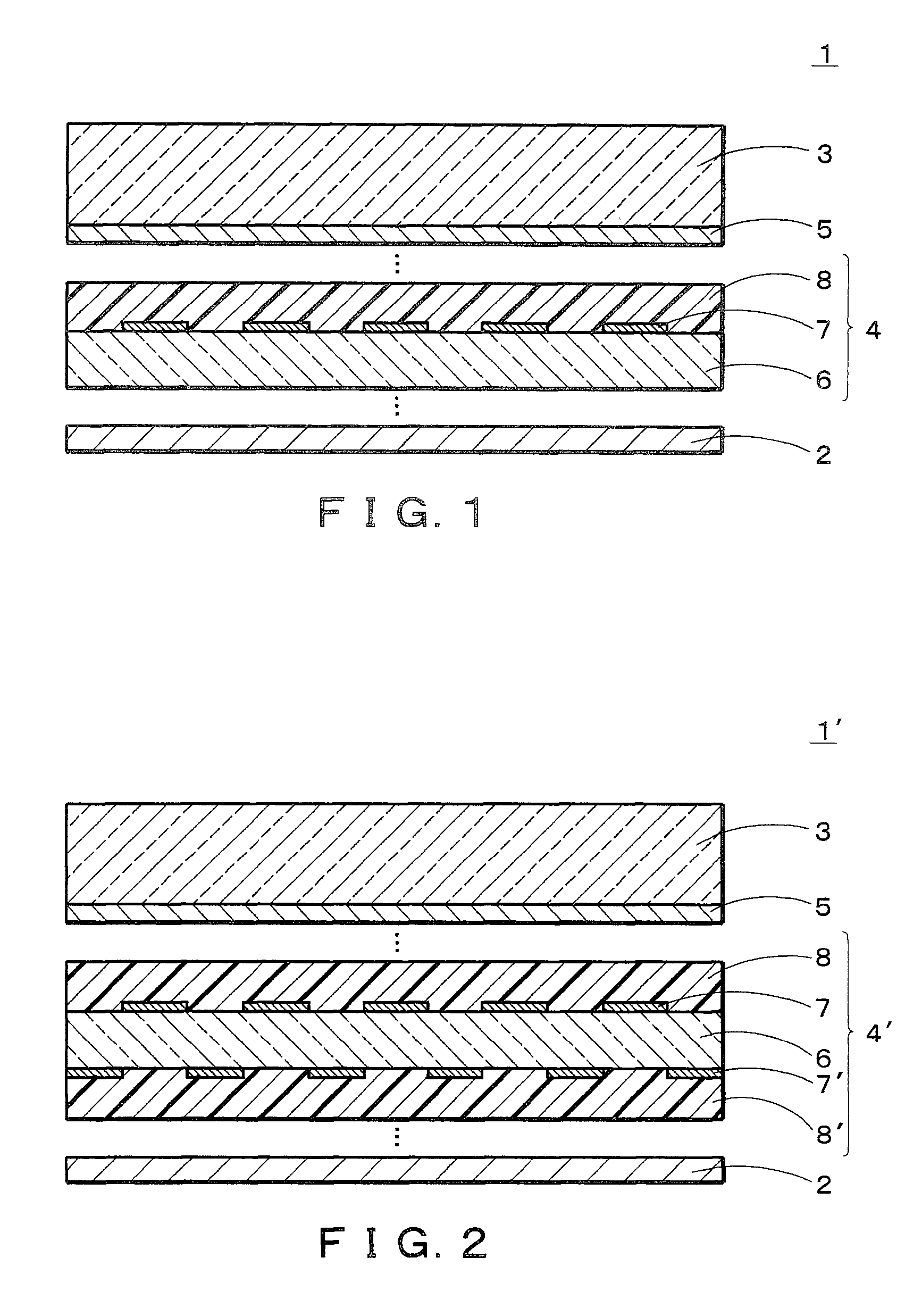

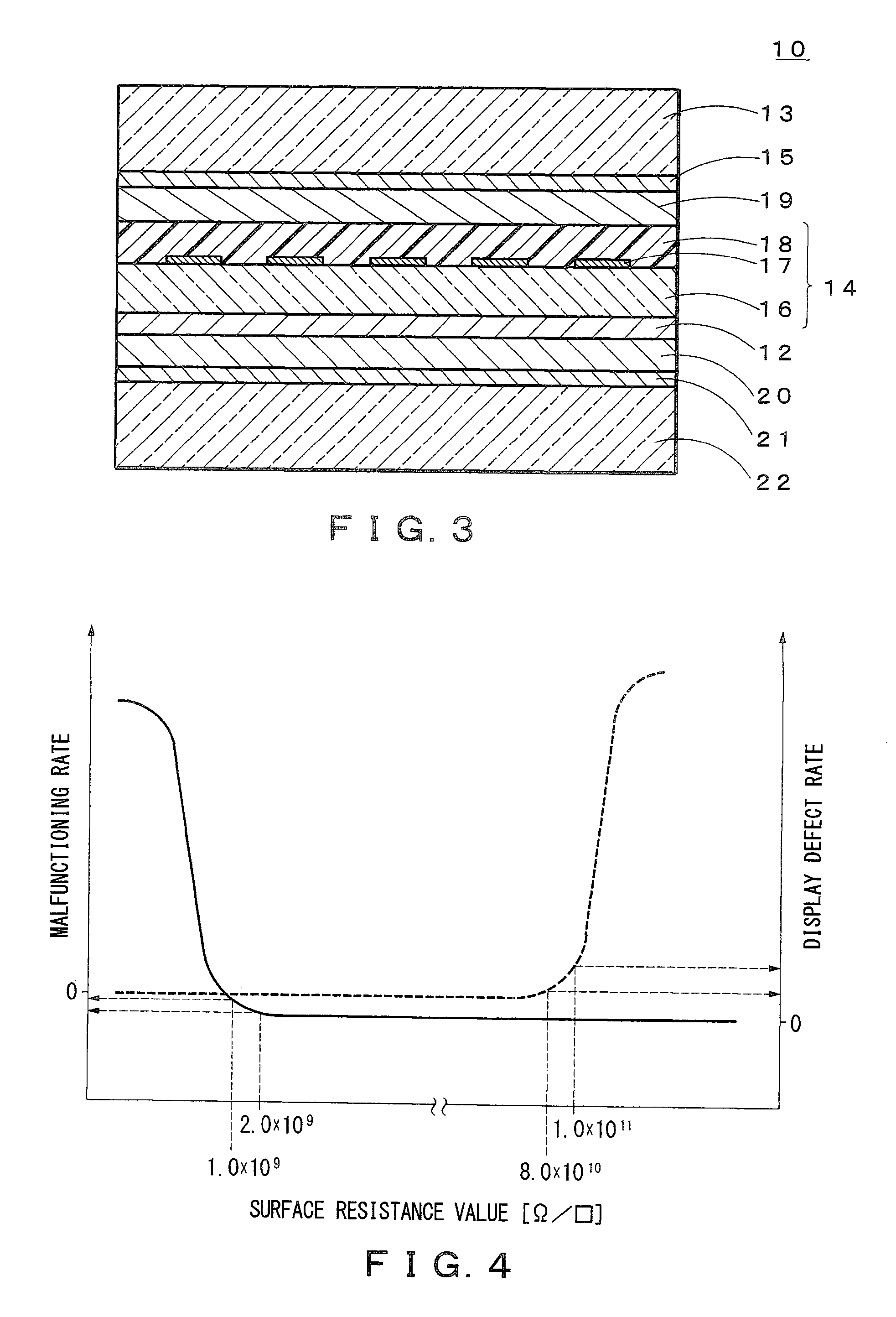

Input display device

ActiveUS20130120314A1Reduce generationAccurate inductionNon-linear opticsInput/output processes for data processingAntistatic agentDisplay device

An input display device includes a liquid crystal layer containing liquid crystal molecules that are homogeneously aligned in an absence of an electric field, a first polarizer disposed on a viewing side of the liquid crystal layer, a capacitive sensor disposed between the first polarizer and the liquid crystal layer, and an antistatic layer disposed between the first polarizer and the capacitive sensor, the antistatic layer being attached to the first polarizer. The capacitive sensor has a transparent substrate, a transparent electrode pattern formed on the transparent substrate, and a first adhesive layer formed on the transparent substrate to embed the transparent electrode pattern, and the antistatic layer has a surface resistance value of 1.0×109 to 1.0×1011Ω / □.

Owner:NITTO DENKO CORP

Prevention of dislocation of an IOL

An intraocular lens assembly operable to be positioned in a capsular bag, the IOL assembly including a lens, a haptic connected to the lens by connecting structure, and an anti-dislocation element extending from at least one of the lens, haptic and connecting structure, the anti-dislocation element being operable, when positioned in the capsular bag and upon application of a dislocating force, to become wedged and inhibit dislocation of the lens from the capsular bag. The anti-dislocation element may be generally coplanar with the lens or tilted with respect to a plane of the lens.

Owner:ABBOTT MEDICAL OPTICS INC

Complete locating device for total hip arthroplsty

PendingCN107149490AReduce the chance and degree of loosening or saggingGuaranteed stabilitySurgical sawsBone drill guidesMedullary cavityCalcar

The invention discloses a complete set of positioning device for artificial total hip joint replacement, which belongs to the field of medical equipment. The positioning device is conducive to the accurate osteotomy of the femoral neck with the oscillating saw, the accurate positioning of the use direction of the acetabular file, the square head bone knife, and the medullary cavity file, and the insertion of the femoral prosthesis into the femoral marrow at the original position and original angle. The cavity is beneficial to preserve the femoral calcar and the length of the femoral neck, which is conducive to the correct placement of the acetabular cup, shortens the operation time, reduces intraoperative bleeding, improves the success rate of the operation, relieves joint pain, corrects deformity, restores and improves joint movement Function.

Owner:汤向阳

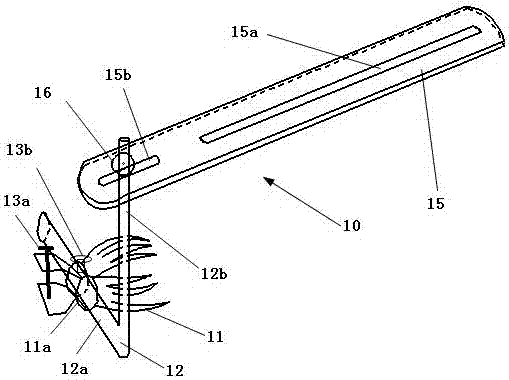

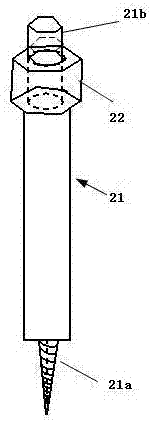

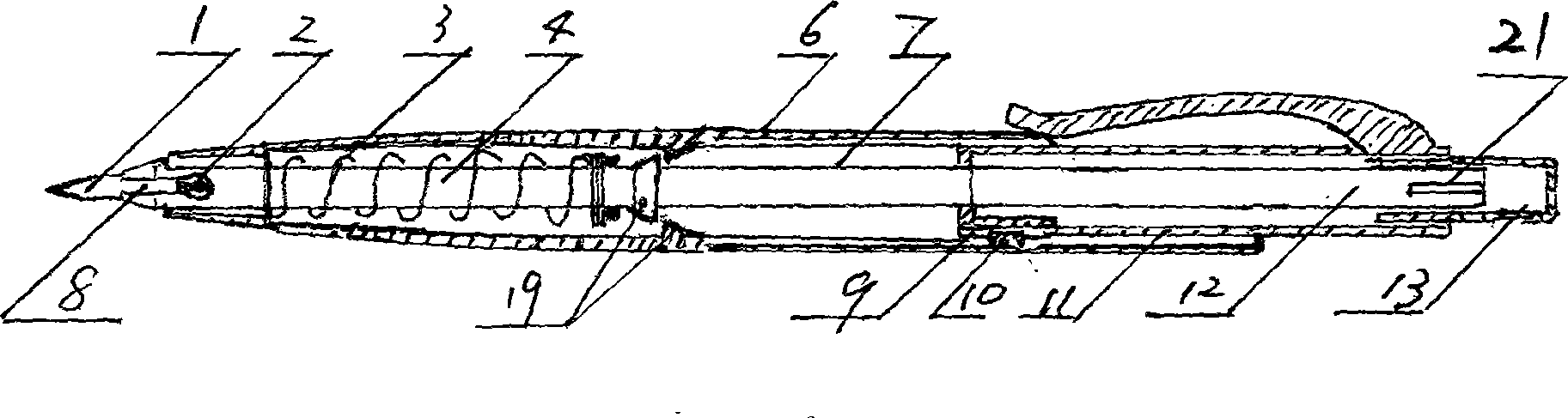

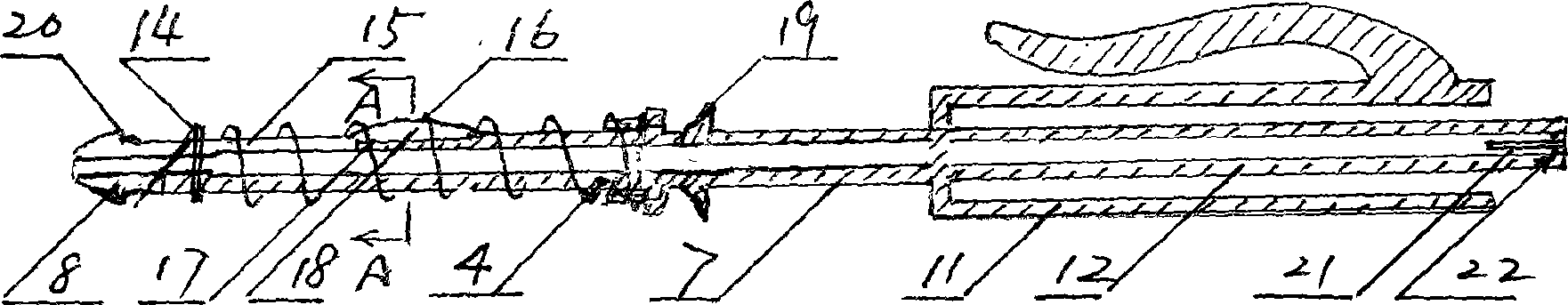

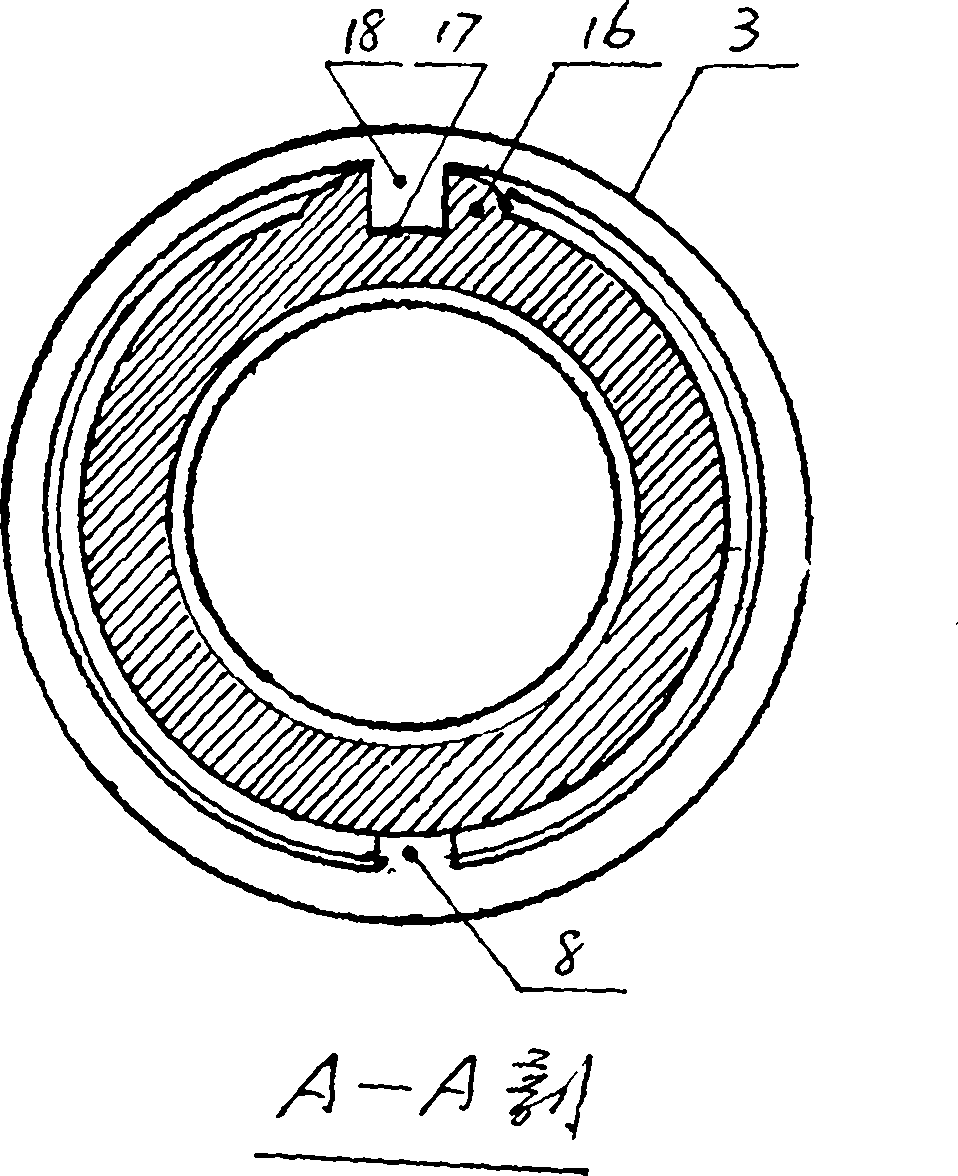

Lead replaceable pencil with bullet pencil lead

ActiveCN101670729BMake sure not to overlapPrevent dislocationPropelling pencilsEngineeringStorage tube

The invention discloses a lead replaceable pencil with bullet pencil lead. A penholder of the lead replaceable pencil is provided with a lead storage tube inside. A spring with a tongue is sleeved outside a front end of the lead storage tube. The lead storage tube is provided with a long slot. A rear end of the long slot is provided with a step. The side opposite to the long slot is provided witha short slot. A front part of the lead storage tube is a single-layer tube, and a rear part of the lead storage tube is a double-layer tube. A buninoid bulge is arranged above the step at the rear end of the long slot. An inner cavity of the penholder and an outer tube of the lead storage tube cannot be relatively rotatably matched so as to prevent the spring tongue from dislocating from the longslot. A rear end of the short slot is provided with a large hole, so that the spring tongue enters the large hole to prevent the pencil lead from retracting. A non-skid limit part is arranged betweenthe lead storage tube and the penholder. Therefore, both the appearance and the performance of the lead replaceable pencil can be accepted by users and the lead replaceable pencil really becomes a substitute product for a wooden pencil.

Owner:YANCHENG LUCKLY STATIONERY CO LTD

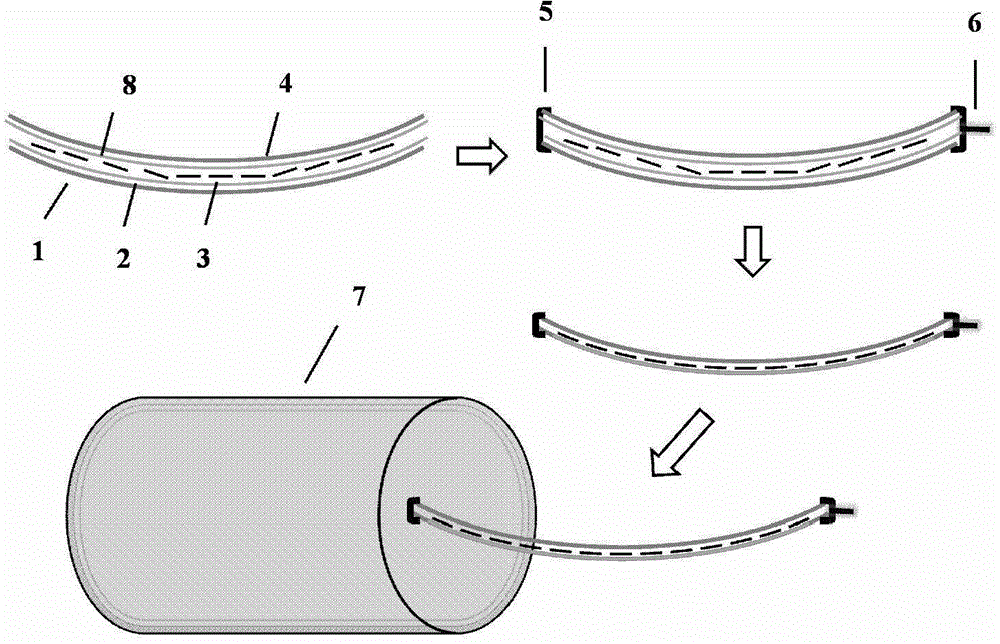

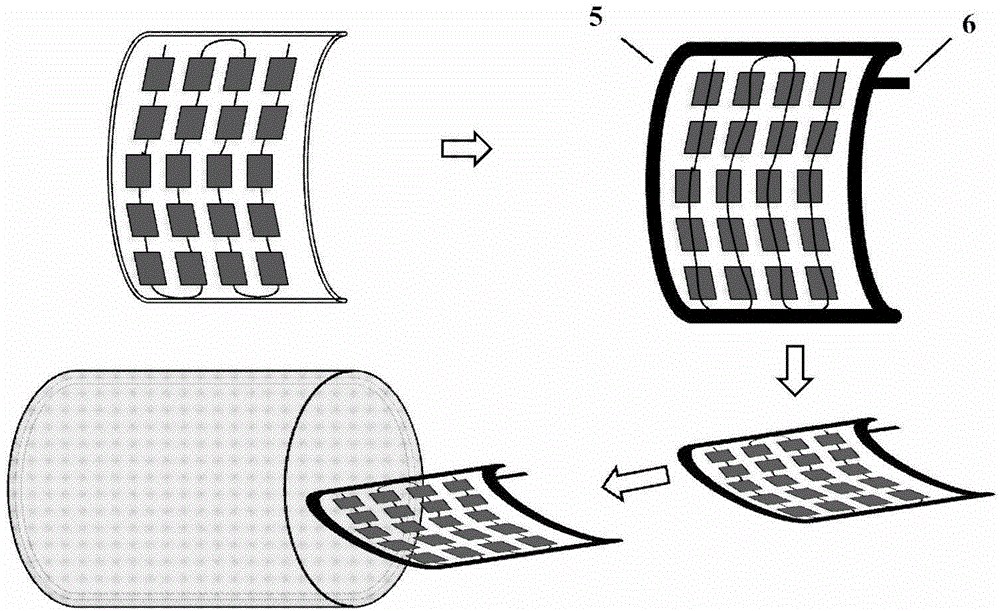

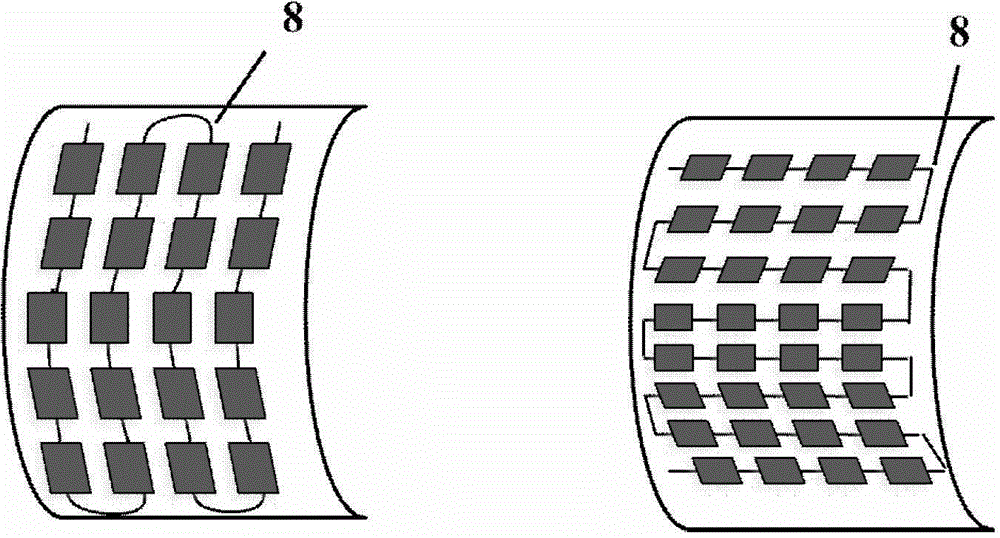

Lamination preparation process of curved-surface double-glass photovoltaic module

InactiveCN102983213AAchieve initial shapePrevent slidingFinal product manufactureLaminationRubber ringGlass cover

The invention discloses a lamination preparation process of a curved-surface double-glass photovoltaic module. Firstly, a layer of binding material covers face plate bent glass, a solar cell is arranged on the binding material, a layer of binding material covers the solar cell, and then rear plate bent glass covers on the binding material. After the panel bent glass is aligned to the rear plate bent glass, a vacuum rubber ring is sleeved on the periphery of the face plate bent glass and the rear plate bent glass, the solar cell and the two layers of binding materials are enabled to be in a closed space formed by the face plate bent glass, the rear plate bent glass and the vacuum rubber ring, the closed space is vacuumized then, the face plate bent glass and the rear plate bent glass compact the solar cell and the binding materials arranged between the face plate bent glass and the rear plate bent glass to prevent relative sliding, and an assembly to be packaged is obtained. The assembly to be packaged is placed into a high-pressure autoclave laminating machine to be carried out with lamination, and the vacuum rubber ring is removed and the curved-surface double-glass photovoltaic module is obtained after the lamination. The lamination preparation process of the curved-surface double-glass photovoltaic module can utilize one device to prepare photovoltaic modules with different radiuses of curvature.

Owner:CHINA SUNERGY CO LTD

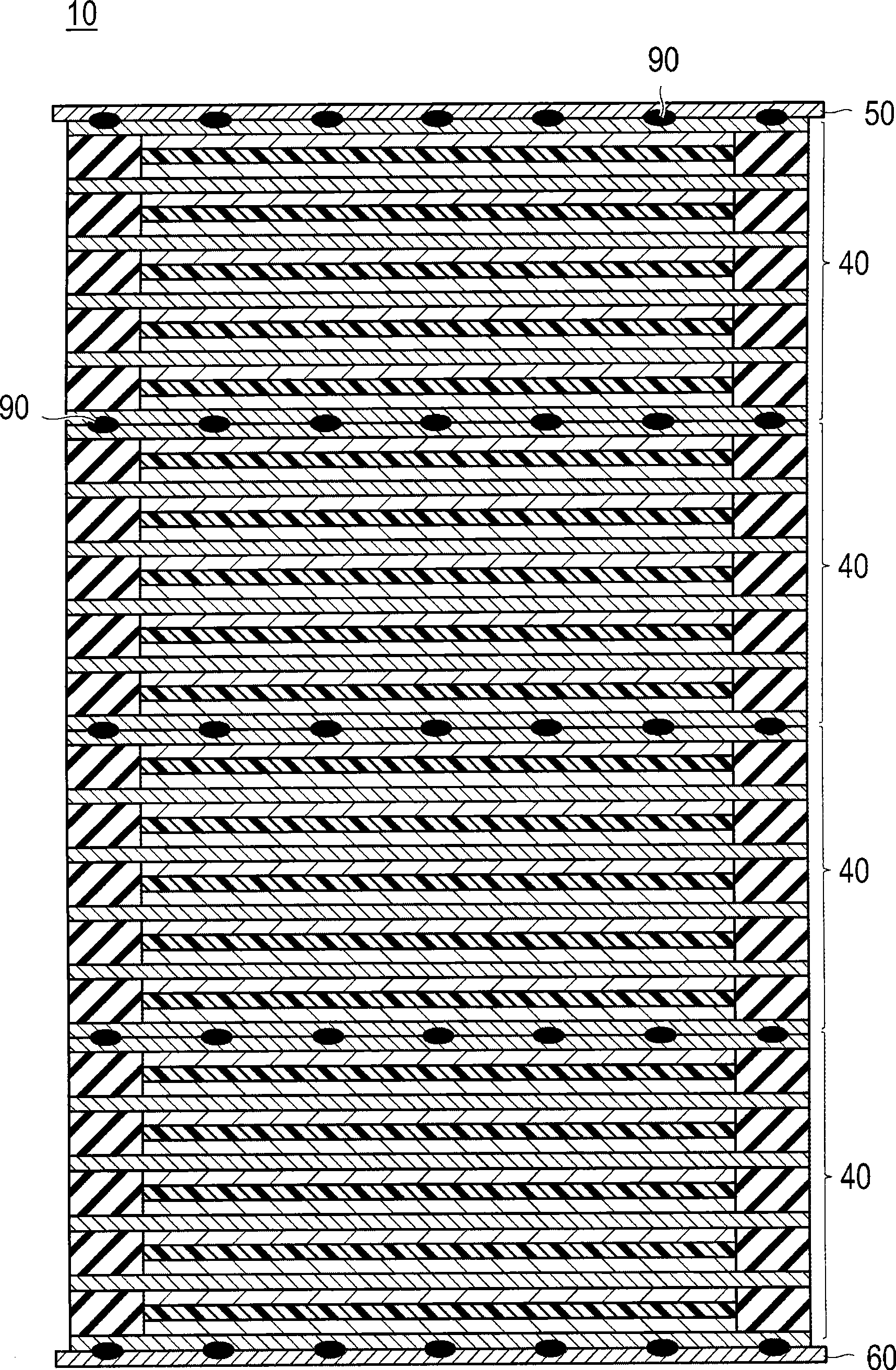

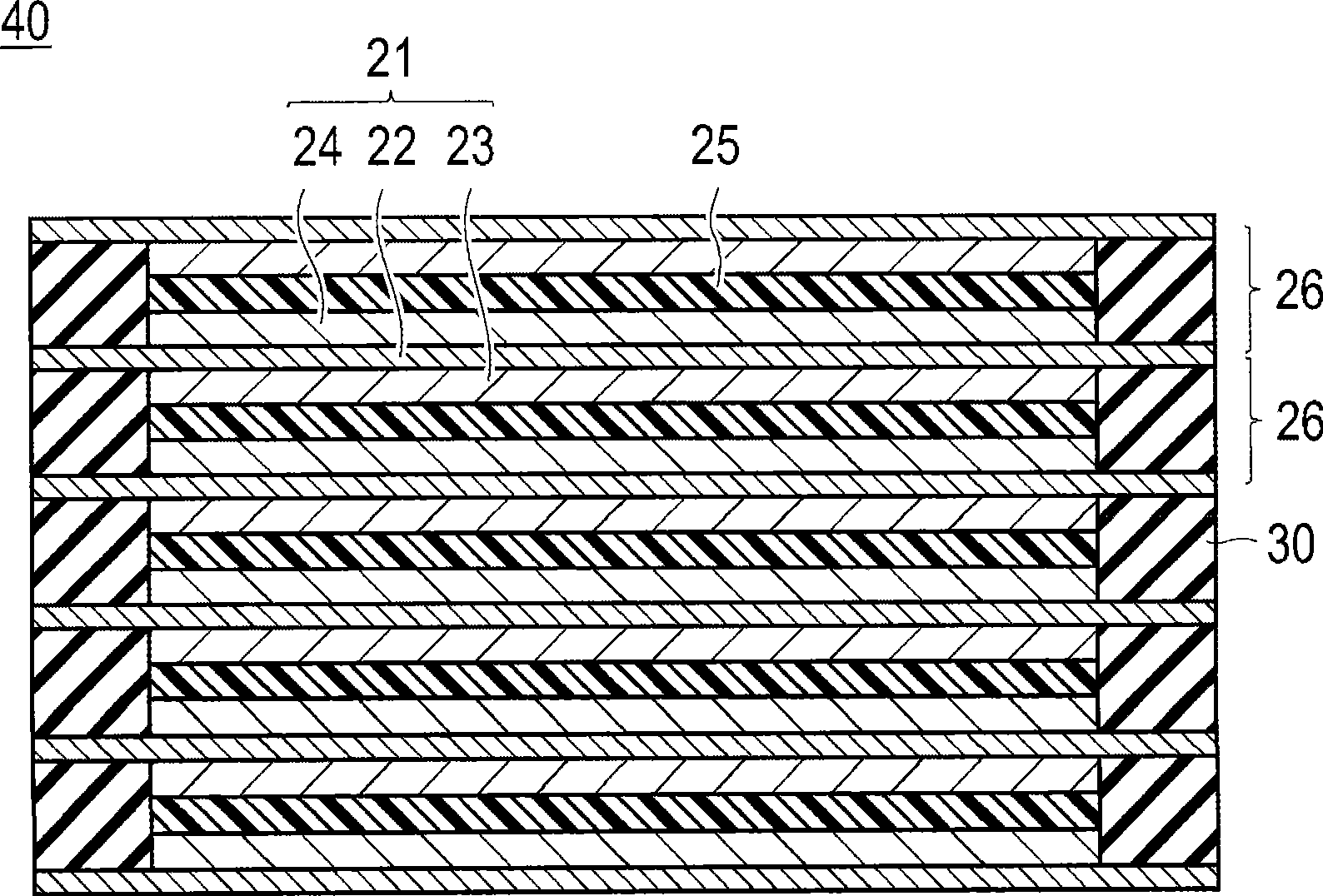

Bipolar secondary battery, battery asembly formed by connecting said batteries and vehicle mounting same

ActiveCN101425600APrevent dislocationLower resistanceFinal product manufactureActive material electrodesEngineeringBattery pack

Embodiments of a battery taught herein are directed to preventing a displacement between bipolar battery stacks or between a bipolar battery stack and an electrode tab. A bonding portion is formed at a part of a contact surface where a collector positioned at both ends in a stacking direction of a bipolar battery stack is bonded to the electrode tabs. The electrode tab and the collector are fixedby such a bonding portion. Further, the bonding portion is formed at a part of a contact surface where adjacent bipolar battery stacks are bonded to each other. Bipolar batteries positioned at upper and lower portions in the stacking direction are fixed by such a bonding portion.

Owner:NISSAN MOTOR CO LTD

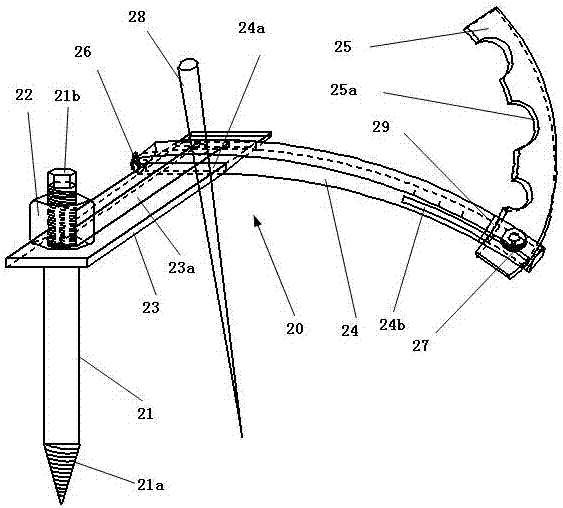

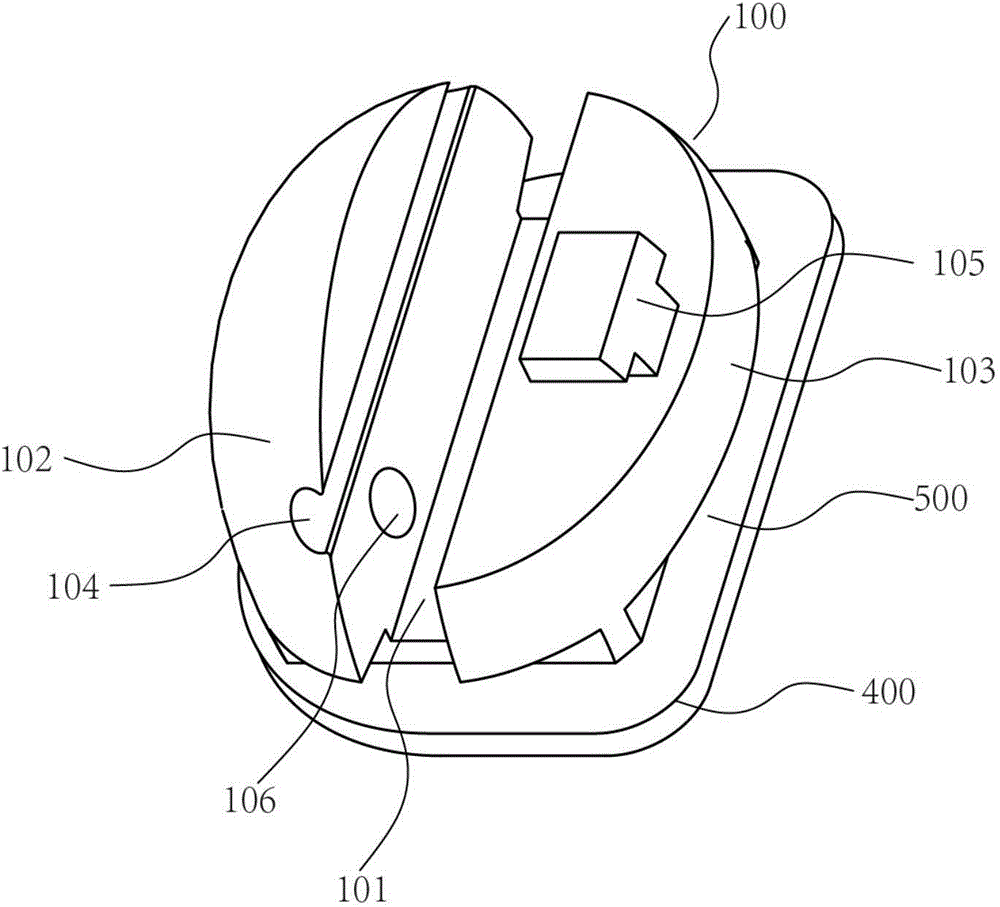

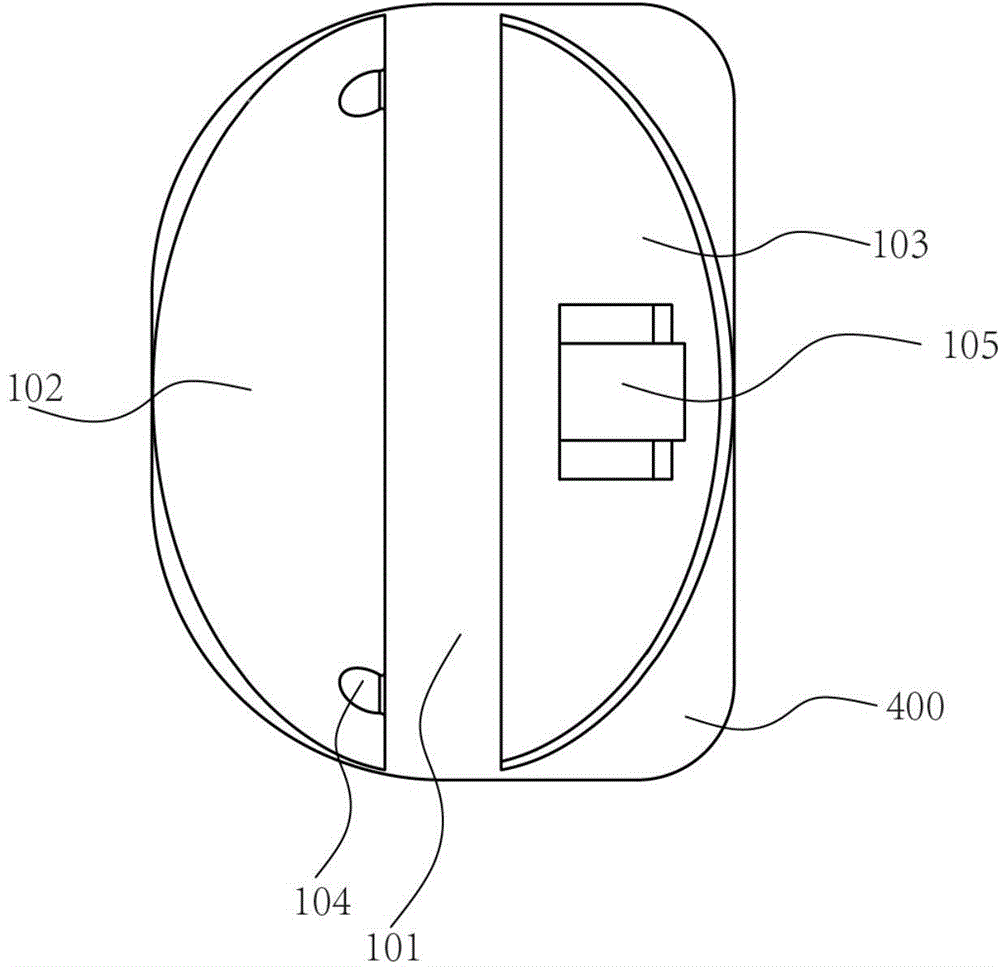

Traction bracket, orthodontic system, and orthodontic method thereof

ActiveCN105982745AAchieve regulationIncrease or decrease in lengthArch wiresBracketsArch wiresEngineering

The invention discloses a traction bracket, an orthodontic system, and an orthodontic method thereof. The traction bracket includes a traction part, a main part, a cover part and a connection part. A main trough is formed in the main part. A locking traction hole is formed in the main part. One end of the locking traction hole is opened on surface of the main part to form a cylindrical traction part inlet while the other end is opened in the main trough in the main part to form a locking hole. The traction part is matched with and connected to the locking traction hole. The main part is connected to the cover part through the connection part. The bottom surface of the cover part is matched with the surface of the main part and covers the main trough. The surface of the cover part is matched with the surface of the main part to form a smooth curve surface. The traction part in the traction bracket is convenient to mount. The traction part not only helps the traction bracket to slide but also completes locking of the bracket and an arch wire after change of a traction bolt (a locking bolt) so as to achieve corresponding orthodontic effects.

Owner:吉利

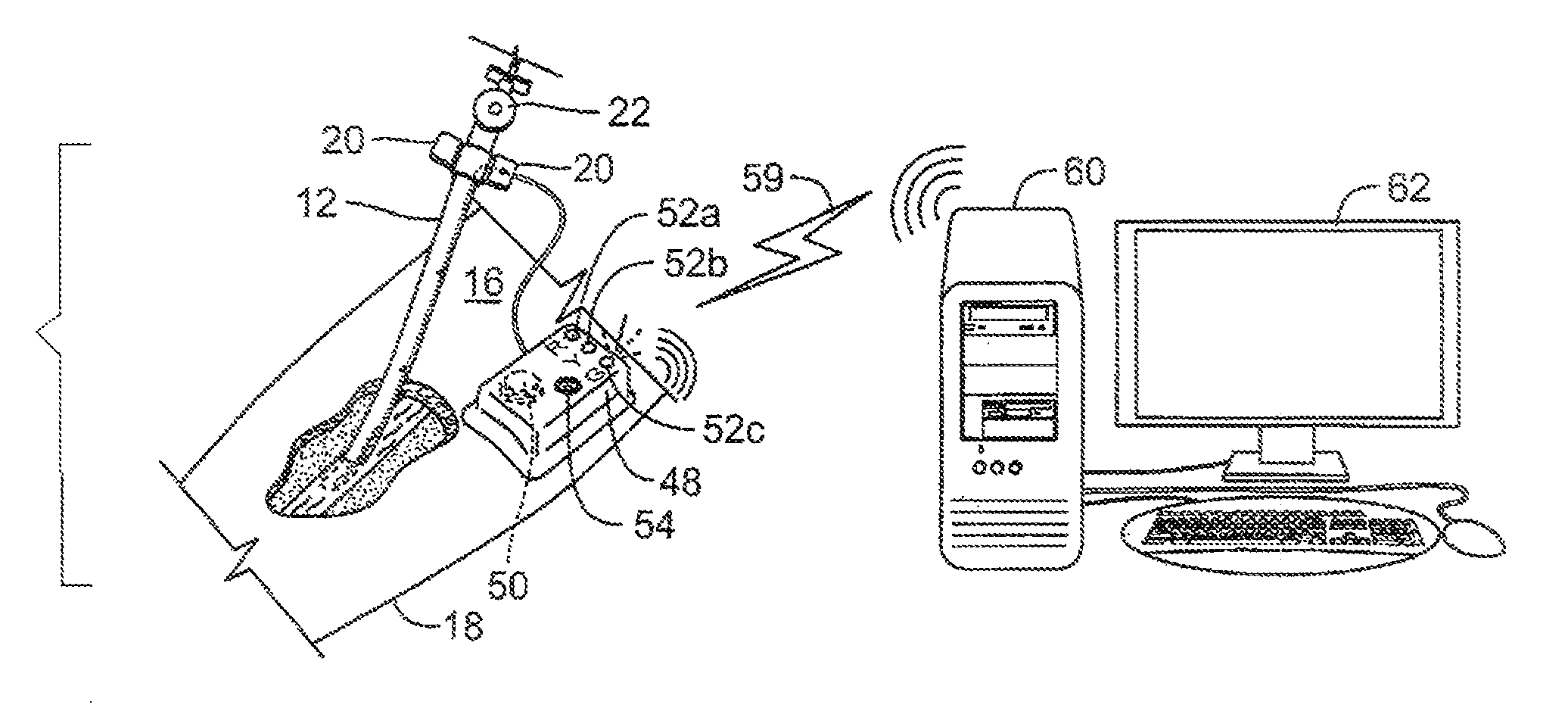

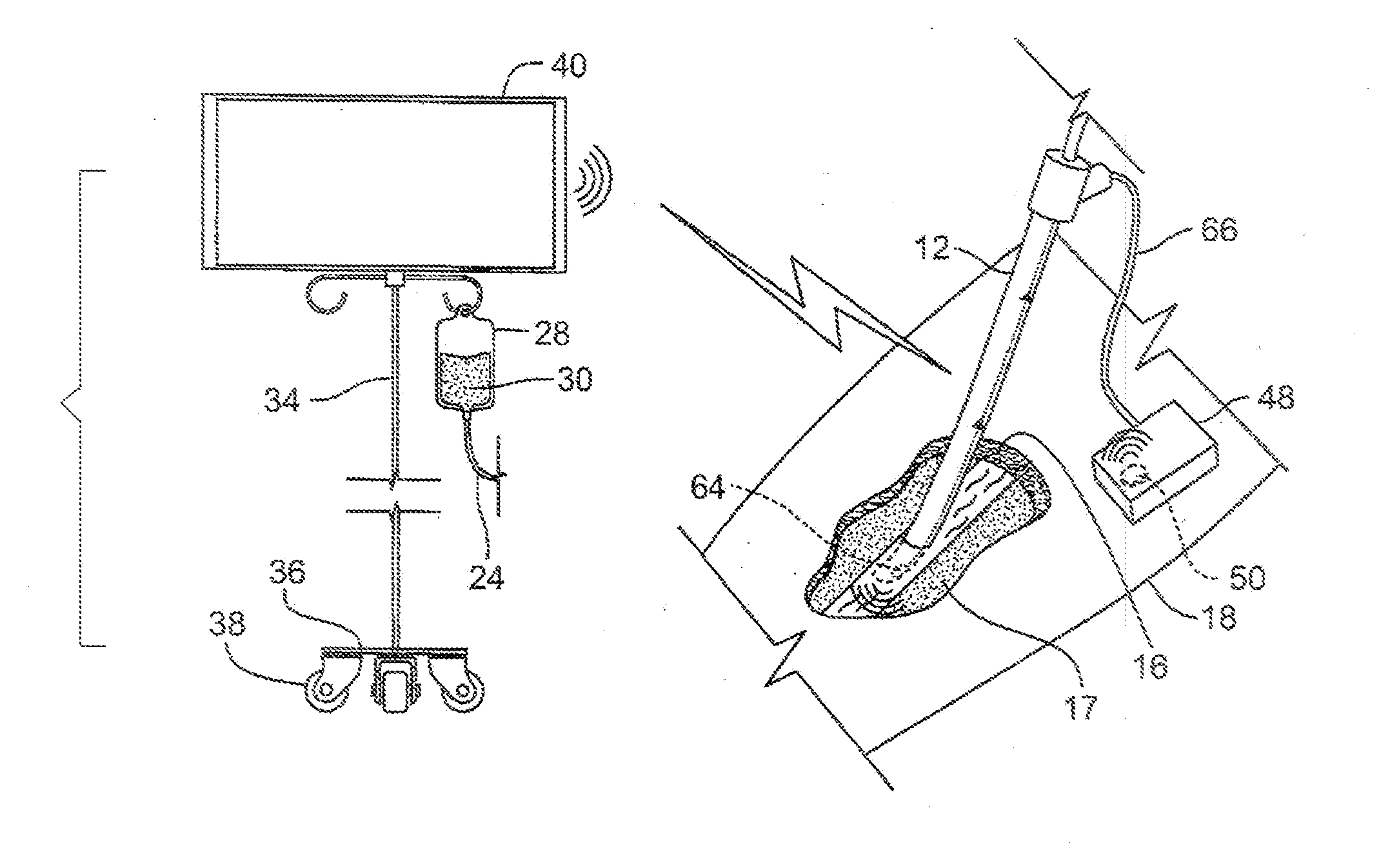

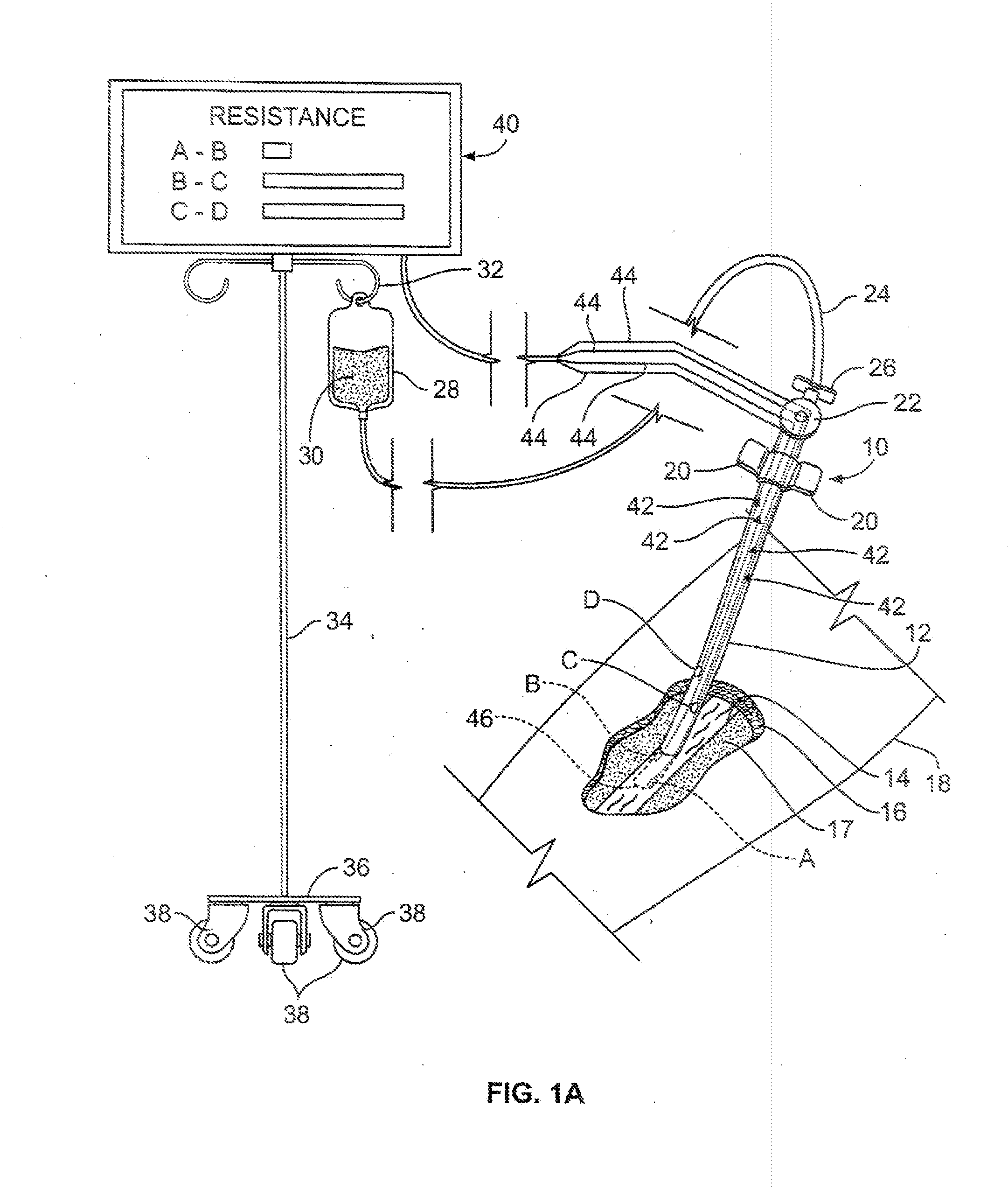

Apparatus and method for monitoring catheter insertion

InactiveUS8700133B2Avoid damagePrevent dislocationUltrasonic/sonic/infrasonic diagnosticsMedical devicesVeinCannula tip

A method and apparatus for inserting and monitoring the placement of a cannula tip within a peripheral vein of a human body where the cannula includes a sensor located at predetermined location and mounted on the cannula for sensing the biological material of the body to guide the insertion of the cannula tip into the vein and alerts to the withdrawal of the cannula tip from the vein in the body.

Owner:SMART IV

Intravenous apparatus and method

InactiveUS20130338480A1Avoid damagePrevent dislocationMedical devicesDiagnostic recording/measuringVeinCannula tip

A method and apparatus for inserting and monitoring the placement of a cannula tip within a peripheral vein of a human body where the cannula includes a sensor located at predetermined location and mounted on the cannula for sensing the biological material of the body to guide the insertion of the cannula tip into the vein and alerts to the withdrawal of the cannula tip from the vein in the body.

Owner:SMART IV

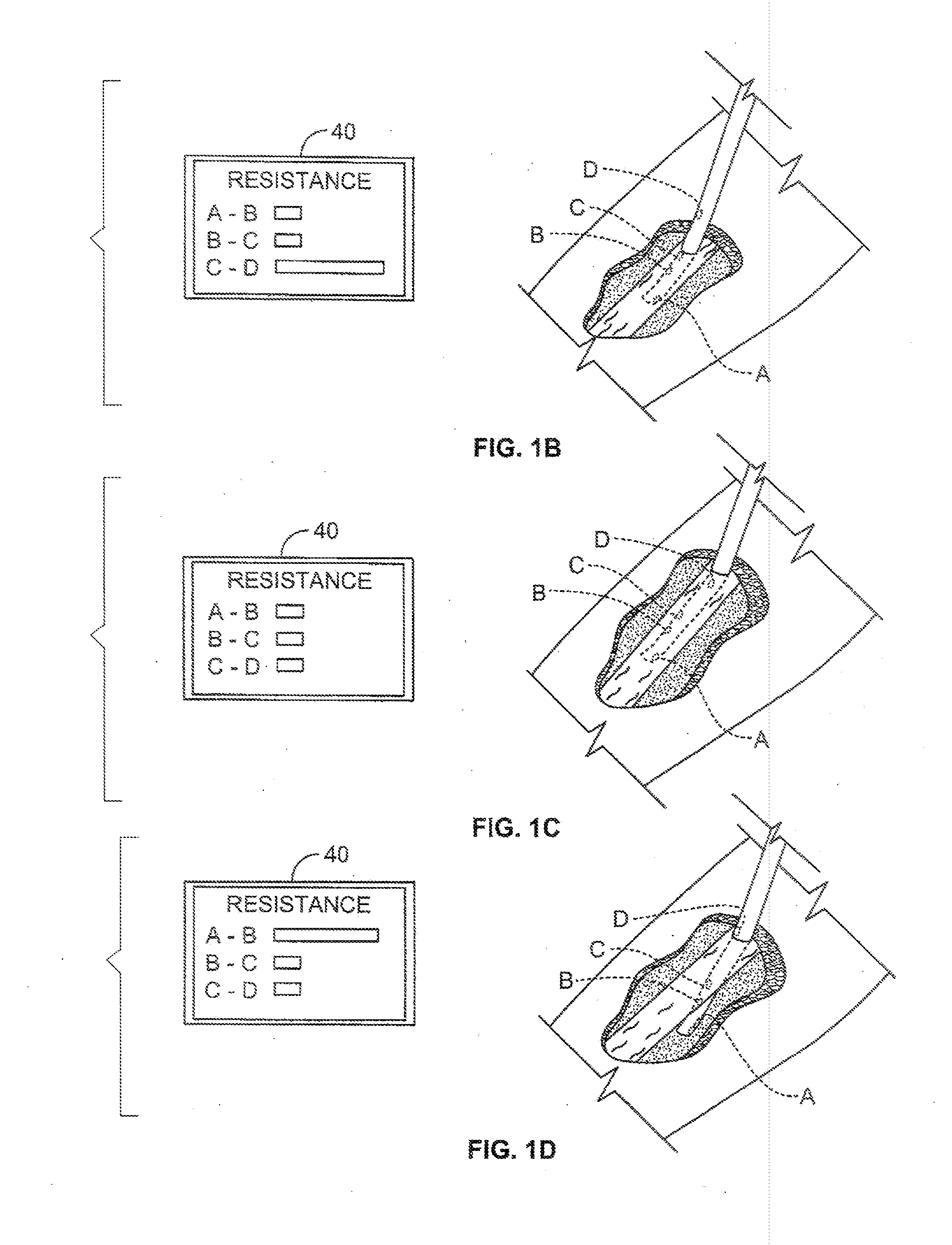

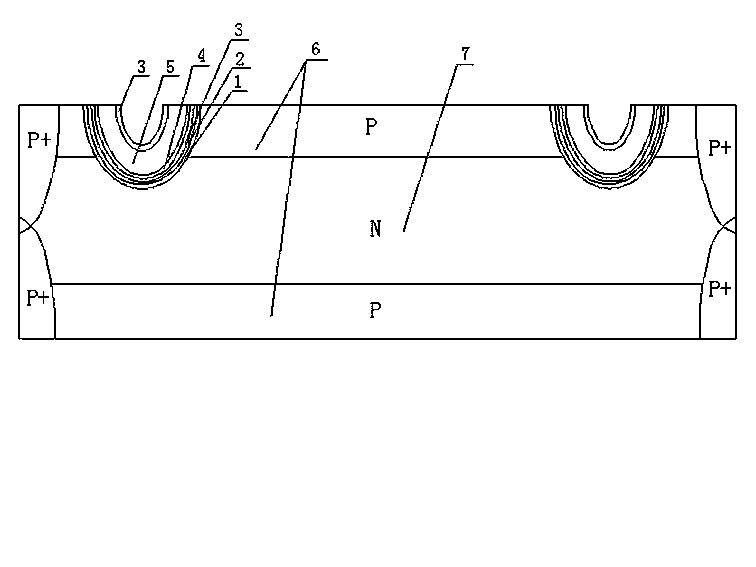

Multilayer composite membrane passivation structure of table top high-power semiconductor device and manufacturing technology of multilayer composite membrane passivation structure of table top high-power semiconductor device

ActiveCN103730430ARepair damageImprove breakdown voltagePolycrystalline material growthSemiconductor/solid-state device detailsManufacturing technologyPolycrystalline silicon

The invention discloses a multilayer composite membrane passivation structure of a table top high-power semiconductor device. The multilayer composite membrane passivation structure comprises P-type boron junction areas and an N-type phosphorus junction area, the upper end and the lower end of the N-type phosphorus junction area are provided with the P-type phosphorus areas respectively, and an alpha-polycrystalline silicon layer, a semi-insulating polycrystalline silicon thin membrane, a low-temperature heat oxidation layer, a high-temperature Si3N4 thin membrane, a negative charge glass passivation layer and a low-temperature heat oxidation layer are sequentially arranged on the surface of a PN junction of a table top of the table top high-power semiconductor device from inside to outside. A manufacturing technology of the multilayer composite membrane passivation structure of the table top high-power semiconductor device includes the following steps: a, depositing the alpha-polycrystalline silicon, b, depositing semi-insulating polycrystalline silicon, c, depositing the low-temperature heat oxidation layer, d, depositing Si3N4, e, conducting passivation on glass, and f, depositing the low-temperature heat oxidation layer in the outmost layer. The multilayer composite membrane passivation structure and the manufacturing technology have the advantages that the alpha-polycrystalline silicon layer is deposited, so that crystal lattice adaptation can be achieved, damage to crystal lattices of a silicon wafer in a groove can be repaired, leaked currents in the surfaces of junctions are reduced, and the stability and the reliability of the device at the high temperature are improved.

Owner:江苏吉莱微电子股份有限公司

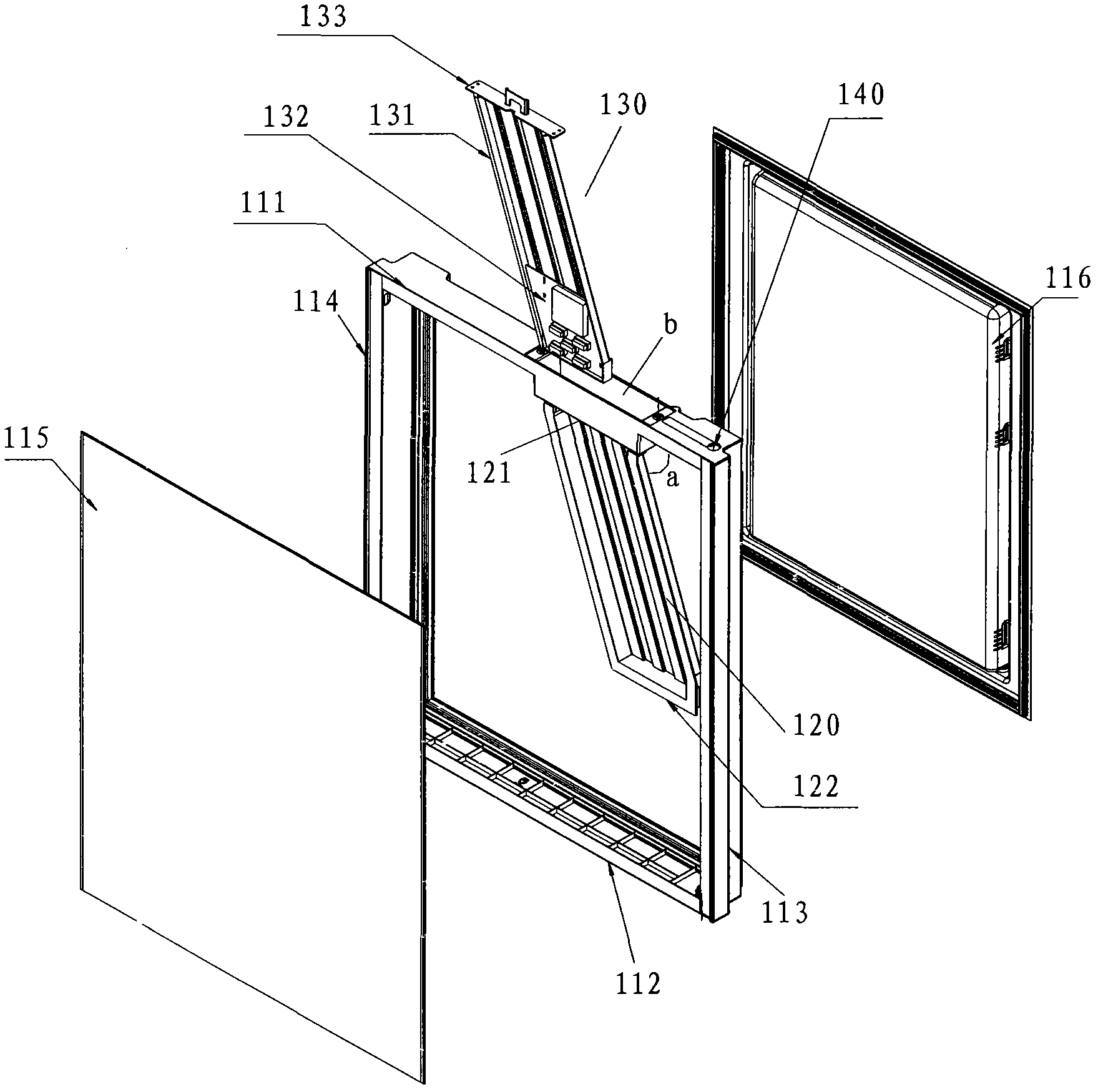

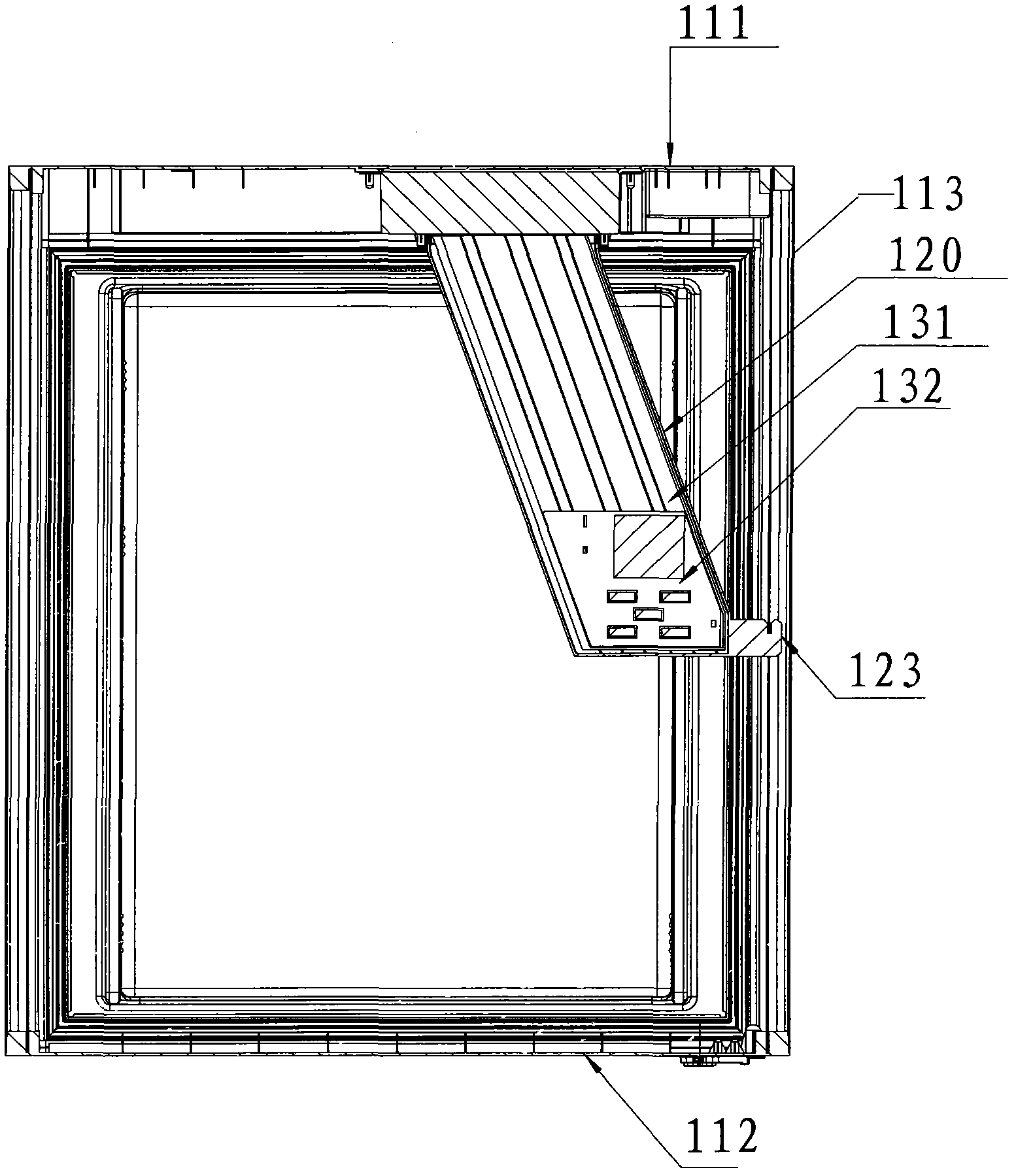

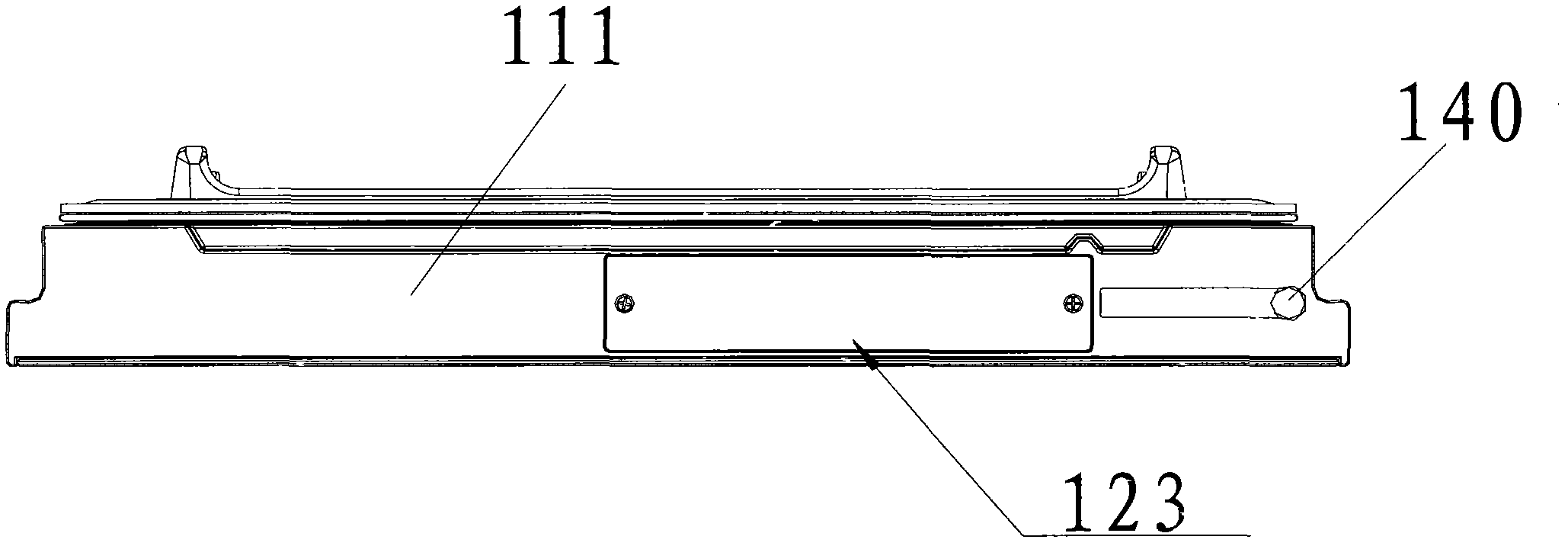

Door body for refrigerator and refrigerator with same

ActiveCN102278856AMeet different design requirementsDiversified choice spaceLighting and heating apparatusDomestic refrigeratorsEngineeringRefrigerated temperature

The invention provides a door body for a refrigerator and the refrigerator with the same. The door body comprises a body, a pre-buried box and a circuit board assembly, wherein the pre-buried box is arranged in the body in a direction which forms a preset angle with the vertical direction; the pre-buried box is communicated with the upper surface of the body so as to form a faucet with the upper surface; the lower end part of the pre-buried box is connected with the right surface of the body; the circuit board assembly is matched with the pre-buried box; and the circuit board assembly is inserted into the pre-buried box through the faucet. According to the door body, the position of the pre-buried box is more firm; and the circuit board assembly is displayed closer to one side of the doorbody, so that the display is more attractive; according to the refrigerator, the position of the display circuit board of the door body can be regulated as required through the position of the presetpre-buried box, so that the display position on the refrigerator is more flexible in design and the selection of a user is more diverse; in addition, the display position of the refrigerator is more fixed, so that dislocation between the display position and a transparent hollowed window of the door body is avoided.

Owner:HEFEI MIDEA REFRIGERATOR CO LTD +1

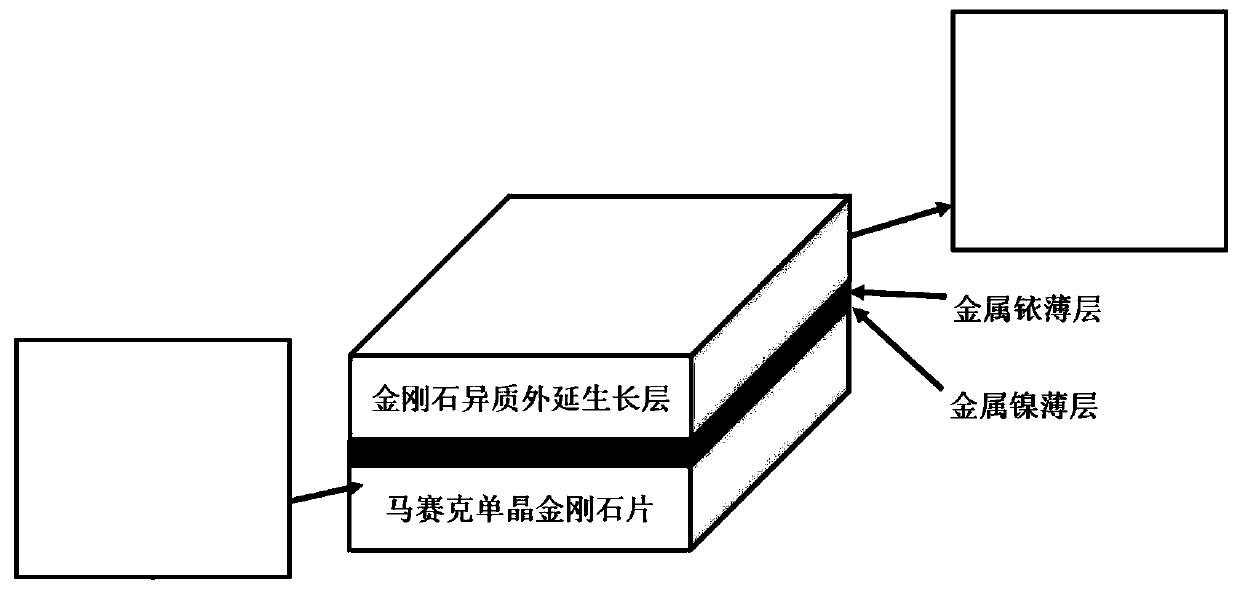

Method for epitaxial growth of high-quality and large-size monocrystalline diamond

ActiveCN111206280AImprove thermal conductivityLight in massPolycrystalline material growthFrom chemically reactive gasesIridiumCarbon layer

The invention discloses a method for epitaxial growth of high-quality and large-size monocrystal diamond, and belongs to the field of preparation of semiconductor materials. The method is characterized in that the surface roughness of a large-size single crystal diamond sheet grown through mosaic splicing is reduced to be lower than 0.2 nm through precision polishing; then electron beam evaporation is adopted to deposit metal nickel with the thickness of 100-200 nm on the surface of a substrate at the speed of 0.01-0.1 nm / s while the substrate is heated at the temperature of 100-500 DEG C, andthen metal iridium is deposited at the speed of 0.01-0.5 nm / s; after the thickness of iridium reaches 15-40 nm, the temperature of the heated substrate is increased to 700-1000 DEG C, meanwhile, thedeposition speed is increased to 0.5-1 nm / s, and finally, an iridium thin layer with the total thickness of 150-300 nm is deposited; then a plasma chemical vapor deposition technology is adopted to pre-deposit a 4-10 nm amorphous carbon layer after the iridium surface is cleaned by hydrogen plasma so as to promote the enrichment of carbon atoms on the sub-surface of the iridium thin layer; and finally, after the substrate is subjected to pure hydrogen plasma etching for 6-15 s, the negative bias voltage and the methane flux are regulated to achieve bias voltage in-situ nucleation of the large-size single crystal diamond on the iridium surface and subsequent non-bias voltage epitaxial growth.

Owner:UNIV OF SCI & TECH BEIJING

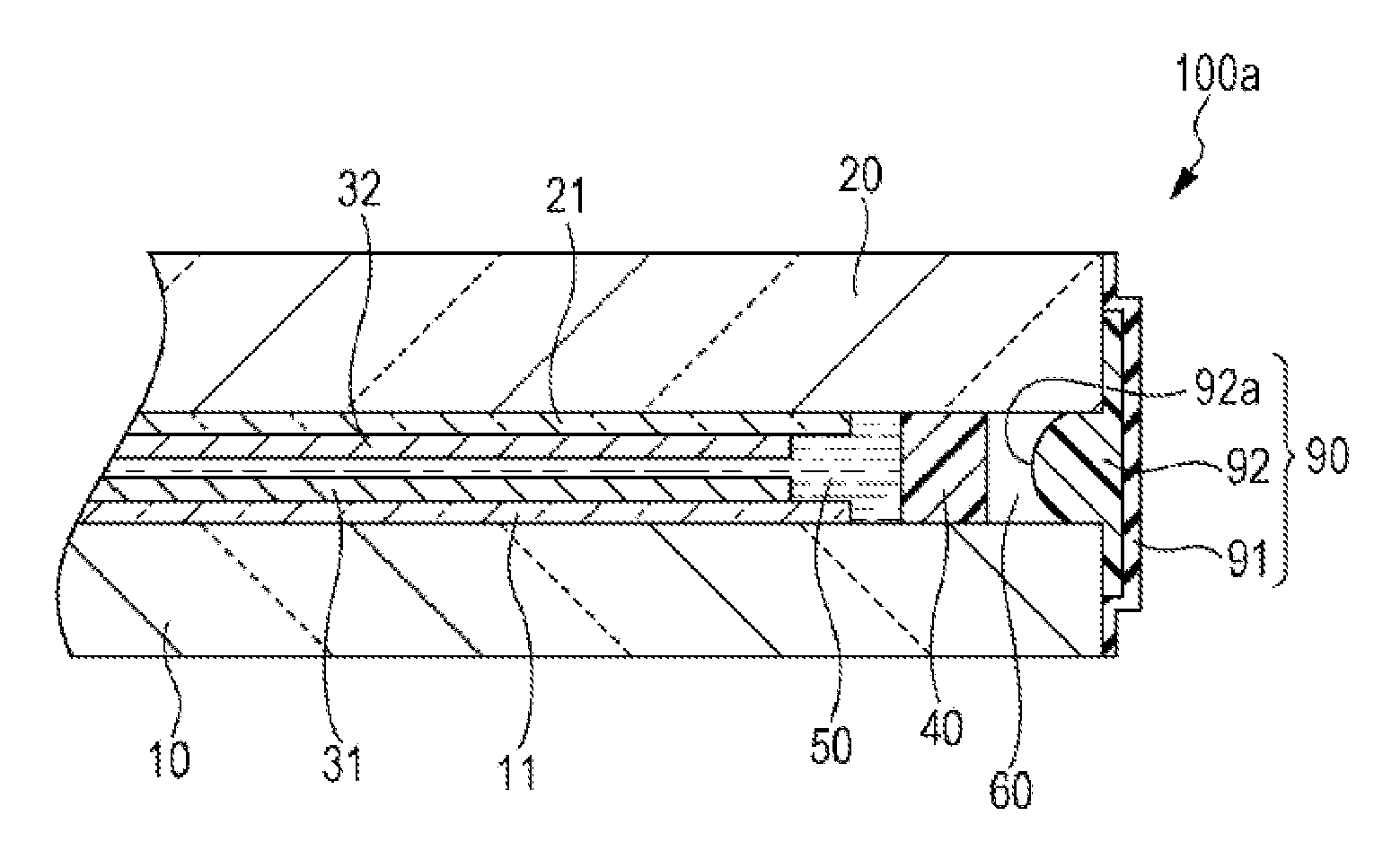

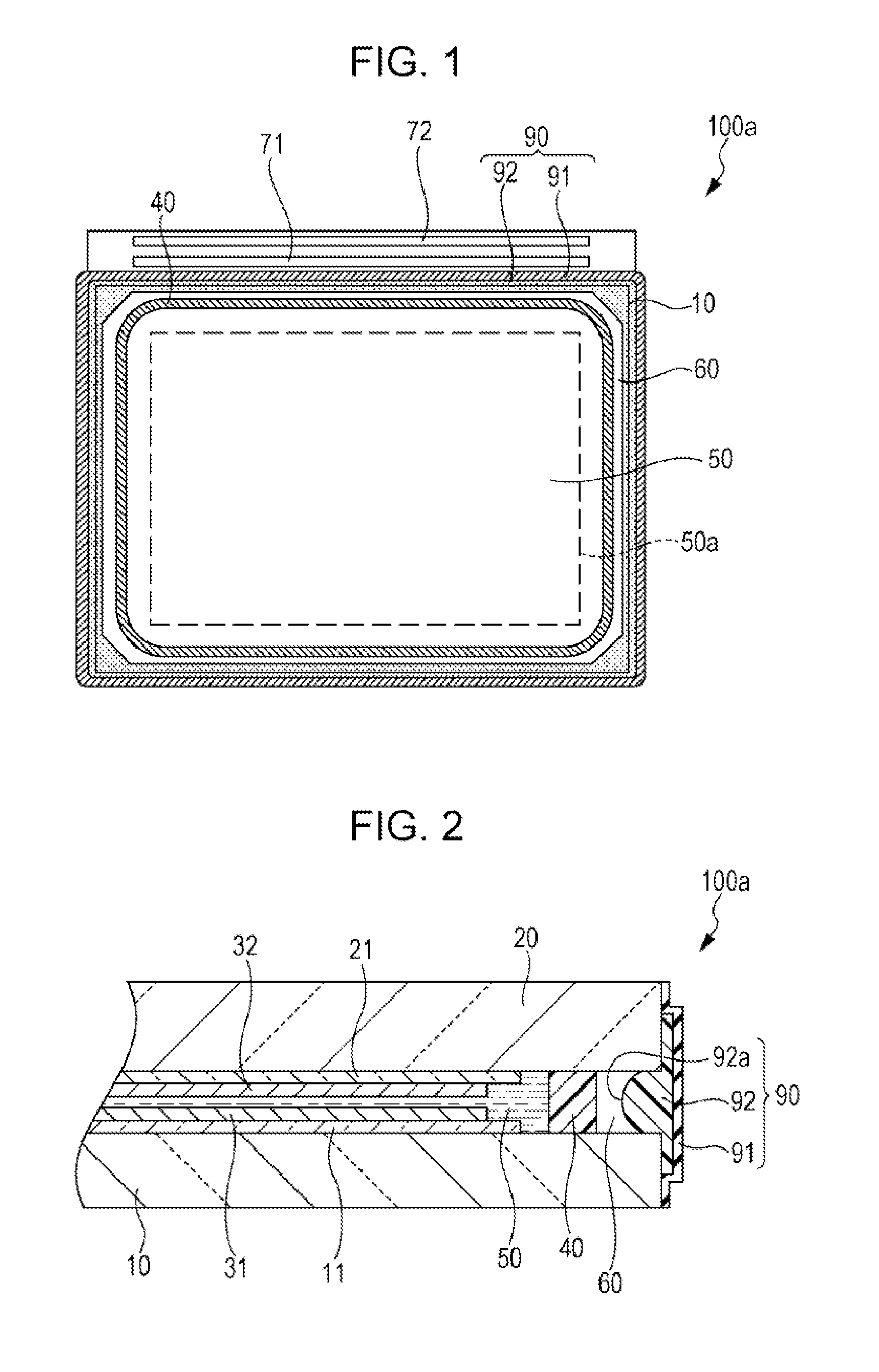

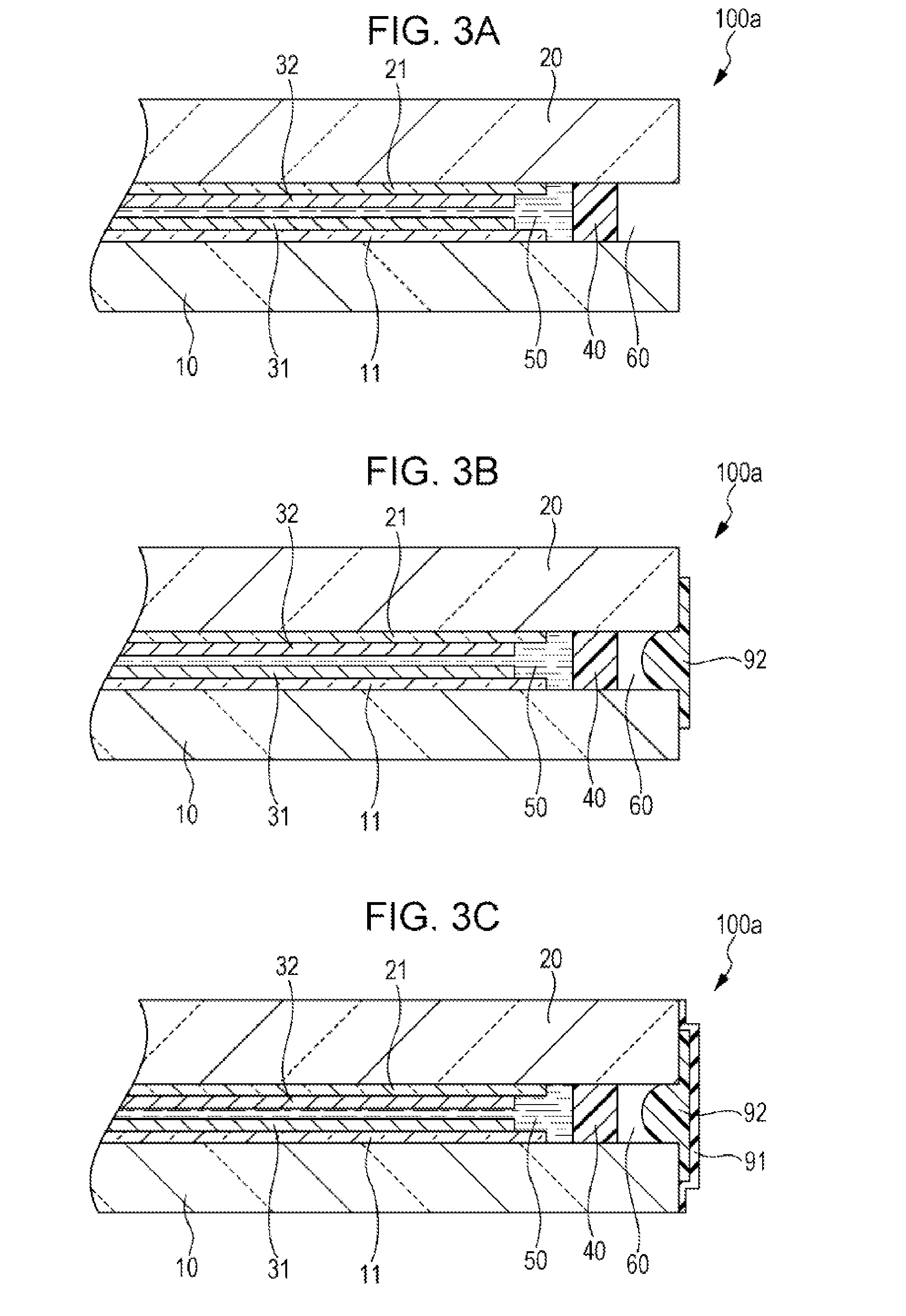

Electro-optical device and electronic apparatus

ActiveUS20140293211A1Suppress bubble generationSuppress misalignmentNon-linear opticsLiquid crystal devicesMechanical engineering

A liquid crystal device includes an element substrate, a counter substrate, a liquid crystal disposed between the substrates, a sealing material disposed in the spacing between the element substrate and the counter substrate and sealing the liquid crystal, a gas barrier layer disposed outside of the sealing material to cover the outside of the spacing and having a portion located in the spacing, and an gap region defined in at least a portion of the space between the sealing material and the gas barrier layer.

Owner:SEIKO EPSON CORP

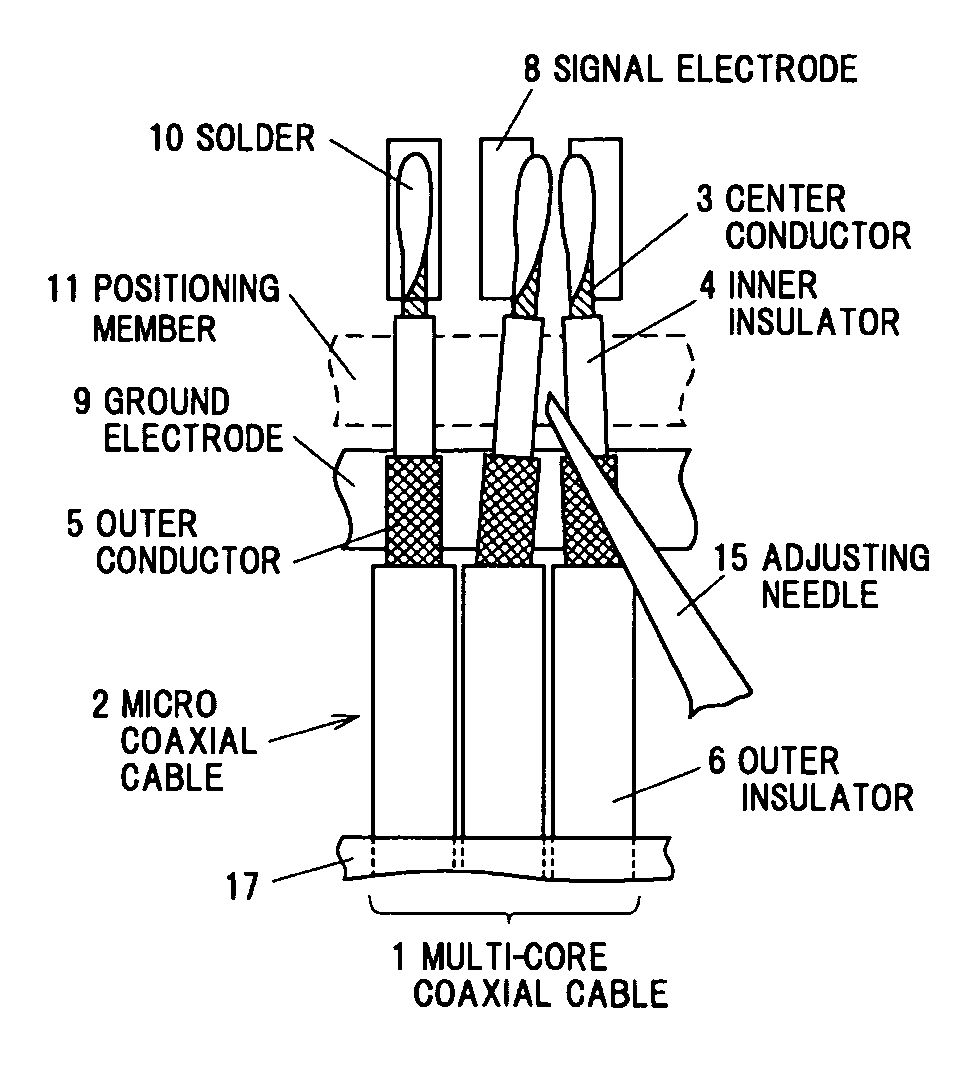

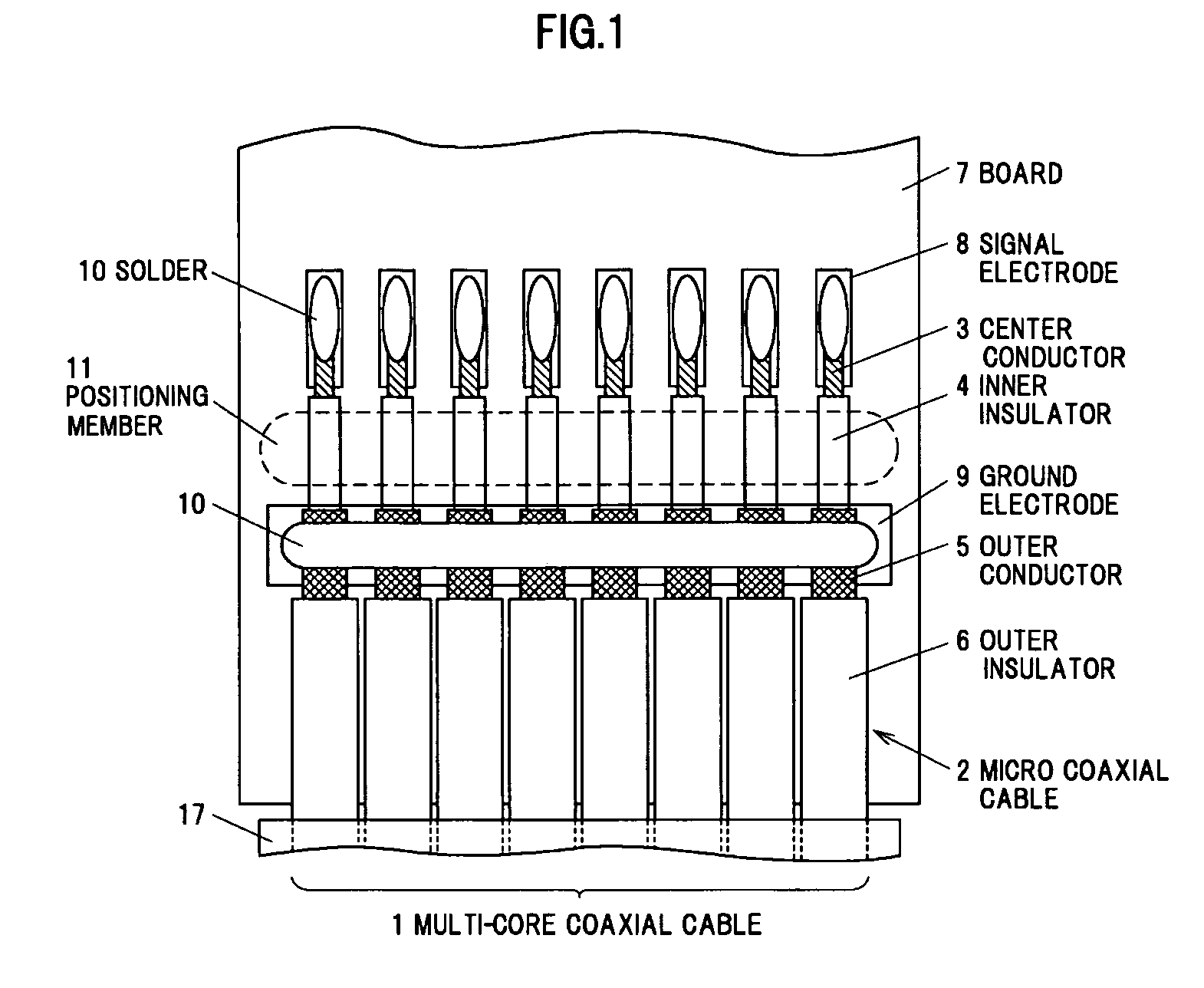

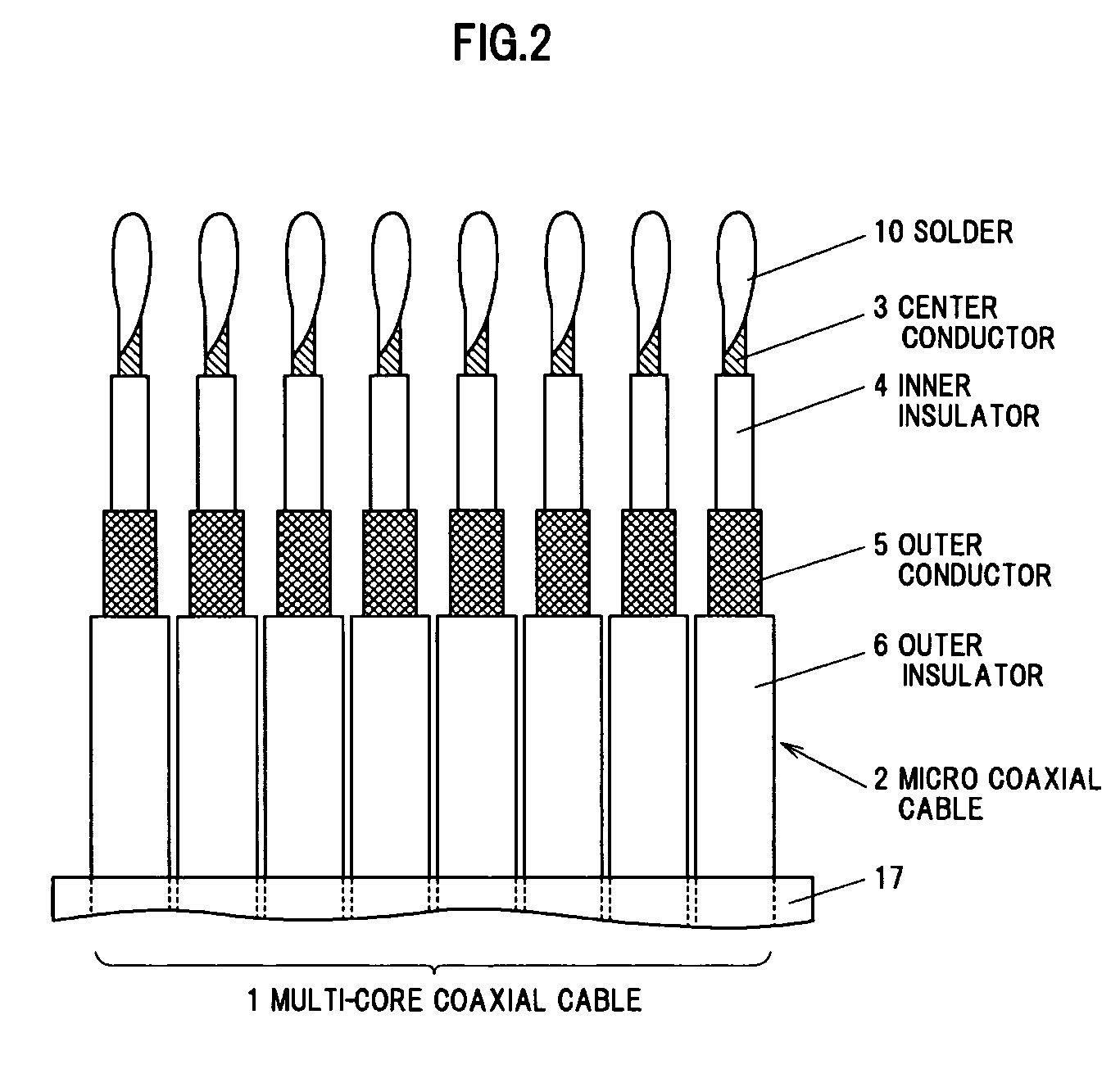

Cable connection structure and cable connection method

InactiveUS20110306235A1Prevent dislocationElectrically conductive connectionsInsulating conductors/cablesElectrical conductorCoaxial cable

A cable connection structure includes a multi-core coaxial cable connected to a board. The multi-core coaxial cable includes a plurality of parallel-arranged coaxial cables each including a center conductor and an inner insulator, an outer conductor and an outer insulator sequentially formed on an outer periphery of the center conductor. The board includes a signal electrode connected to the center conductor and a ground electrode connected to the outer conductor. The cable connection structure further includes a positioning member lying between the signal electrode and the ground electrode for positioning the center conductor while the inner insulator is attached to the positioning member.

Owner:HITACHI METALS LTD

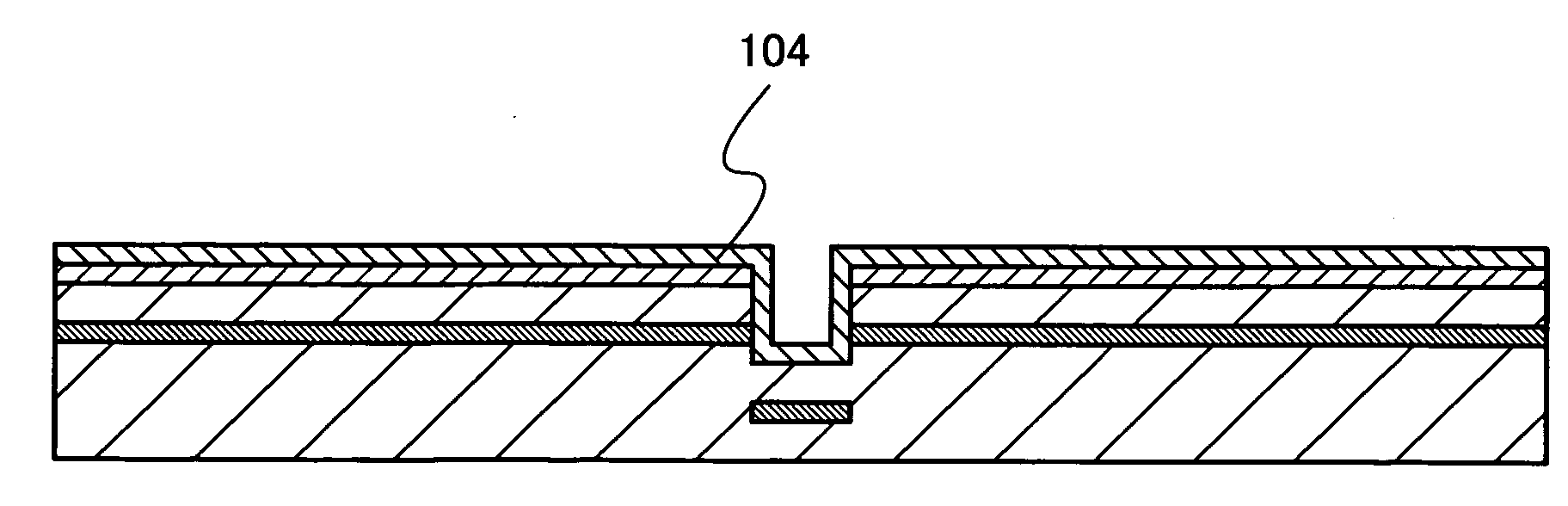

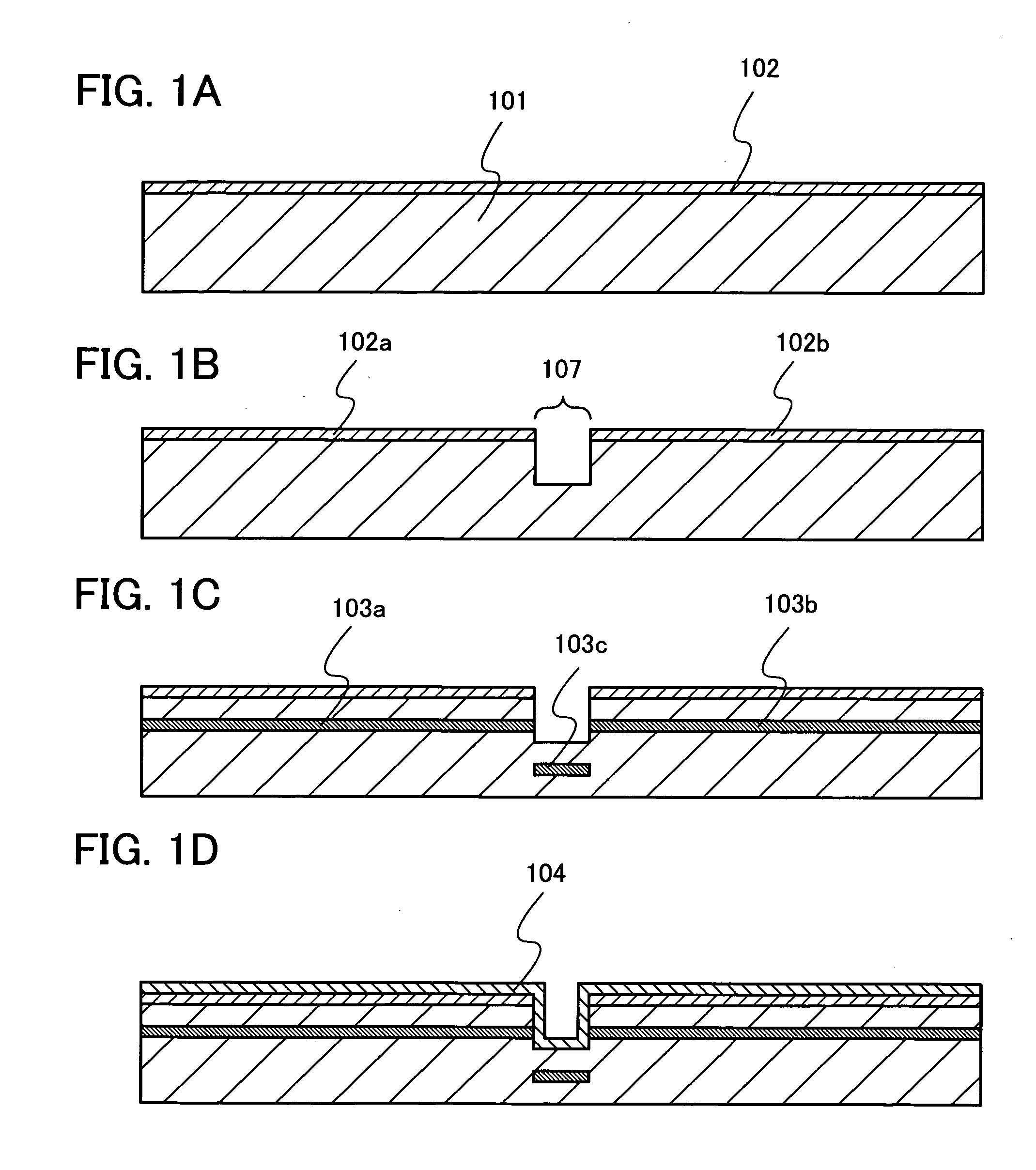

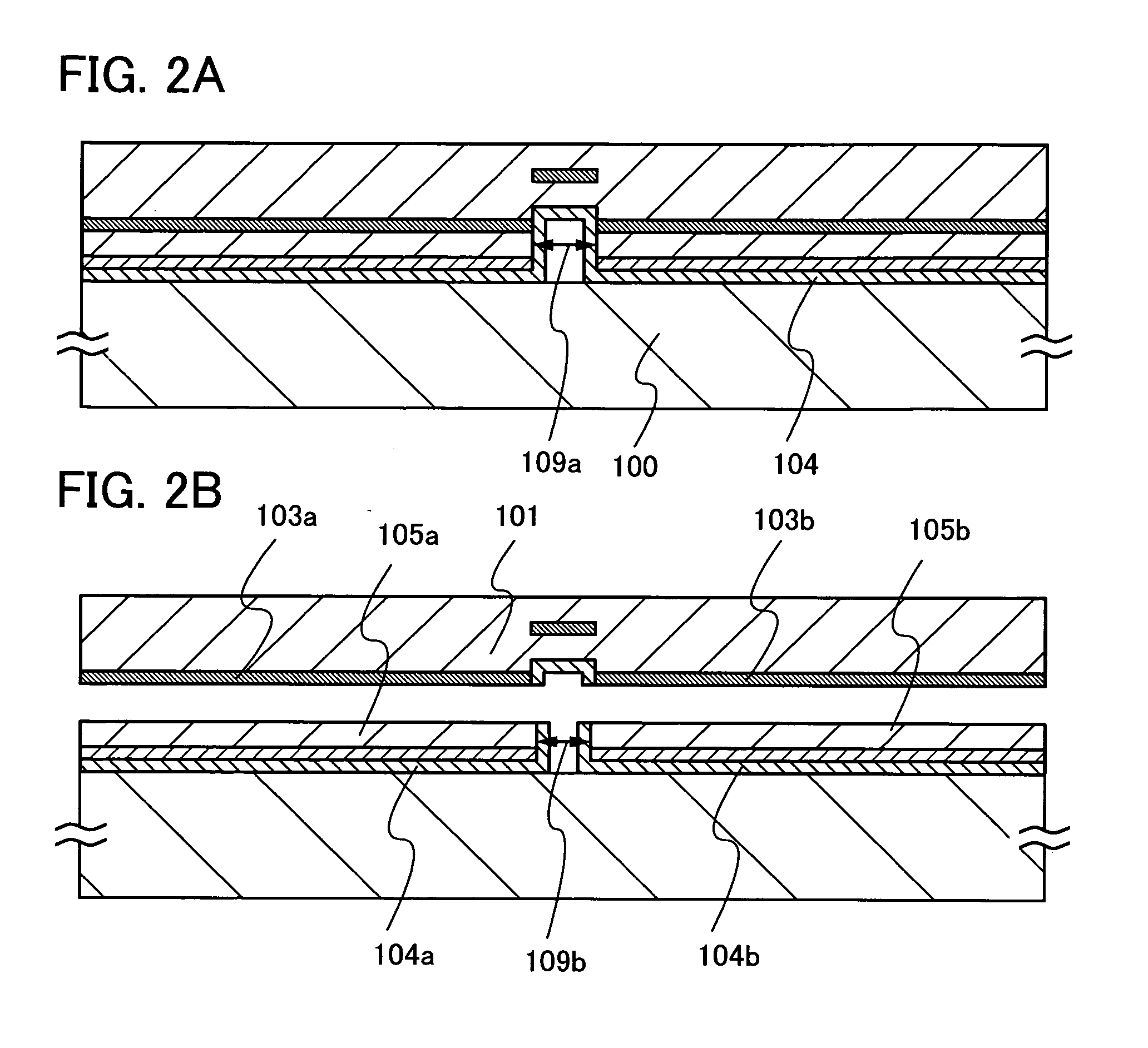

Method for manufacturing semiconductor device

InactiveUS20080280417A1High yieldFilm separationSolid-state devicesSemiconductor/solid-state device manufacturingCrystalline semiconductorHeat treated

An object is to provide a method for manufacturing, with high yield, a semiconductor device having a crystalline semiconductor layer even if a substrate with low upper temperature limit. A groove is formed in a part of a semiconductor substrate to form a semiconductor substrate that has a projecting portion, and a bonding layer is formed to cover the projecting portion. In addition, before the bonding layer is formed, a portion of the semiconductor substrate to be the projecting portion is irradiated with accelerated ions to form a brittle layer. After the bonding layer and the supporting substrate are bonded together, heat treatment for separation of the semiconductor substrate is performed to provide a semiconductor layer over the supporting substrate. The semiconductor layer is selectively etched, and a semiconductor element is formed and a semiconductor device is manufactured.

Owner:SEMICON ENERGY LAB CO LTD