IC pin testing device

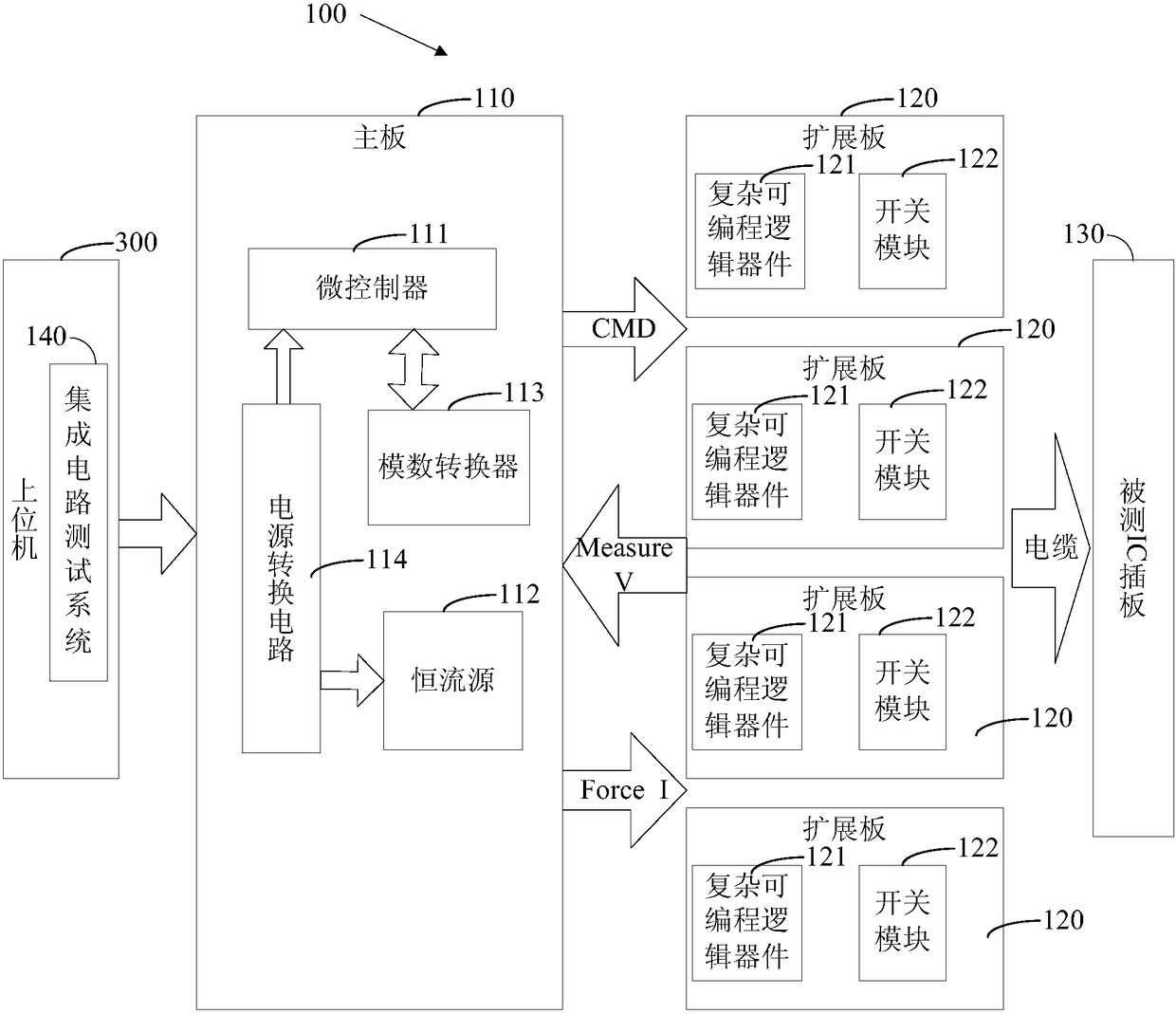

An integrated circuit and test device technology, applied in the field of integrated circuit pin test devices, can solve the problems of high production cost, unfavorable portability, complex internal hardware circuit structure, etc., achieve volume reduction, facilitate portability, and solve the problem of large volume Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0053] In order to make the technical solution of the present invention clearer, the present invention will be further described in detail below in conjunction with the accompanying drawings and specific embodiments.

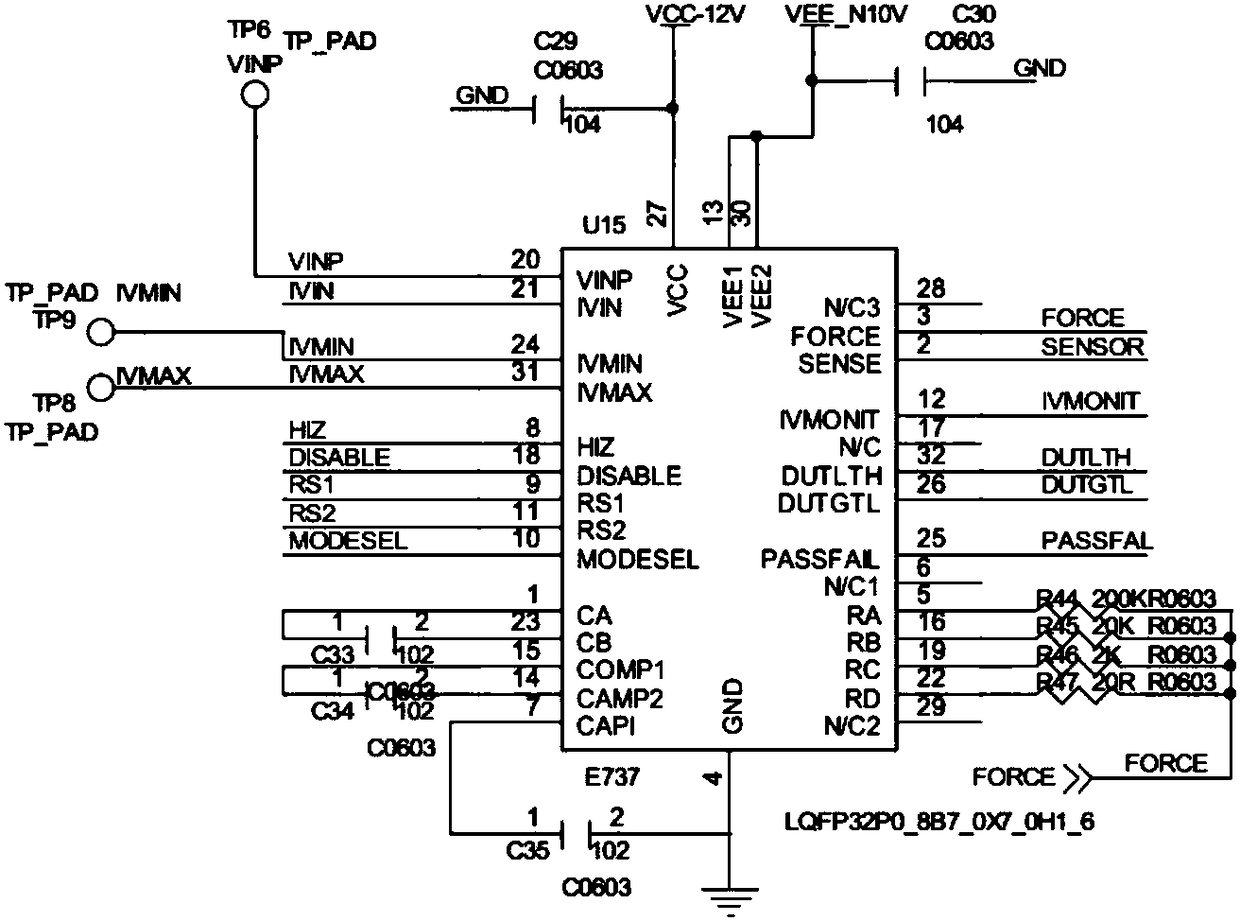

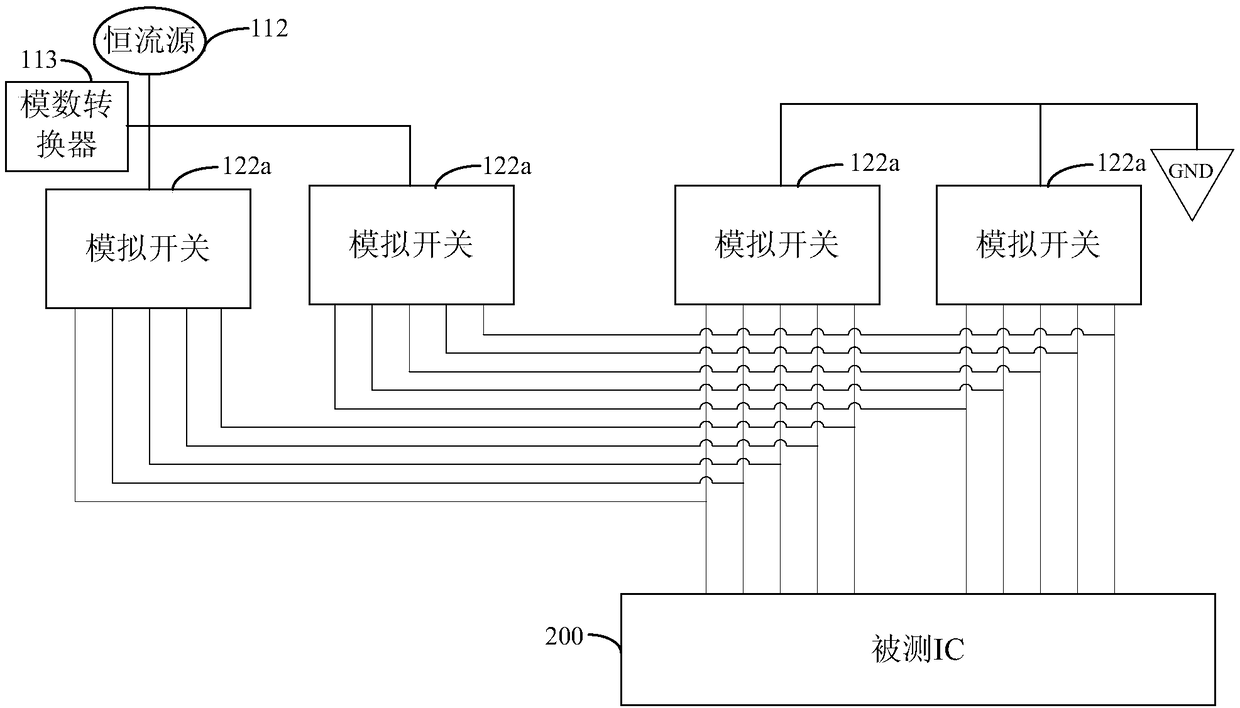

[0054] First of all, it should be noted that the O / S test refers to whether there is an open circuit or short circuit between the tested pin (Pin) and other Pins in verifying a failed IC (Integrated Circuit, integrated circuit). Wherein, in order to protect the pins in the IC, generally there will be a diode between Pin to VDD and Pin to GND in the IC during design. Therefore, by applying a constant current to the diode and testing the voltage drop across the diode, it can be determined whether the pin under test is an open circuit or a short circuit.

[0055] Based on the above test principles, in general, there are three test modes for O / S testing:

[0056] The first one is Pin to GND mode. In this test mode, the pin under test is connected to zero potential...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More