Fin type field effect transistor (FET) and formation method thereof

A fin-type field effect and transistor technology, which is applied in semiconductor devices, semiconductor/solid-state device manufacturing, electrical components, etc., can solve problems that cannot meet the needs of device performance, and achieve the effect of improving carrier mobility and performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

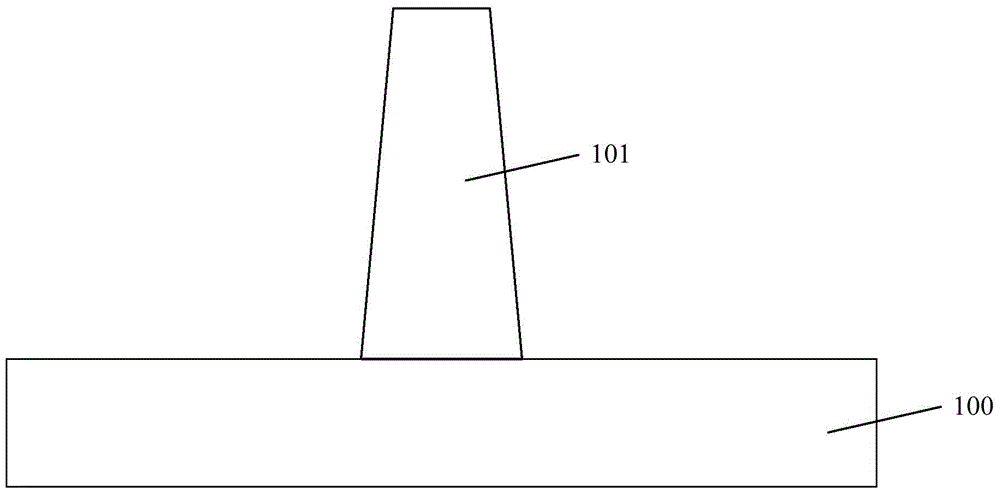

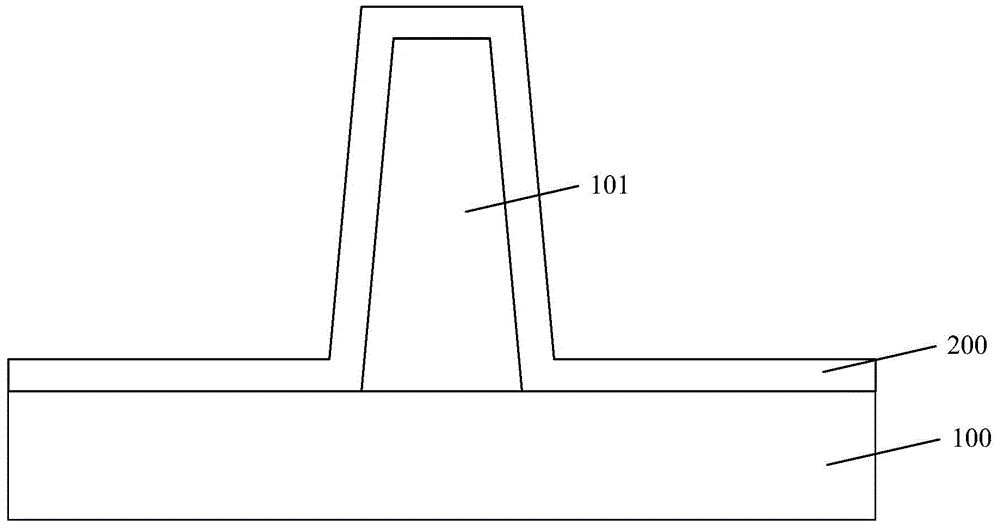

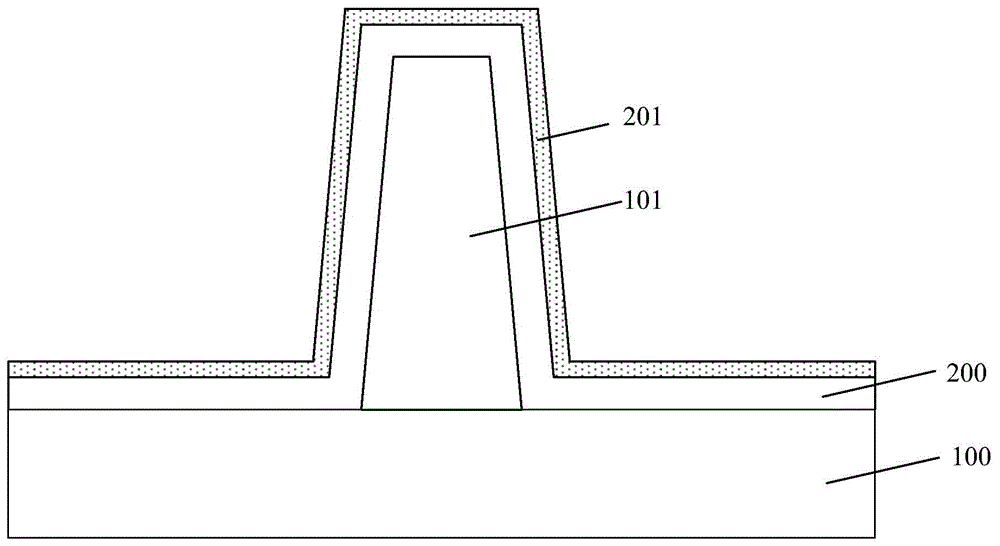

[0031] As mentioned in the background art, the performance of existing fin field effect transistors formed by using graphene as a channel material needs to be further improved.

[0032] The quality of the graphene layer currently formed on the fin is poor, the atomic disorder on the surface of the graphene layer is high, and there are many defects in the graphene layer, resulting in the mobility of the charge carriers in the graphene layer. Decrease, thereby affecting the performance of the formed fin field effect transistor.

[0033] In the embodiment of the present invention, a graphene layer is formed with a carbon-containing semiconductor layer as a base, and the graphene layer is subjected to surface treatment to eliminate defects of the graphene layer, and then a gate is formed on the surface of the graphene layer. The pole structure can improve the quality of the graphene layer and improve the performance of the formed fin field effect transistor.

[0034] In order to ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More