Low-latency fast market decoding device and method based on pipeline architecture

A pipelined, low-latency technology, applied in the information field, can solve the problem of not realizing parallel decoding of FAST market messages, and achieve the effect of simplifying control and update logic, avoiding processing delay, and improving scalability.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

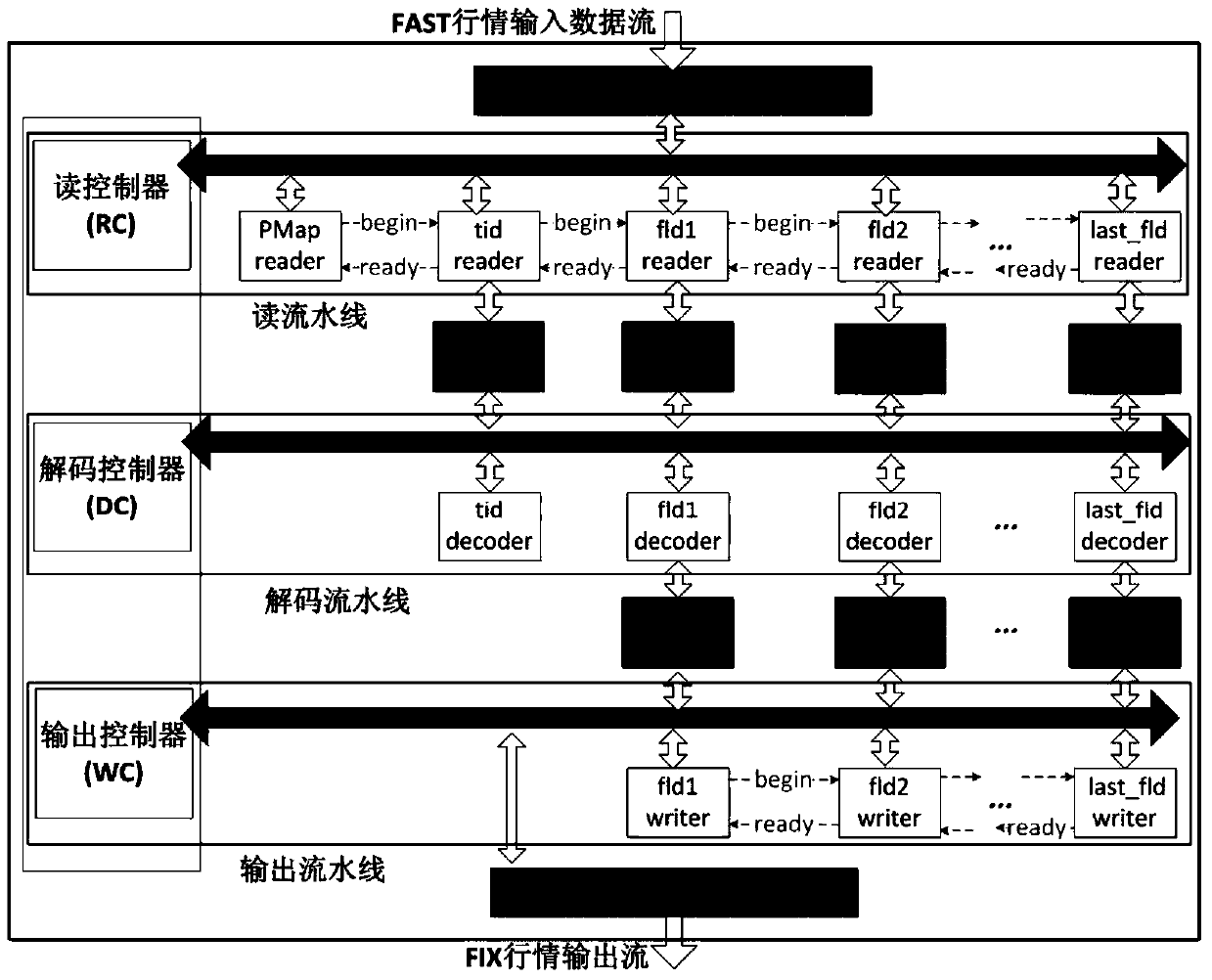

[0031] In order to make the above objects, features and advantages of the present invention more obvious and understandable, the present invention will be further described below through specific embodiments and accompanying drawings.

[0032] In the present invention, special hardware is used to accelerate the decoding of FAST market data, such as FPGA (Field Programmable Gate Array, Field Programmable Gate Array), ASIC (Application Specific Integrated Circuit, application specific integrated circuit) and the like.

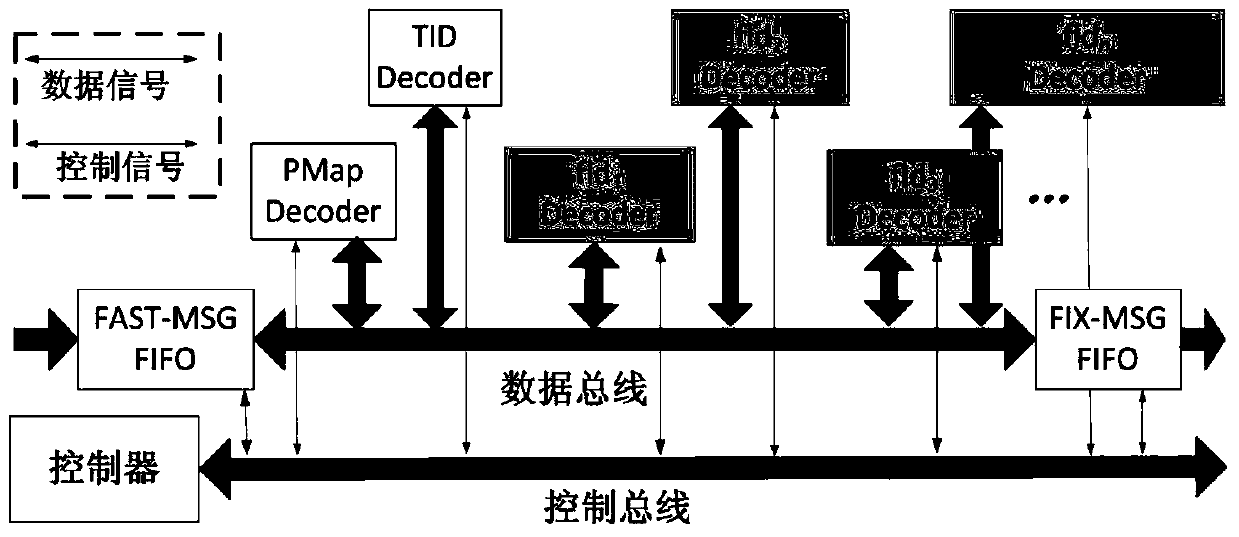

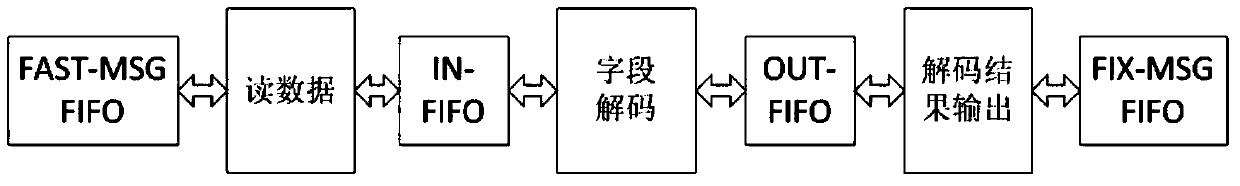

[0033] First of all, the FAST market decoding processor based on the bus architecture is designed. For a specific FAST market template, first connect the decoders (also called decoding operators) of each field defined in the template to the internal bus of the decoding processor. The internal bus is divided into two types: data bus and control bus. Under the control of the decoding controller, the decoding of each field is completed in turn.

[0034] After that...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More