A time-sharing power-on system with multiple power supply partitions for fpga configuration memory array

A memory array, time-sharing power-on technology, applied in the field of integrated circuits, can solve problems such as reducing the reliability of FPGA devices and systems, increasing power supply current, increasing current, etc., to solve the problem of excessive power-on current, improve reliability, Impact prevention effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

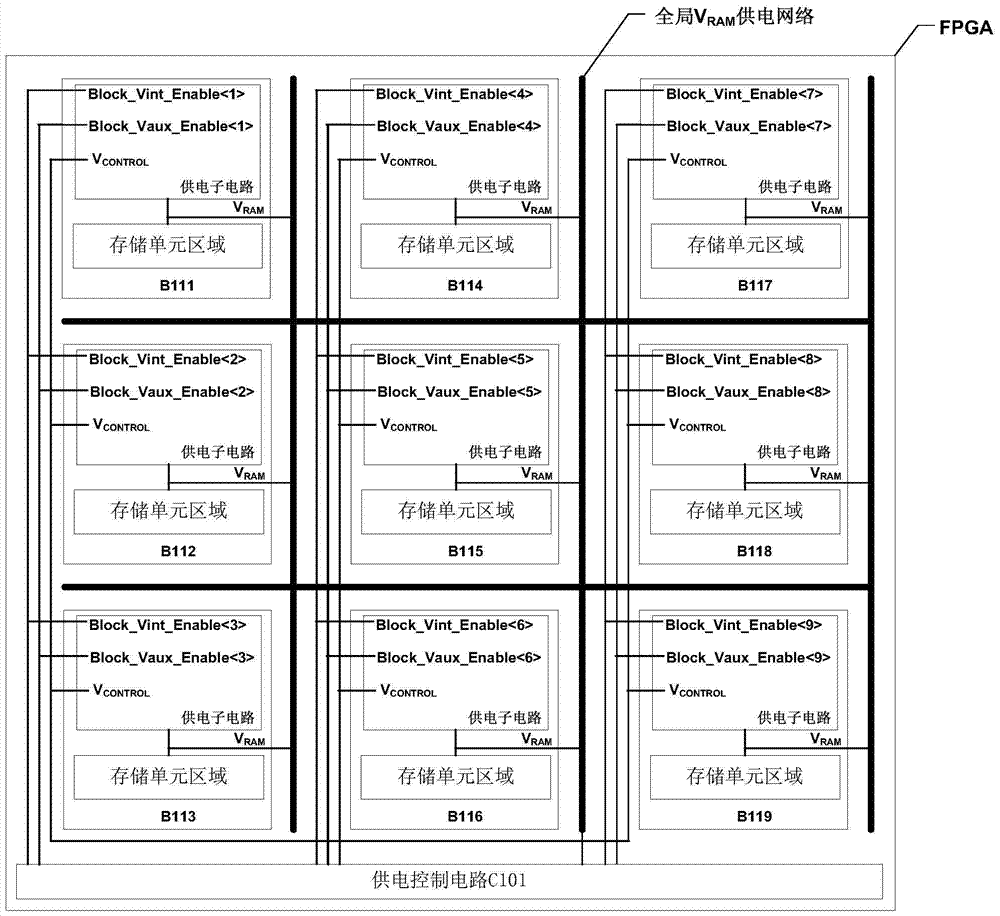

[0072] The present invention will be described by taking the storage unit of the FPGA configuration memory array divided into 9 areas roughly equally according to the boundaries of logic resources as an example.

[0073] Figure 8 It is a block diagram of FPGA, the input and output ports (IOB) are located around the chip, the configurable logic module (CLB) is arranged in an array internally, the block memory (BRAM) is interspersed in the configurable logic module (CLB), and the clock module (of which Including DCM and global clock BUF) are distributed in two corners, the dedicated clock path provides a good clock for configuration logic resources, and also includes configuration logic, configuration interface and power supply control circuit. Figure 8 For illustration, only a small number of Input Output Blocks (IOBs) and Configurable Logic Blocks (CLBs) and Block Memory (BRAM) are shown. The configuration memory array (CSRAM) connected to the various blocks throughou...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More