FPGA-based binary image connected region information fast acquisition system and method

A technology for connected regions and binary images, which is applied in the field of rapid acquisition systems for the information of connected regions of binary images, can solve the problems of unsuitability for parallelization and low efficiency, and achieve the effect of real-time acquisition.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

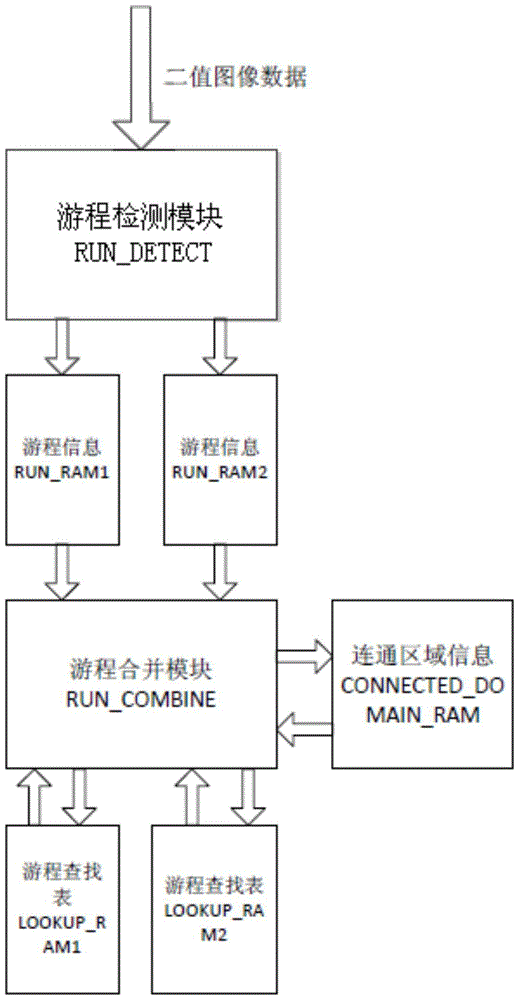

[0037] The technical scheme that the present invention implements is as follows:

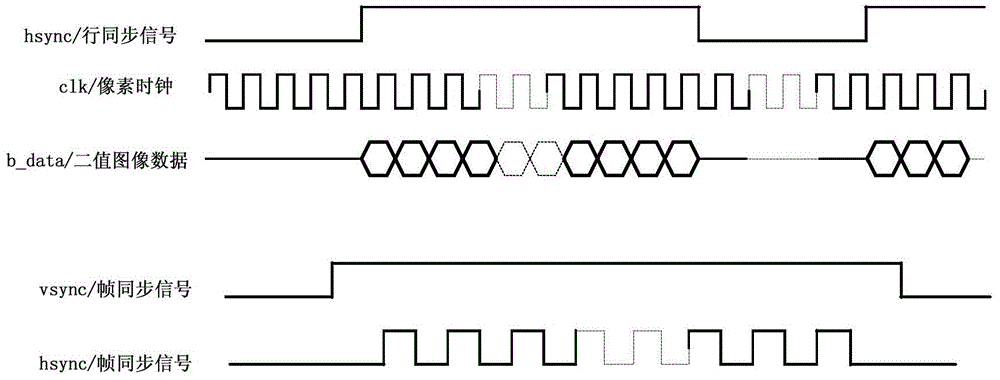

[0038] 1. The image data adopts the common output format of the image sensor, that is, the frame synchronization signal, the line synchronization signal, the binary image data and the pixel synchronization clock are used as the image input signal.

[0039] 2. Effective period of the first line: Detect the run-length information of the first line of images, and store the run-length information into the on-chip storage space.

[0040]3. The valid period of the second line: Detect the run-length information of the second line of images, and store the information in the on-chip storage space; convert the run-length information of the first line into the connected area information and write it into the corresponding connected area information storage space; A run-length look-up table of one row, the run-length look-up table records the run-length information and the merging relationship between the r...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com