Method for assignment of multiple power supply pins of voltage island

A distribution method and technology of voltage island, applied in electrical digital data processing, CAD circuit design, special data processing applications, etc., can solve the circuit failure of circuit macro-modules, the voltage drop does not meet the design constraints, and affects the voltage drop of power supply network nodes, etc. problem, to achieve the effect of optimizing the voltage drop and reducing the design cost

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0030] The present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments.

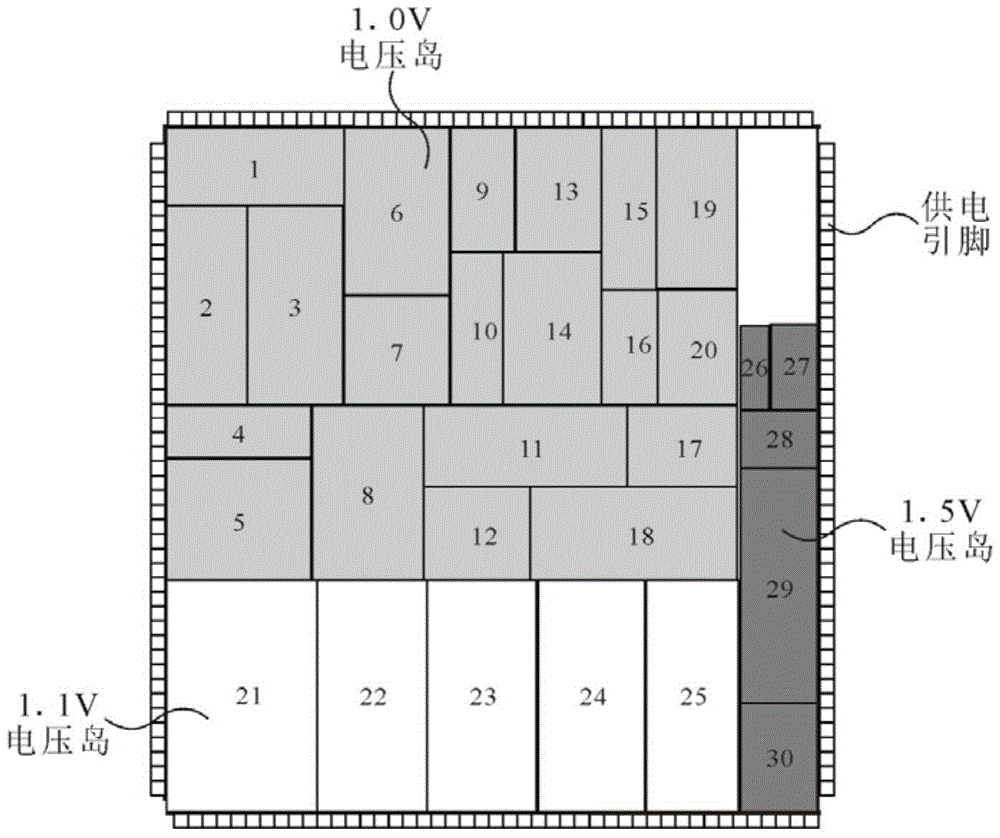

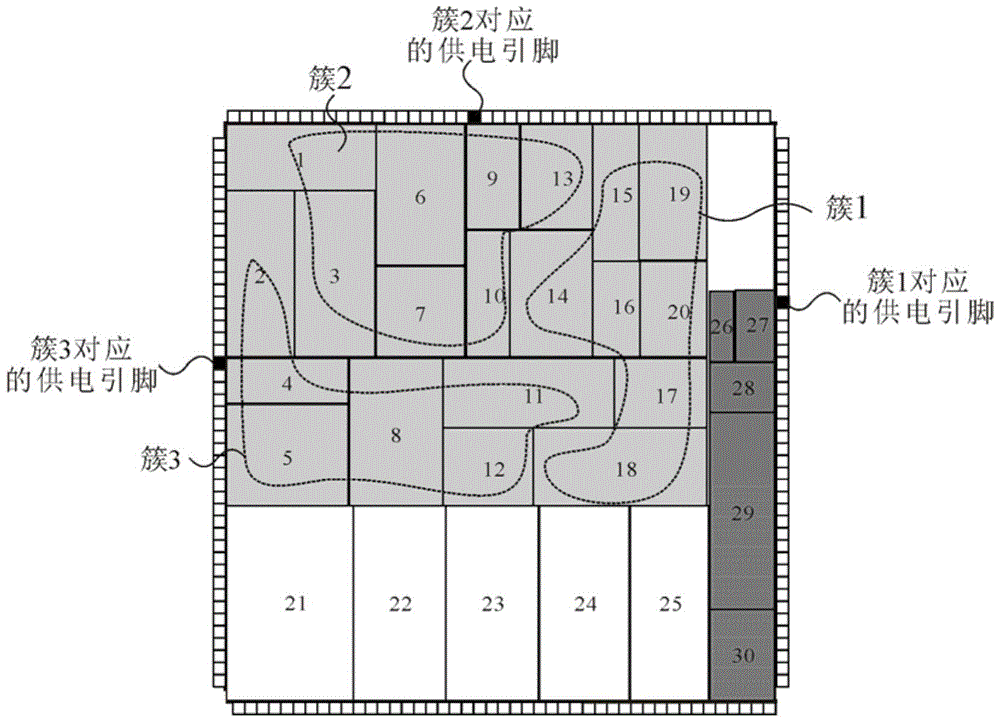

[0031] Taking a chip containing three voltage islands as an example, its layout representation is shown in figure 1 , figure 1 That is, a schematic layout diagram of a circuit macromodule including three voltage islands, which contains 30 circuit macromodules, namely b 1 , b 2 , b 3 ,...,b 30 , the multi-supply pin allocation method of its voltage island, including the following steps:

[0032] Step ①: Define a voltage island as an area composed of circuit macromodules operating at the same operating voltage and occupying a continuous two-dimensional physical space. The chip is composed of several voltage islands. figure 1 Contains three voltage islands, where the circuit macroblock b 1 ~b 20 A voltage island with a working voltage of 1.0V is formed, and the circuit macromodule b 21~b 25 A voltage island with a working voltage of 1.1V...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More