Thin film transistor and preparation method thereof, array substrate and display device

A technology of thin-film transistors and array substrates, applied in the display field, can solve problems such as impacting, reducing the response speed of the display, and increasing the load of the display

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

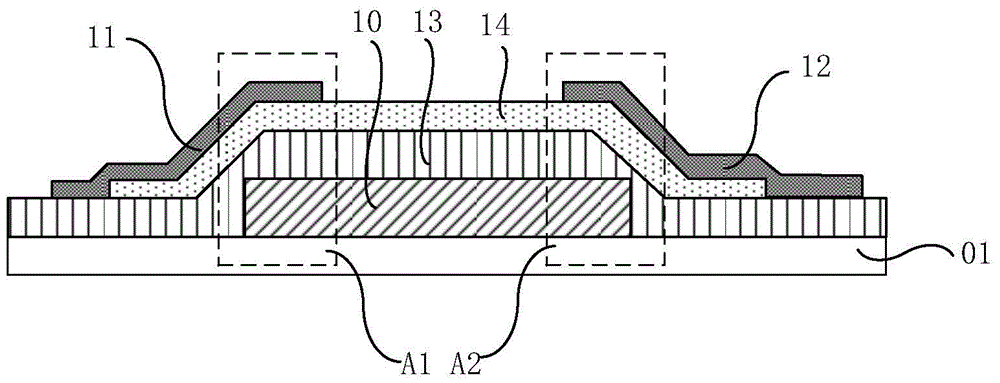

[0043] In this example, if Figure 4a The source 11 of the shown TFT includes a U-shaped first working portion 110 . The drain 12 includes a strip-shaped second working portion 120 .

[0044] In this case, the first opening part 100 is a U-shaped through hole, and a U-shaped through hole is provided on the above-mentioned one U-shaped first working part 110 along the outline of the first working part 110 . In this way, only one U-shaped through hole needs to be prepared on the first working portion 110 to reduce the overlapping area between the source electrode 11 and the gate 10 without preparing multiple through holes. In addition, the above-mentioned U-shaped through hole is provided along the outline of the first working portion 110 , so that the overlapping area between the source electrode 11 and the gate electrode 10 can be minimized through one patterning process.

[0045] Preferably, the distance H1 from the inner side C1 of the U-shaped first working portion 110 to...

Embodiment 2

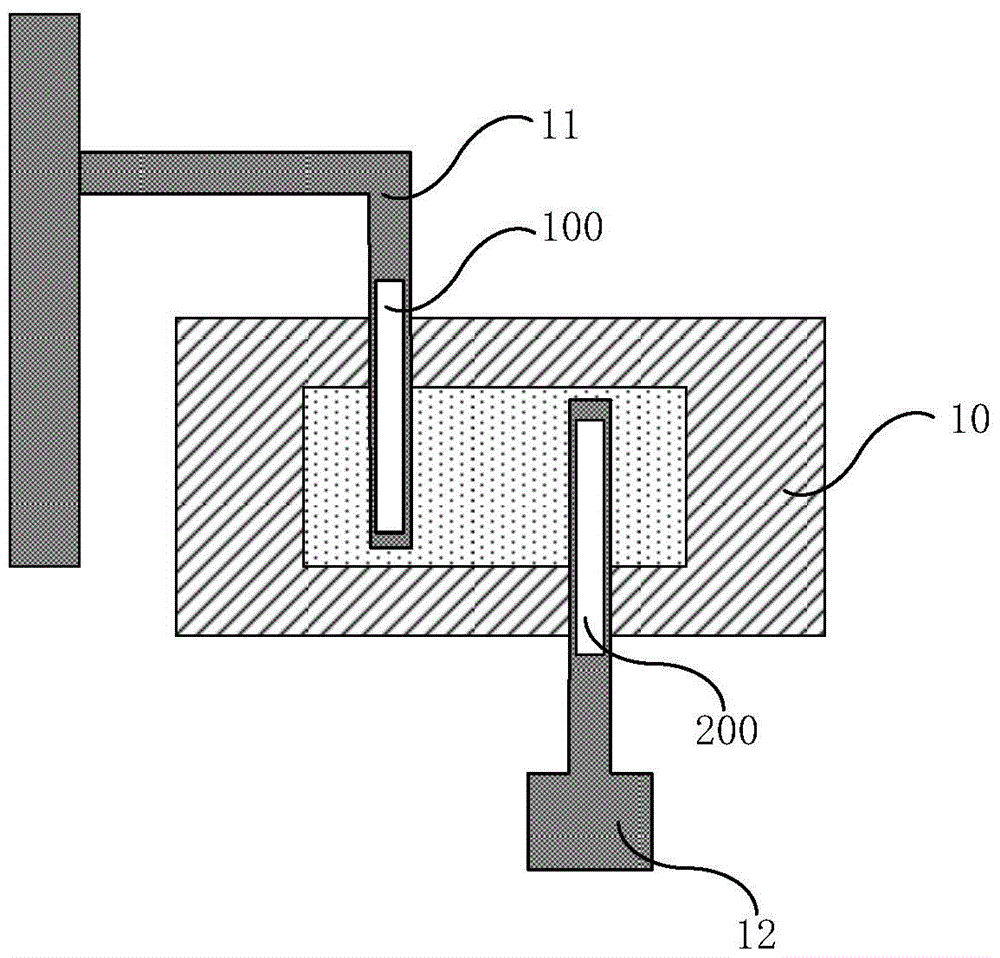

[0050] In this embodiment, the source 11 of the TFT is the same as the first embodiment, including a U-shaped first working portion 110 . Drain 12 as Figure 4b Shown includes a U-shaped second working portion 120 .

[0051] In this case, the setting method of the first opening 100 is the same as that of the first embodiment, and will not be repeated here.

[0052] The second opening 200 is a U-shaped through hole, and a U-shaped through hole is provided on the second working part 120 along the outline of the second working part 120 . In this way, only one U-shaped through hole needs to be prepared on the second working portion 120 to reduce the overlapping area between the drain 12 and the gate 10 without preparing multiple through holes. In addition, the above-mentioned U-shaped through holes are provided along the outline of the second working portion 120 , which can minimize the overlapping area between the drain 12 and the gate 10 through one patterning process.

[005...

Embodiment 3

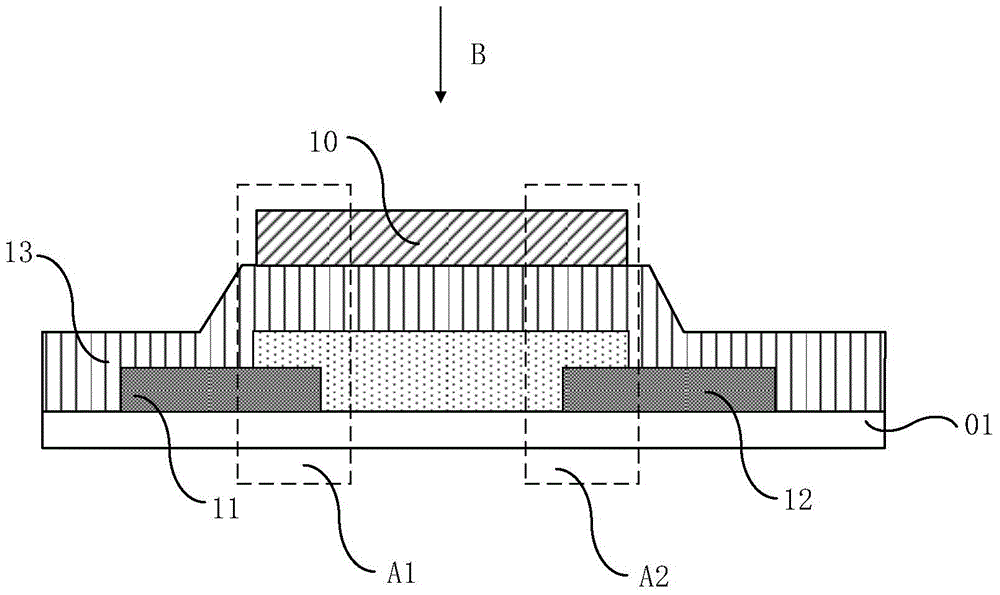

[0055] In this example, if Figure 4c As shown, the source 11 of the TFT includes two U-shaped first working portions 110 . The drain 12 includes two strip-shaped second working portions 120 .

[0056] In this case, the first opening 100 is a U-shaped through hole, and each U-shaped first working part 110 in the source 11 is provided with a U-shaped through hole along the outline of the first working part 110 . In this way, it is only necessary to prepare a U-shaped through hole on each first working part 110 to reduce the overlapping area between the source electrode 11 and the gate 10, without preparing a U-shaped through hole on each first working part 110. Multiple vias. In addition, the above-mentioned U-shaped through hole is provided along the outline of the first working portion 110 , so that the overlapping area between the source electrode 11 and the gate electrode 10 can be minimized through one patterning process.

[0057] Preferably, the distance H1 from the in...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More