Formation method of semiconductor structure

A technology of semiconductor and plasma, which is applied in the manufacture of semiconductor/solid-state devices, electrical components, circuits, etc., can solve the problems of poor quality of conductive materials, affecting the electrical connection performance of semiconductor devices, rough side wall surface, etc., and achieve the improvement of interface quality, Improvement of metal layer interconnection performance and quality improvement effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

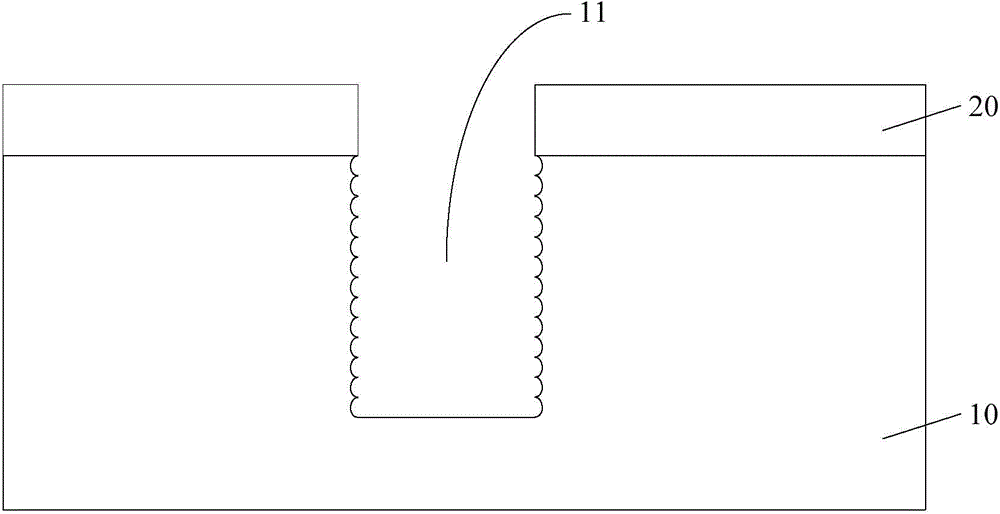

[0030] As mentioned in the background art, the surface of the side wall of the through hole formed in the prior art is relatively rough, and there are protrusions and depressions. Please refer to figure 1 After the semiconductor substrate 10 is etched using a dry etching process with the mask layer 20 as a mask, a through hole 11 is formed in the semiconductor substrate 10 , and the sidewall of the through hole 11 is rough. The rough sidewall of the through hole 11 will affect the quality of the metal layer subsequently formed in the through hole 11 , resulting in uneven width of the metal layer, thereby affecting the electrical connection performance, such as increased RC delay.

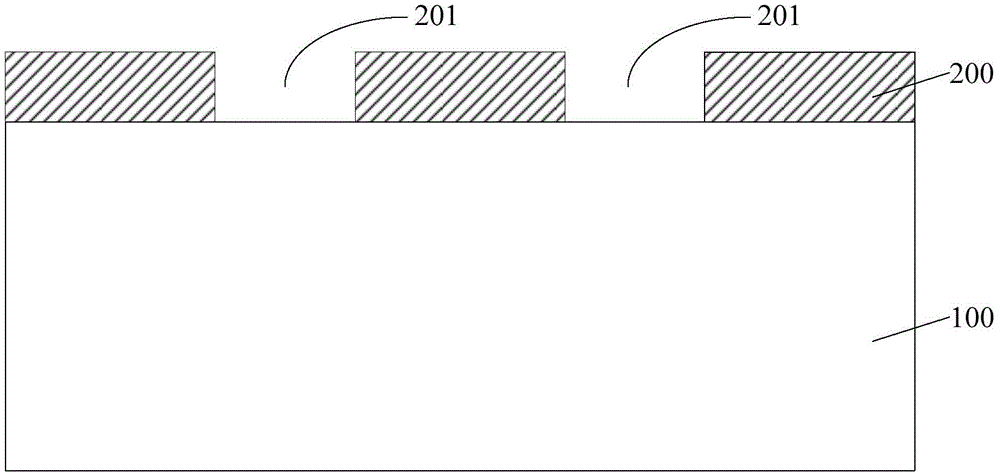

[0031] In an embodiment of the present invention, after the first through hole is formed in the semiconductor substrate, after the sidewall of the first through hole is oxidized to form an oxide layer, the oxide layer is removed to form the second through hole, so that the second through hole The s...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More